# UNIVERSITE DE LIMOGES

# ECOLE DOCTORALE Science et Ingénierie pour l'information FACULTE DES SCIENCES ET TECHNIQUES

Année : 2011 Thèse N°[90-2011]

# **THESE**

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITE DE LIMOGES

Discipline: "Electronique des Hautes Fréquences, Photonique et Systèmes"

Présentée et soutenue par

# Michel AL KHOURY

Le 19 Décembre 2011

# Intégration de filtres Radio Fréquences en technologie intégrée Silicium

Thèse dirigée par Bernard JARRY, Bruno BARELAUD, Julien LINTIGNAT

### **JURY**:

| Serge VERDEYME                    | Professeur à l'Université de Limoges-XLIM                                                          | Président                |

|-----------------------------------|----------------------------------------------------------------------------------------------------|--------------------------|

| Philippe FERRARI<br>Gérard TANNE  | Professeur à l'Université de Grenoble - IMEP LAHC<br>Professeur à l'Université de Brest- Lab STICC | Rapporteur<br>Rapporteur |

| Corinne BERLAND<br>Patrice GAMAND | Professeur HDR à ESIEE et LAMIPS- Caen<br>Directeur du Centre d'Innovations RF                     | Examinateur              |

|                                   | NXP Semiconductors, Caen                                                                           | Examinateur              |

| Ali LOUZIR                        | Ingénieur à Technicolor R&D, Cesson sévigné                                                        | Examinateur              |

| Bernard JARRY                     | Professeur à l'Université de Limoges-XLIM                                                          | Examinateur              |

| Bruno BARELAUD                    | Professeur à l'Université de Limoges-XLIM                                                          | Examinateur              |

| Julien LINTIGNAT                  | Maître de conférence à l'Université de Limoges-XLIM                                                | Invité                   |

# Remerciements

Mes premiers remerciements iront à mes directeurs de thèse, Bernard JARRY, Bruno BARELAUD et Julien LINTIGNAT qui ont accepté d'encadrer cette thèse et qui m'ont témoigné leur soutien et confiance.

J'exprime ma sincère reconnaissance au Professeur Serge VERDEYME d'avoir accepté de présider ce jury de thèse.

Je remercie Monsieur le Professeur Philippe FERRARI du laboratoire IMEP LAHC de l'université de Grenoble, et Monsieur le Professeur Gérard TANNE du laboratoire Lab STICC de l'université de Brest pour avoir accepté de juger ce travail.

J'exprime ma gratitude à Monsieur Patrice GAMANT directeur du Centre d'Innovations RF, NXP Semiconducteur CAEN, Madame le professeur HDR Corinne BERLAND du laboratoire ESIEE et LAMIPS et à Monsieur Ali LOUZIR, Ingénieur hyperfréquence à Technicolor, d'avoir acceptés d'examiner ce travail.

Je tiens à remercier tous les collègues de l'XLIM qui savent bien rendre agréable le cadre de travail. Je pense plus particulièrement à mes collègues de bureau : Cédric, Raafat et Ragheb ainsi qu'à mes voisins : François et Ludovic.

J'adresse un merci spécial et particulier à mon cousin Georges ZAKKA EL NASHEF pour son infini soutien pendant la période de la rédaction et tout au long de cette thèse. Encore merci à Georges, Elie et Nour pour les soirées inoubliables, les moments agréables.

Une sincère gratitude à mes parents et à toute ma famille qui m'ont toujours encouragé et soutenu.

A mes parents,

A mes amis

# **SOMMAIRE**

| Introduction générale5                                                          |

|---------------------------------------------------------------------------------|

| Chapitre I : Etat de l'art sur le filtrage actif en technologie silicium 9      |

| I. Introduction                                                                 |

| II. Rôle des filtres RF dans les chaînes de télécommunication                   |

| III. Etat de l'art des filtres actifs                                           |

| III.1. Introduction                                                             |

| III.2. Classification des filtres actifs                                        |

| III.2.1. Les filtres actifs analogiques continus (Gm-C)                         |

| III.2.2. Les filtres actifs récursifs et transversaux                           |

| III.2.3. Les filtres actifs à inductance active                                 |

| III.2.3.1. Exemples de circuits d'inductance active                             |

| III.2.4. Les filtres actifs LC à facteur de qualité compensé (Q-enhanced LC) 22 |

| III.2.4.1. Architectures de résistances négatives                               |

| III.2.4.2. Filtres actifs à résistance négative                                 |

| IV. Conclusion                                                                  |

| V. Références Bibliographiques                                                  |

| Chapitre II : Inductance compensée à trois inductances couplées et              |

| modélisation du transformateur en technologies CMOS 65 nm et BiCMOS             |

| 0,25 μm45                                                                       |

| I. Introduction47                                                               |

| II. Conception de l'inductance compensée                                        |

| II.1. Principe de fonctionnement                                                |

| II.1.1. Introduction                                                            |

| II.1.2. Concept du couplage entre deux inductances                              |

| II.1.3. Inductance compensée à trois inductances couplées                       |

| II.1.3.1. Inductance compensée utilisant un transistor NMOS51                   |

| II.1.3.2. Inductance compensée avec un transistor bipolaire                     |

| II.1.3.3. Calcul des paramètres $\alpha$ et $\beta$                             | 55     |

|---------------------------------------------------------------------------------|--------|

| II.2. Layout du transformateur                                                  | 57     |

| II.2.1. Paramètres géométriques                                                 | 57     |

| II.2.2. Sens des enroulements et dessin du transformateur                       | 59     |

| II.2.3. Présentation des deux technologies utilisées dans cette thèse et layou  | it des |

| transformateurs                                                                 | 62     |

| II.2.3.1. La technologie CMOS 65 nm                                             | 62     |

| II.2.3.2. La technologie BiCMOS 0,25 μm                                         | 62     |

| II.2.3.3. Exemple de layout du transformateur en technologie CMOS 65nm          | m 63   |

| II.2.3.4. Exemple de layout du transformateur en technologie BiCMOS             | 0,25   |

| μm                                                                              | 64     |

| III. Modélisation du transformateur                                             | 65     |

| III.1. Problématique                                                            | 65     |

| III.2. Méthodologie de modélisation                                             | 65     |

| III.2.1. Modèle électrique du transformateur en technologies CMOS 65 n          | ım et  |

| BiCMOS 0,25 μm                                                                  | 71     |

| IV. Inductance compensée                                                        | 75     |

| IV.1. Inductance compensée à 2 GHz en technologie CMOS 65 nm                    | 75     |

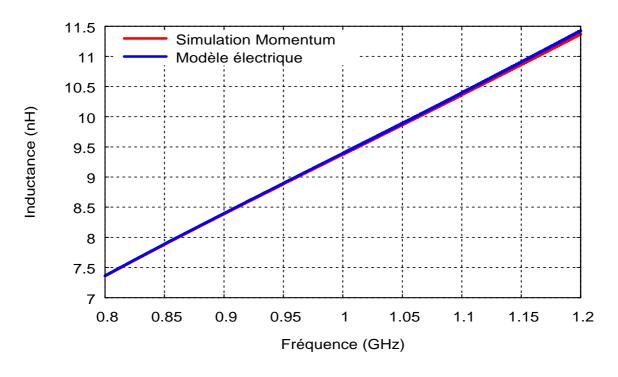

| IV.1.1. Validation du modèle électrique du transformateur                       | 79     |

| IV.2. Inductance compensée à 1GHz en technologie BiCMOS 0,25 μm                 | 80     |

| IV.2.1. Validation du modèle électrique du transformateur                       | 82     |

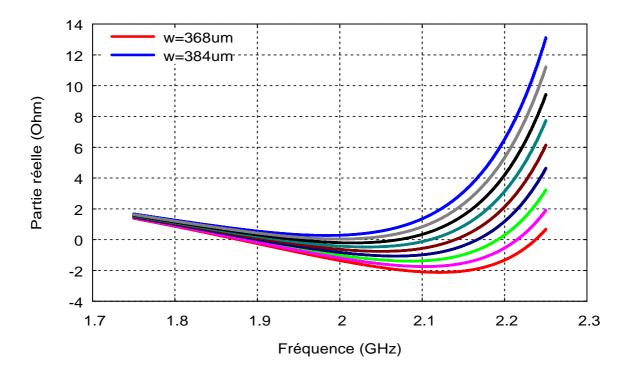

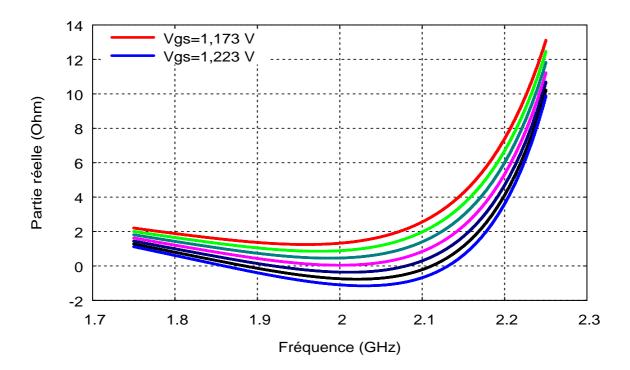

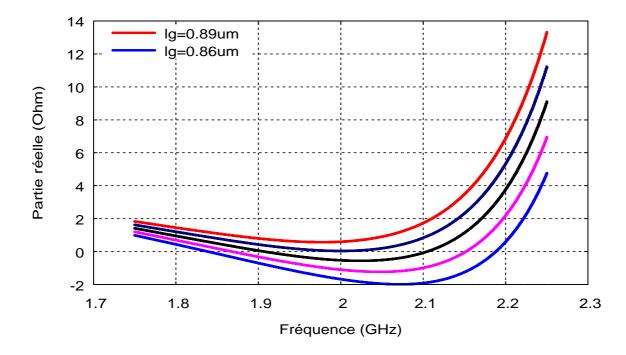

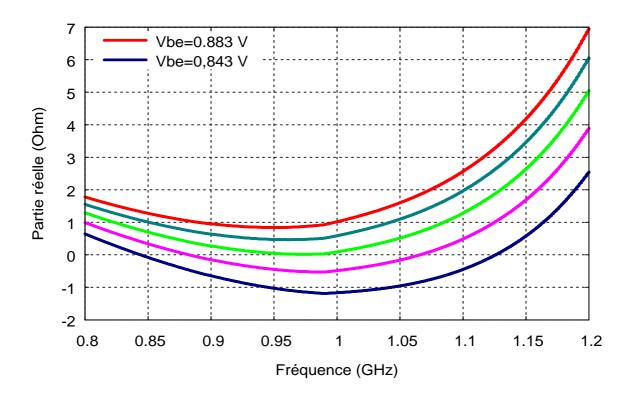

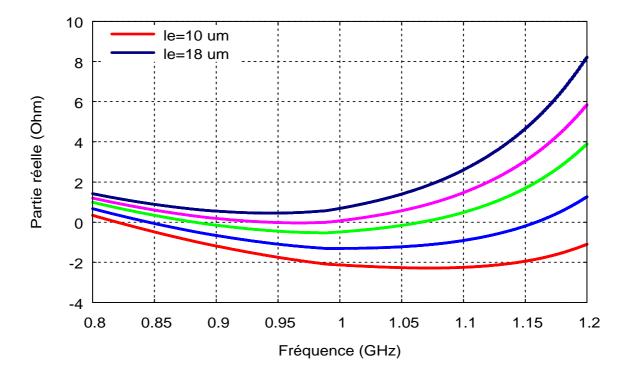

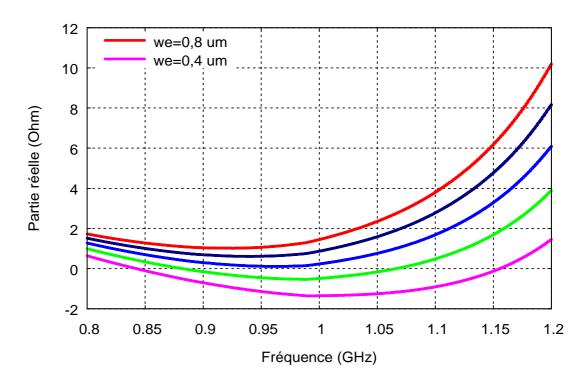

| IV.3. Effets des paramètres géométriques du transistor de compensation          | ı sur  |

| l'inductance compensée                                                          | 83     |

| IV.3.1. Cas du transistor NMOS                                                  | 83     |

| IV.3.2. Cas du transistor bipolaire                                             | 85     |

| V. Différentes topologies de résonateurs utilisant l'inductance compensée : Ana | alyse  |

| spécifique liée à la nature simple accès de l'inductance.                       | 87     |

| VI. Conclusion                                                                  | 92     |

| VII Références hibliographiques                                                 | 93     |

| Chapitre III: Conception d'un LNA filtrant pour une ch                      | aîne de    |

|-----------------------------------------------------------------------------|------------|

| réception intégrée à 942,5 MHz                                              | 97         |

| I. Introduction                                                             | 99         |

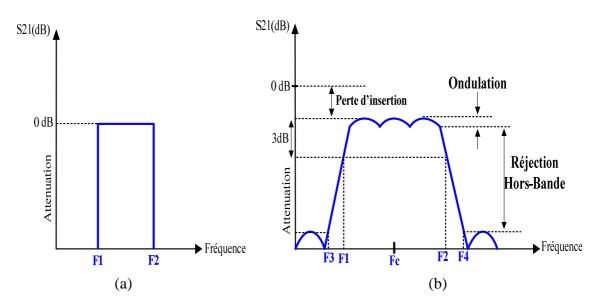

| II. Filtres à résonateurs LC                                                | 99         |

| II.1. Quelques définitions                                                  | 99         |

| II.2. Analyse détaillée de la topologie optimale de filtrage définie dans l | e chapitre |

| II                                                                          | 102        |

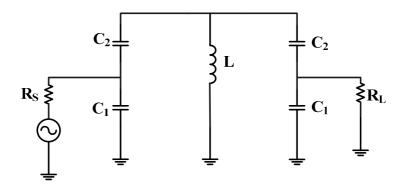

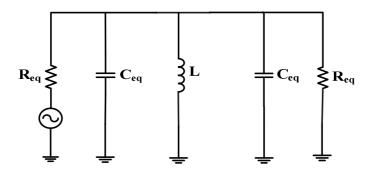

| II.2.1. Principe de transformation d'impédance et filtre à un pôle          | 102        |

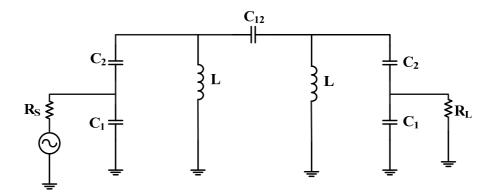

| II.2.2. Filtre à 2 pôles                                                    | 104        |

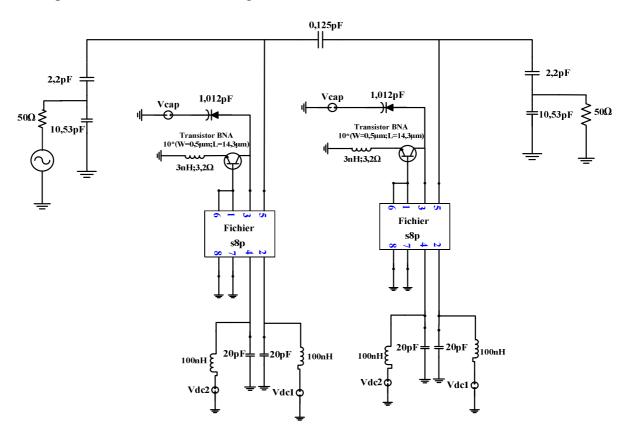

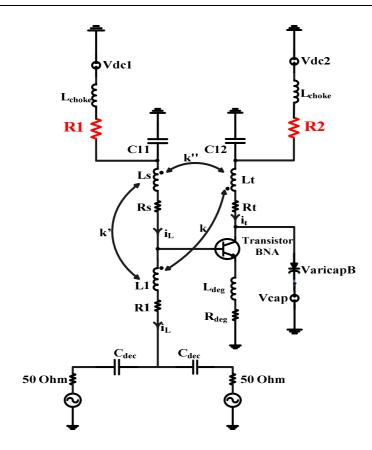

| III. Conception du circuit LNA-Filtrant                                     | 105        |

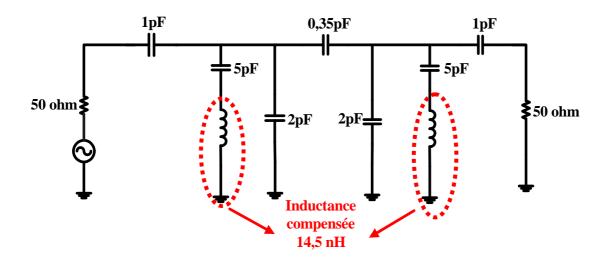

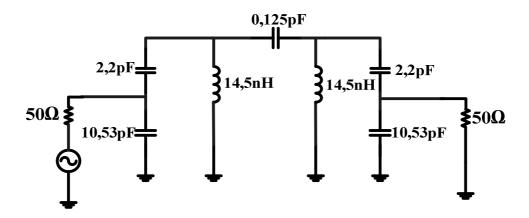

| III.1. Conception du filtre                                                 | 107        |

| III.1.1. Conception de l'inductance compensée                               | 107        |

| III.1.1. Optimisation du transformateur                                     | 107        |

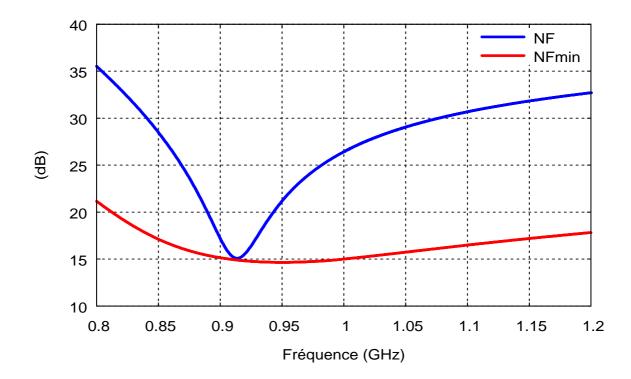

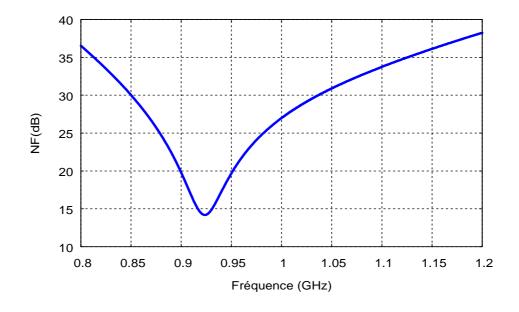

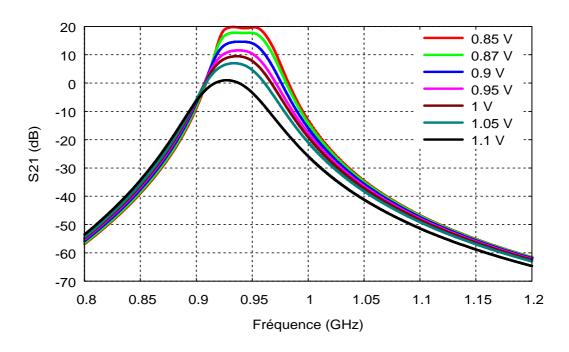

| III.1.1.2. Choix du transistor et optimisation en bruit                     | 108        |

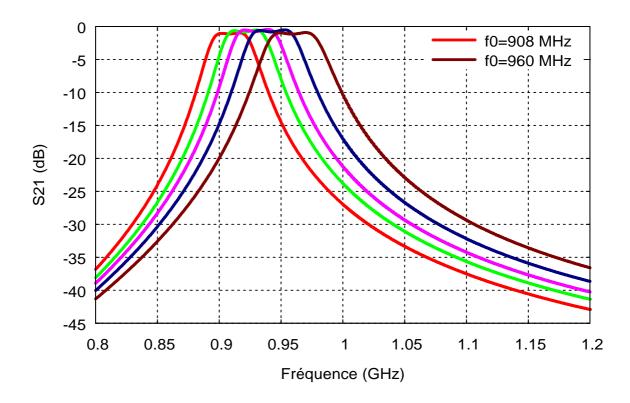

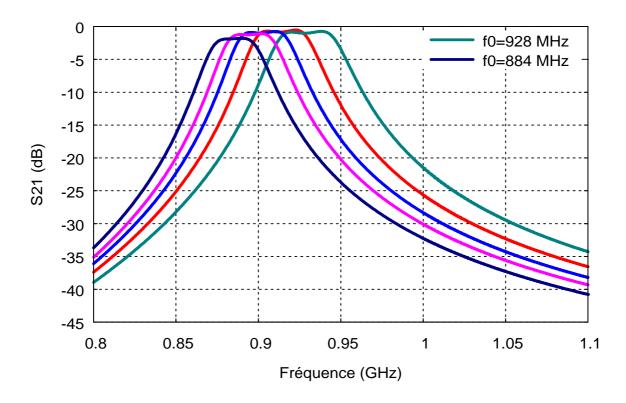

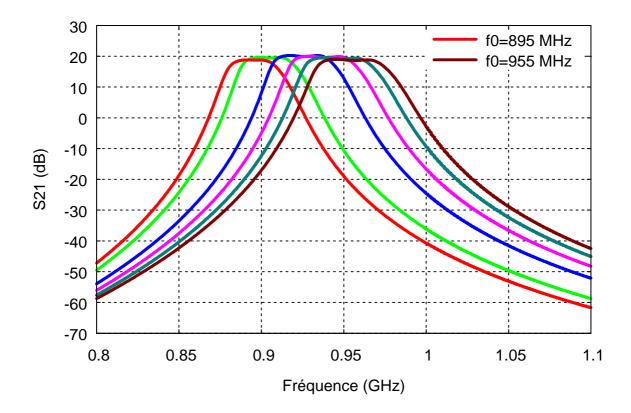

| III.1.1.3. Accordabilité de la fréquence centrale                           | 110        |

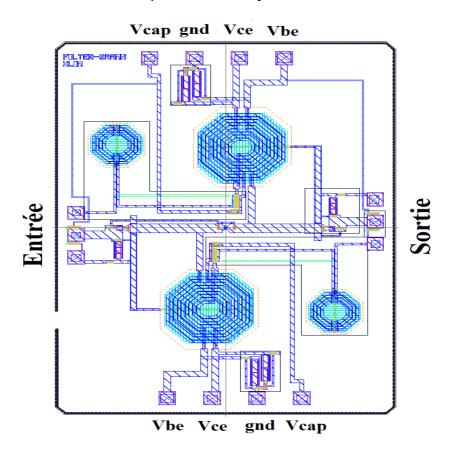

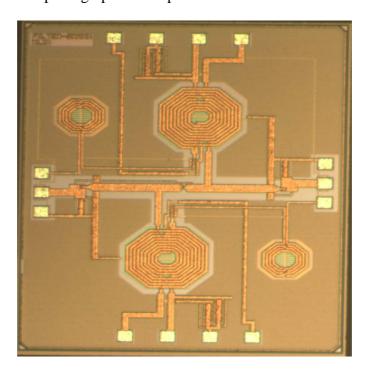

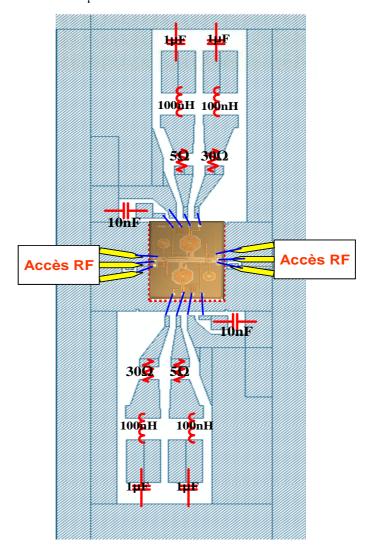

| III.1.2. Layout du filtre                                                   | 111        |

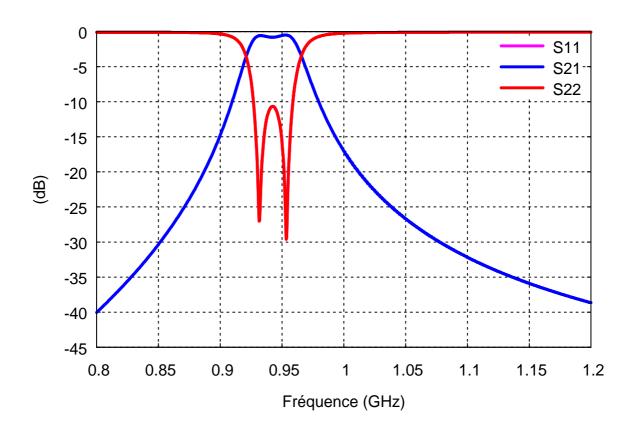

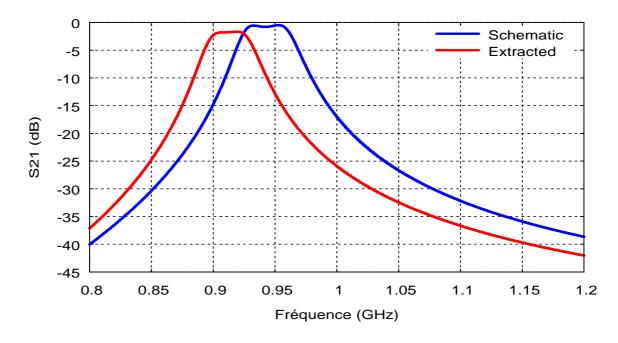

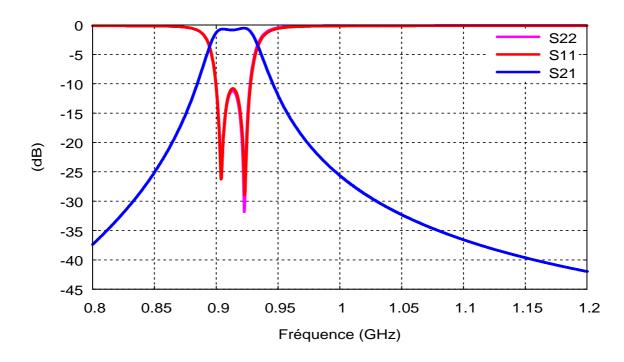

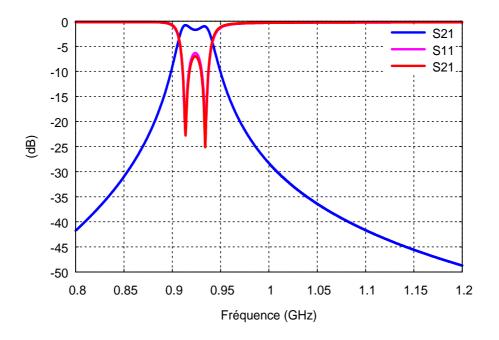

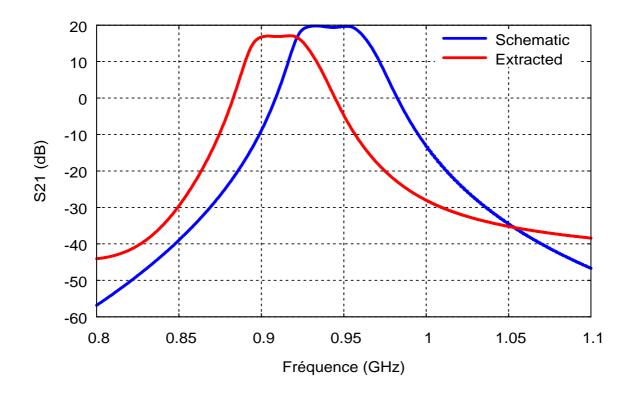

| III.1.2.1. Résultats de simulation                                          | 113        |

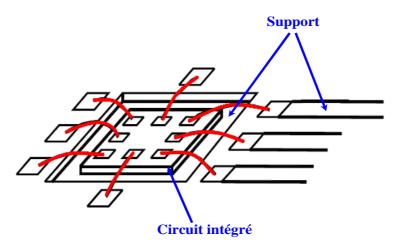

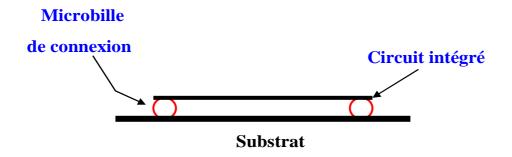

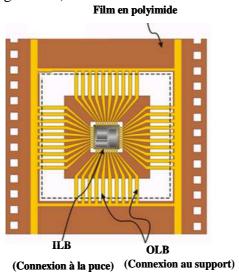

| III.1.3. Report du circuit filtre                                           | 117        |

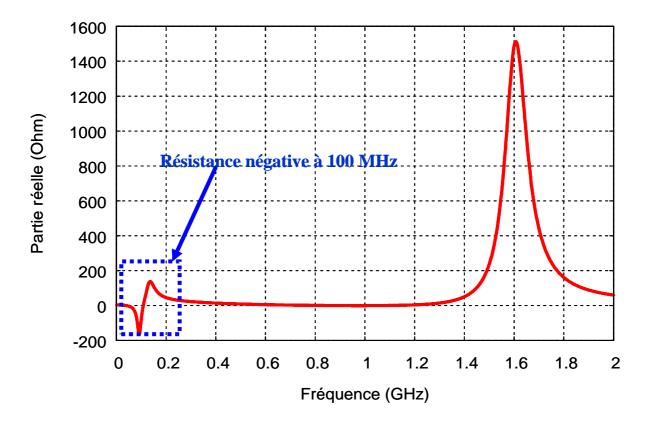

| III.1.3.1. Origine de l'instabilité basses fréquences                       | 118        |

| III.1.3.2. Caractéristiques du substrat du circuit support                  | 120        |

| III.1.3.3. Analyse du circuit de report                                     | 120        |

| III.1.3.4. Résultats de simulation                                          | 121        |

| III.2. Amplificateur faible bruit                                           | 123        |

| III.2.1. Rôle et topologies du LNA                                          | 123        |

| III.2.2. Conception du LNA                                                  | 124        |

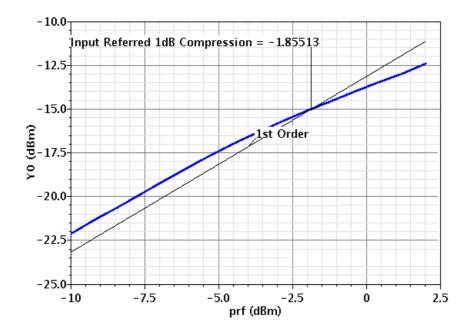

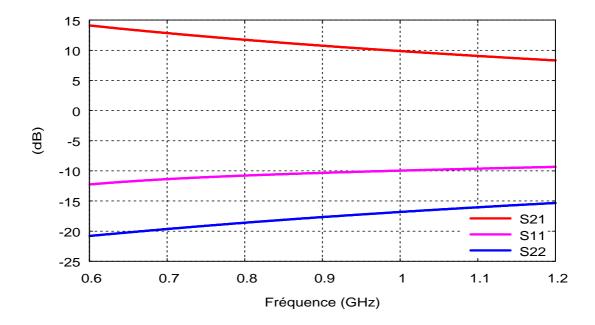

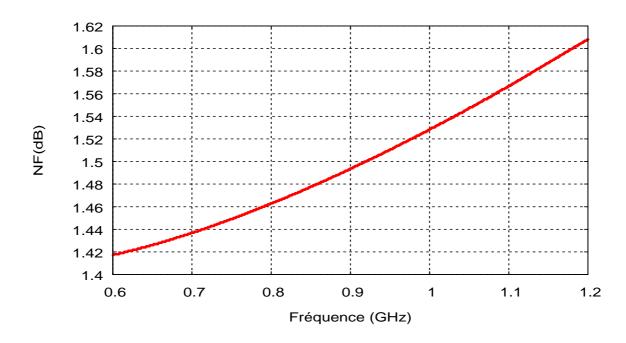

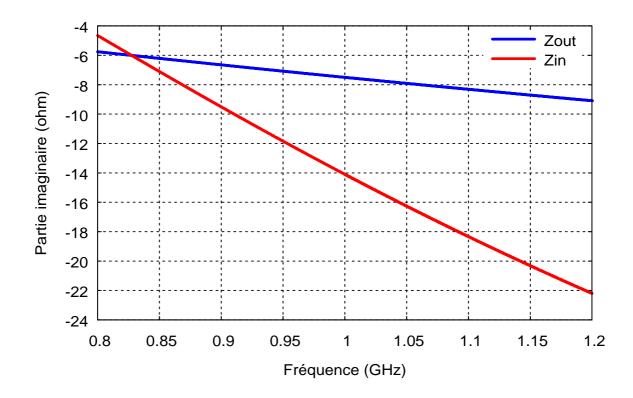

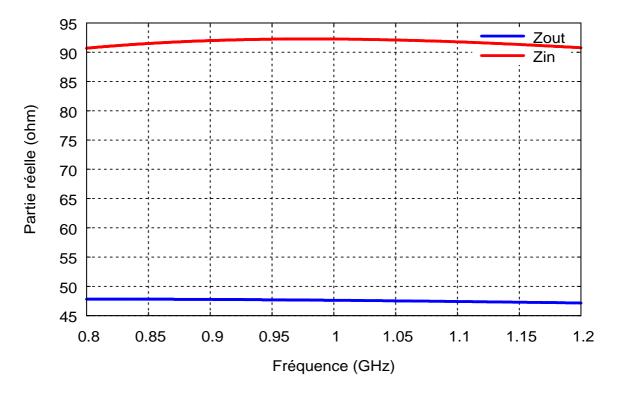

| III.2.2.1. Résultats de simulation                                          | 127        |

| III.3. LNA filtrant                                                         | 130        |

| III.3.1. Conception du circuit LNA Filtrant                                 | 130        |

| III.3.1.1. Résultats de simulation                                          | 131        |

# Sommaire

| IV. Conclusion                                            | 139       |

|-----------------------------------------------------------|-----------|

| V. Références Bibliographiques                            | 140       |

| Conclusion générale et perspectives                       | 143       |

| Annexe A : Critères de stabilité d'un étage amplificateur | 149       |

| Annexe B : Facteur de qualité en charge d'un résonateur   | 155       |

| Annexe C: Techniques de connexions entre la puce et le c  | ircuit de |

| report                                                    | 161       |

# INTRODUCTION GENERALE

Les systèmes de télécommunications sans fil ont évolué de façon rapide depuis une vingtaine d'année. La conception de ces systèmes est soumise à de nombreux challenges :

- le coût de production,

- les techniques d'intégration des composants,

- l'encombrement etc.

La technologie monolithique et plus précisément les procédés de fabrication de circuits silicium (CMOS et BiCMOS) offrent depuis plusieurs années une possibilité de pallier à ce type de difficultés. Ils permettent aujourd'hui l'intégration de plusieurs fonctions RF et mixte sur une seule puce.

Malheureusement, la conception de certaines fonctions RF pose encore problème. C'est le cas des filtres radiofréquences qui constituent les éléments essentiels du système de télécommunication GSM. Les exigences demandées par ces filtres conduisent à étudier des solutions de filtres actifs, car les structures passives (à cavité ou diélectrique ou à ondes acoustiques de surface) ne permettent pas d'avoir de meilleures performances en pertes d'insertion, en sélectivité, en encombrement et en accordabilité fréquentielle.

Dans cette thèse préparée avec le soutien contractuel de l'ANR (projet SRAMM (Systèmes de Réception Adaptatifs Multimodes Multistandards)), nous nous sommes intéressés à l'étude d'une nouvelle topologie de filtrage actif LC basée sur l'utilisation d'une inductance compensée à trois inductances couplées. Notre travail consiste également à définir une méthodologie de modélisation des trois inductances couplées et à utiliser cette dernière pour la réalisation d'un circuit LNA filtrant utilisable en bande GSM.

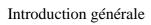

Ce rapport est organisé en trois chapitres. La Figure 1 présente le synoptique de la démarche suivie dans cette thèse.

Figure 1: Synoptique de la thèse

Le premier chapitre est dédié à l'étude bibliographique des filtres actifs en technologie silicium. Ce chapitre à pour objectif de présenter un aperçu des architectures publiées dans la littérature. Des filtres actifs analogiques continus (Gm-C), filtres actifs récursifs et transversaux, filtres à inductance active et filtres actifs LC (Q-enhanced LC) sont présentés en évoquant leurs avantages et leurs limitations.

Le deuxième chapitre détaille une étude théorique de l'inductance compensée proposée, ainsi que les différentes étapes de modélisation du transformateur en technologies CMOS 65 nm et BiCMOS 0,25 µm. La validation de cette étude est réalisée à travers la conception de deux inductances compensées pour une application dans la bande de réception du standard GSM et UMTS.

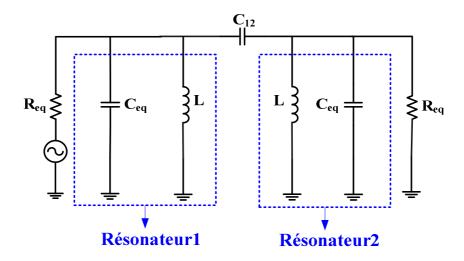

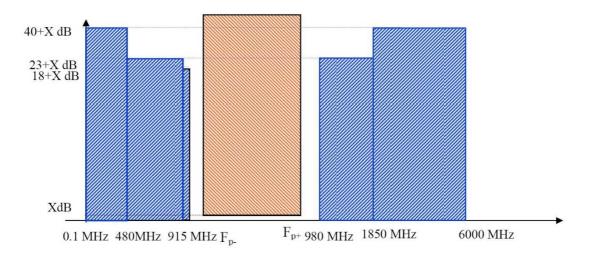

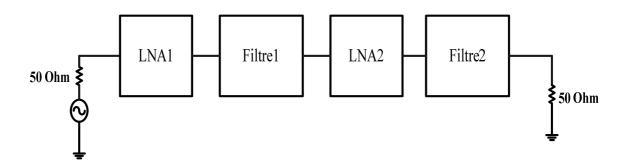

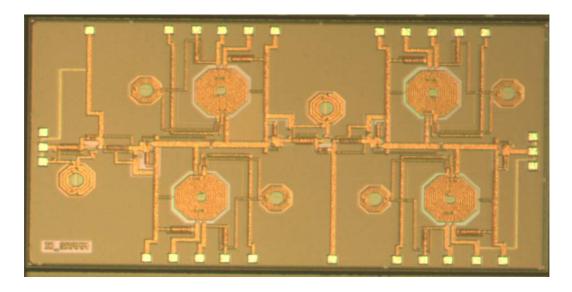

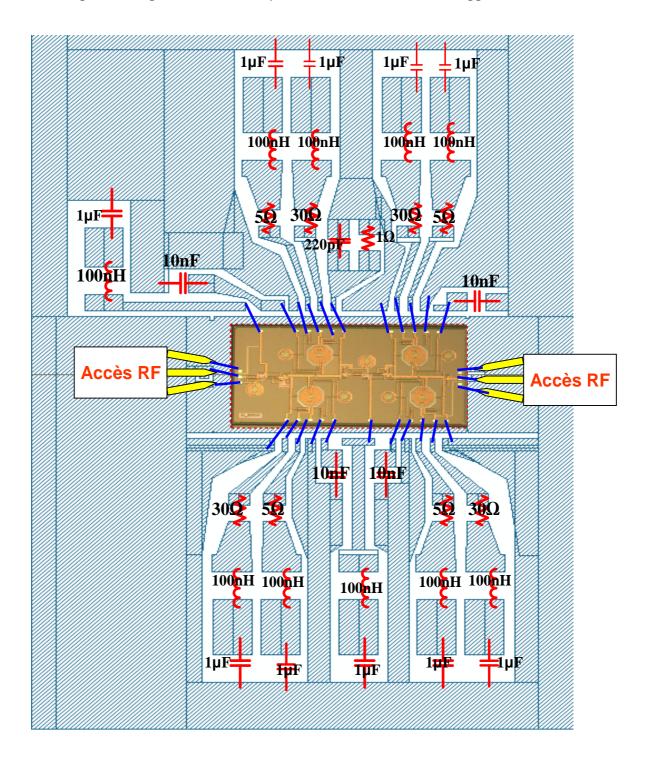

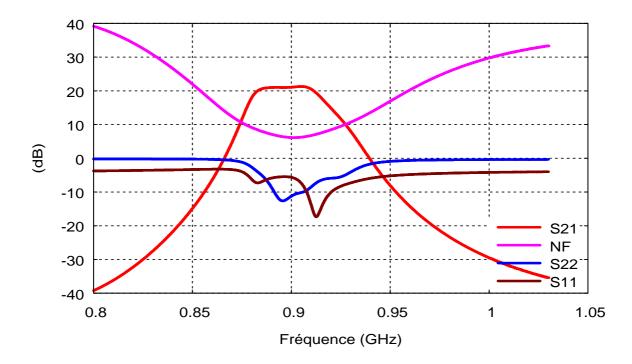

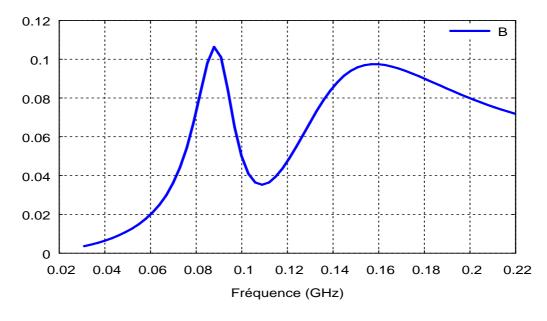

Le troisième chapitre analyse une topologie de filtrage passe bande utilisant l'inductance compensée présentée dans le deuxième chapitre. Cette topologie se base sur le principe de transformation d'impédance entre l'inductance compensée et les impédances de source et de charge. La conception intégrée de cette architecture de LNA filtrant constitué de quatre blocs (LNA1-Filtre1- LNA2-Filtre2) est décrite en détail. Cette partie inclut l'étude du report sur substrat d'alumine des fonctions élémentaires (LNA, filtre) et de l'ensemble LNA1-filtre1-LNA2-filtre2 pour effectuer les mesures.

Enfin, nous concluons ce manuscrit et présentons quelques perspectives à ces travaux.

# Chapitre I :Etat de l'art sur le filtrage actif en technologie silicium

# I. Introduction

Le développement des systèmes de communication modernes conduit aujourd'hui à une évolution importante dans les domaines de l'électronique RF et microonde. Cette évolution est liée à plusieurs exigences telles que l'intégration, le coût et la fiabilité des circuits.

La fonction de filtrage est une des principales fonctions analogiques utilisées dans l'architecture des systèmes modernes dont l'optimisation et l'intégration posent de nombreux problèmes.

L'amélioration de cette fonction implique la recherche d'architectures spécifiques, la mise en œuvre de nouvelles méthodes d'analyse, de conception et des choix de technologies optimisés.

Dans ce cadre, nous introduisons ci-après le rôle et la nécessité des filtres RF dans les systèmes de télécommunications et l'intérêt de proposer des solutions alternatives avec des filtres entièrement intégrables.

Nous effectuons ensuite un état de l'art de différents types de filtres actifs radiofréquences et microondes intégrés en technologie silicium.

# II. Rôle des filtres RF dans les chaînes de télécommunication

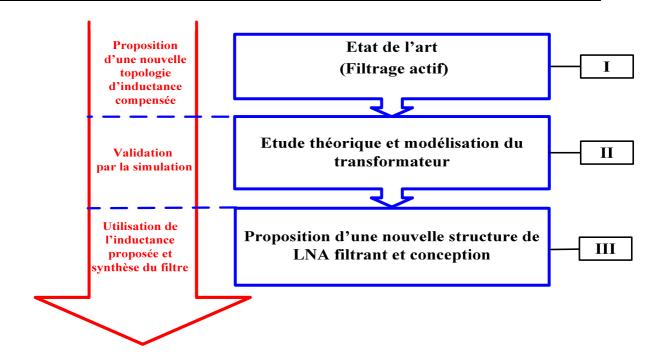

Une chaîne d'émission-réception de type superhétérodyne peut être représentée d'une manière générale par le synoptique de la Figure I-1. L'antenne permet la réception des signaux, le commutateur permet de commuter entre le canal émission et réception. Dans le canal de réception le filtre RX-RF permet la sélection de la bande de réception, l'amplificateur faible bruit « LNA» amplifie le signal utile et préserve le système du bruit. Le filtre RX-IF placé derrière le mélangeur effectue un filtrage à la fréquence intermédiaire avant la conversion en bande de base. Dans l'émission, ces filtres sont essentiellement responsables de la mise en forme du signal fourni à l'amplificateur de puissance.

Figure I-1: Architecture superhétérodyne d'une chaîne d'émission-réception

Dans le contexte des applications de télécommunications sans fil multi standards, les filtres RF exigent des performances en termes de sélectivité, de linéarité et de consommation très élevées. L'intégration de ces filtres RF à hautes performances est un enjeu industriel important.

Actuellement, les filtres passifs non intégrables tels que les filtres à cavités [1], à guides d'ondes [2], céramiques [3] et les filtres SAW (Surface Acoustic Wave) [4] sont très largement utilisés. Ces filtres offrent de très bonnes performances, mais leurs dimensions encombrantes et leurs pertes d'insertion représentent un inconvénient majeur. De plus, ils sont difficilement accordables en fréquence.

Dans ces conditions, les filtres actifs représentent une alternative intéressante vu leur facilité d'intégration et la possibilité d'être accordables en fréquence. Malheureusement, l'utilisation de ces filtres imposent la prise en compte des nouveaux paramètres tels que :

- la stabilité,

- les performances en bruit,

- la linéarité,

- la consommation,

Afin d'établir l'état de l'art des précédents travaux, nous réalisons une étude bibliographique des principaux types de filtres actifs, en analysant leurs utilisations et leurs performances.

# III. Etat de l'art des filtres actifs

# III.1. Introduction

Plusieurs travaux de recherche ont traité du développement des filtres actifs intégrés. Dans la littérature, différentes architectures ont été proposées et étudiées. Les paragraphes qui suivent décrivent les principales catégories des filtres actifs en relevant leurs limitations et leurs avantages.

# III.2. Classification des filtres actifs [5] [6] [7]

En fonction de l'analyse bibliographique effectuée, les filtres actifs peuvent être regroupés en quatre catégories principales :

- ♦ Les filtres actifs analogiques continus (Gm-C),

- ♦ Les filtres actifs récursifs et transversaux,

- ♦ Les filtres à inductance active.

- ♦ Les filtres actifs LC (Q-enhanced LC),

Les travaux développés dans ce manuscrit concernent la quatrième catégorie, c'est-àdire, les filtres actifs LC (Q-enhanced LC).

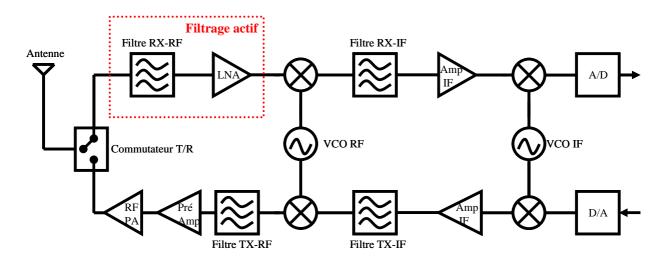

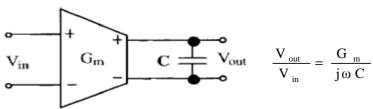

#### III.2.1. Les filtres actifs analogiques continus (Gm-C)

Les filtres Gm-C (Transconductance-Capacitor) sont bien adaptés pour les applications à hautes fréquences telles que la vidéo numérique et le filtrage IF [8] [9] et sont principalement destinés à la réalisation des filtres d'ordre élevé ( $\geq 5$ ). Ces filtres sont constitués d'une transconductance Gm associée à une capacité C comme le montre la Figure I-2. La fonction de transfert dépend du rapport  $G_m/C$  qui détermine les caractéristiques en fréquence de ces filtres.

Figure I-2: Principe des filtres actifs Gm-C

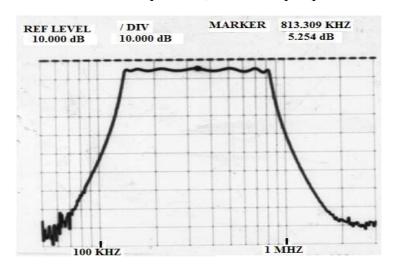

Un exemple de réalisation de filtre Gm-C d'ordre quatorze étudié par Zhong Yuan Chang [10] est présenté sur la Figure I-3. L'avantage principal de ces filtres réside dans la possibilité de pouvoir régler la valeur de la transconductance  $G_m$  pour compenser les pertes dues aux procédés de fabrication. Cependant, la limitation principale de ce genre de filtres est qu'ils ne peuvent pas être utilisés à très hautes fréquences (100 KHz à quelques centaines de MHz).

Figure I-3: Réponse en transmission (S21)

Le tableau I-1 représente une liste des publications correspondant à cette catégorie de filtres.

|                                | [11] 2003 | [12] 2006  | [13] 2007 | [14] 2007 | [15] 2011  | [16] 2011 |

|--------------------------------|-----------|------------|-----------|-----------|------------|-----------|

| Fréquence centrale             | 1,5~12    | 800~1400   | 0,00025-1 | 80        | 10-42      | 2         |

| (MHz)                          |           |            |           |           |            |           |

| Facteur de qualité             | -         | -          | -         | 16~44     | -          | -         |

| Ordre de filtre                | 6         | 6          | 5         | 5         | 5          | 5         |

| Consommation                   | 15        | 24,2       | 0,8       | 66        | 21,6       | 8,82      |

| (mW)                           | Pour 1,8V | Pour 1,8V  | Pour 1,8V | Pour 3,3V | Pour 1,8V  | Pour 1,8V |

| Technologie (µm)               | 0,18      | TSMC       | TSMC      | 0,25      | 0,065      | 0,18      |

|                                | CMOS      | 0,18 CMOS  | 0,18 CMOS | BiCMOS    | CMOS       | CMOS      |

| Réalisation (mm <sup>2</sup> ) | 0,83      | Simulation | 0,3       | 0,36      | Simulation | 1,36      |

|                                |           |            |           |           |            |           |

Tableau I-1 : Performances de quelques filtres Gm-C

## III.2.2. Les filtres actifs récursifs et transversaux

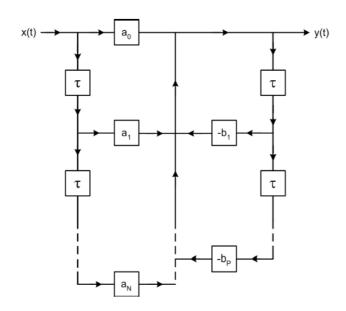

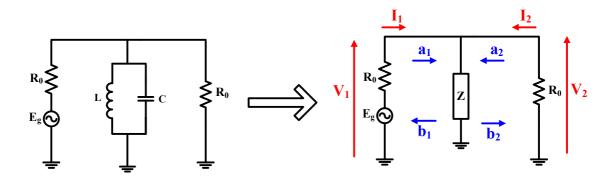

Les applications de cette catégorie de filtres sont initialement celles du traitement numériques du signal. Les filtres récursifs et transversaux sont régis par l'équation temporelle (I-1) dans laquelle x(t) et y(t) représentent respectivement les signaux d'entrée et de sortie du filtre.

$$y(t) = \sum_{k=0}^{N} a_k . x(t - k\tau) - \sum_{p=1}^{P} b_p . y(t - p\tau)$$

(I-1)

Le premier terme de l'équation (I-1) caractérise la partie transversale du dispositif, tandis que le second terme représente la partie récursive.

Pour représenter graphiquement ce type de filtre on utilise généralement un graphe de fluence tel que celui présenté sur la Figure I-4.

Figure I-4 : Graphe de fluence d'un filtre de type récursif et transversale

La réponse du filtre est obtenue par combinaison de signaux élémentaires retardés, pondérés par les coefficients  $\{a_k\}$  et  $\{b_k\}$ .

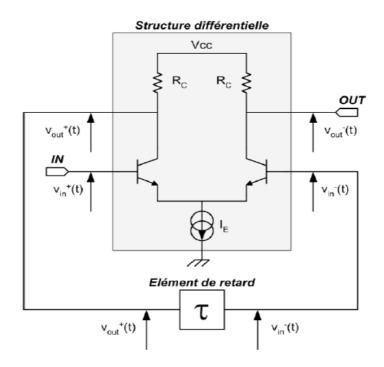

Plusieurs filtres basés sur ce principe ont été réalises à XLIM. Dans la référence [17], l'auteur présente un circuit récursif d'ordre 1, à fréquence centrale fixe, réalisé autour d'une structure différentielle remplissant les fonctions d'amplification et de sommation (Figure I-5).

Figure I-5 : Principe du circuit de filtre récursif d'ordre 1

Figure I-6 : Réponse S21 du filtre

Les résultats de mesures (cf. Figure I-6) montrent que la bande passante de ce filtre est 260 MHz. La fréquence centrale est 1,95 GHz et le gain varie entre 5 et 10 dB selon la polarisation des transistors. Le facteur de bruit est 4,6 dB et la consommation est de 12 mA.

## III.2.3. Les filtres actifs à inductance active

L'inductance " passive " intégrée est un composant qui possède un facteur de qualité relativement faible. Cette caractéristique compromet totalement la réalisation de filtres actifs intégrés RF très sélectifs.

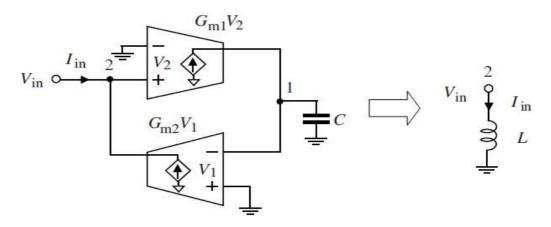

Une des méthodes de conception des filtres actifs intégrés consiste à remplacer l'inductance "passive" par un circuit qui génère un effet inductif. Ces circuits sont souvent appelés inductances actives. La majorité des circuits réalisés à partir d'une inductance active utilisent le principe d'un gyrateur présenté sur la Figure I-7 [18]. Son rôle est de présenter à son entrée, une impédance proportionnelle à l'inverse de son impédance de charge.

Figure I-7 : Inductance active basée sur le principe d'un gyrateur

L'admittance d'entrée d'un gyrateur est :

$$Y_{in} = \frac{I_{in}}{V_2} = \frac{1}{j\omega(\frac{C}{G_{m1}G_{m2}})}$$

(I-2)

L'équation (I-2) montre que le port 2 de la Figure I-7 représente une inductance reliée à la masse de valeur :

$$L = \frac{C}{G_{m1}G_{m2}}$$

(I-3)

A partir du réglage du Gm1 et Gm2, la valeur de l'inductance active (L) peut être modifiée. Ainsi, un résonateur LC peut être réalisé en associant le gyrateur à une capacité C1 (cf. Figure I-8).

Figure I-8: Résonateur LC

La fréquence de résonance du résonateur est donnée par l'expression suivante :

$$f_0 = \frac{1}{2\pi \sqrt{\frac{C}{G_{ml}G_{m2}}C1}}$$

(I-4)

Néanmoins, les principaux défauts de ce type de circuit restent toujours le bruit important et la non linéarité. De plus, le nombre relativement élevé de transistors nécessaires pour la réalisation de ces montages entraîne une consommation importante.

## III.2.3.1. Exemples de circuits d'inductance active

Dans ce paragraphe, nous présentons trois exemples de circuits d'inductance active.

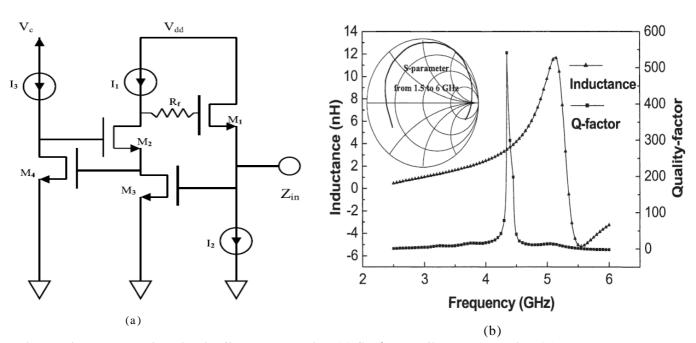

La Figure I-9 présente la réalisation d'une inductance active en technologie 0,18um CMOS [19]. L'inductance active est constituée d'un gyrateur associé à une rétroaction résistive Rf et à un transistor NMOS.

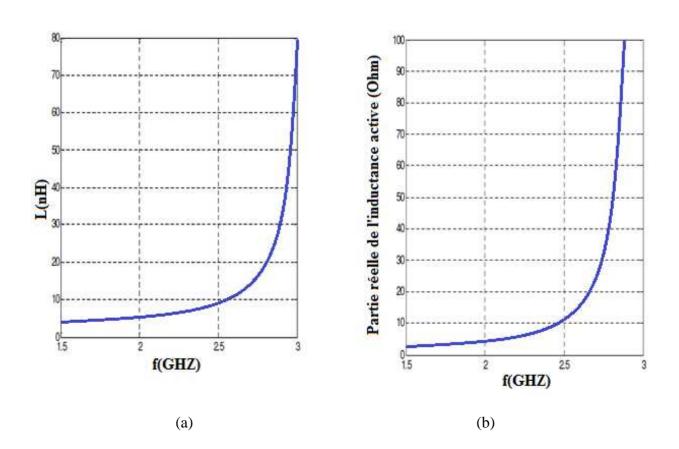

Figure I-9 : Exemple d'un circuit d'inductance active. (a) Schéma de l'inductance active. (b) Facteur de qualité et valeur de l'inductance.

Les résultats de mesure montrent que la valeur de l'inductance est 3,2 nH et le facteur de qualité est égal à 540 à 4,3 GHz. La fréquence de résonance de l'inductance active est 5,4 GHz.

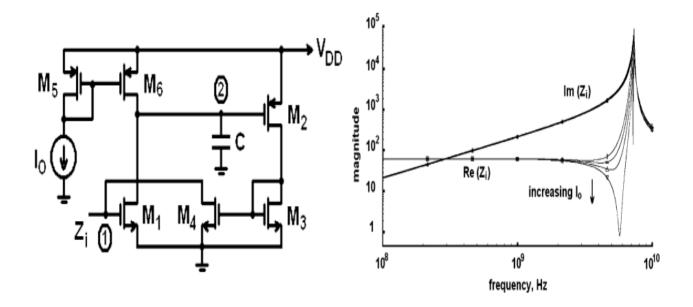

Un deuxième exemple d'inductance active utilisant le principe d'un gyrateur est présenté dans la Figure I-10 [20]. Cette inductance est conçue en technologie 0,13 µm CMOS. Les résultats de simulation montrent que cette topologie peut être utilisée entre 900MHz et 6 GHz. La valeur de l'inductance varie entre 38nH et 144 nH. Le facteur de qualité à 5,75 GHz est égal à 3900.

Figure I-10: Inductance active

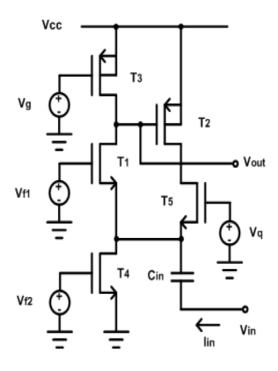

Le troisième exemple d'inductance active est présenté dans la Figure I-11 [6]. Cette topologie utilise le principe de transformation d'impédance en utilisant les transconductances des transistors MOS et leurs capacités parasites Cgs.

Figure I-11 : Filtre passe-bande à inductance active

Figure I-12 : (a) valeur de l'inductance. (b) valeur de sa résistance de perte

Les caractéristiques de l'inductance active sans l'ajout de la capacité en l'entrée Cin sont représentées sur la Figure I-12. Cette inductance à une valeur de 5 nH et sa résistance de perte est 4,1  $\Omega$  à 2 GHz. Cela donne un facteur de qualité de 15,7. Sa fréquence de résonance est de 3,04 GHz.

Le problème de cette topologie est le faible facteur de qualité (Q=15,7). Il est donc nécessaire d'ajouter un dispositif de compensation pour augmenter cette valeur. Ce dispositif est appelé « résistance négative » que nous allons étudier dans le paragraphe suivant.

Le tableau I-2 montre les performances de quelques circuits d'inductance active.

|                 | [21] 2011  | [22] 2011  | [23] 2009  | [24] 2005  | [25] 2004          | [26] 2000  |

|-----------------|------------|------------|------------|------------|--------------------|------------|

| Fréquence       | 0,35       | 2          | 2,3 ~2,4   | 2,05~2,45  | 5,7                | 1,68       |

| centrale (GHz)  |            |            |            |            |                    |            |

| Facteur         | 11400      | 10~148     | >350       | 30~300     | > 665              | 19-250     |

| de qualité      |            |            |            |            |                    |            |

| Bande           | -          | 100        | -          | 8~80       | -                  | -          |

| passante(MHz)   |            |            |            |            |                    |            |

| Ordre de filtre | -          | 4          | 2          | 6          | 1                  | -          |

| Consommation    | 1,8        | 11,28      | 5,1        | 4,7        | 4,4                |            |

| (mW)            | Pour 0,8V  | Pour 3,25V | Pour 2,3V  | Pour 1,8V  | Pour 1,8V          | 24,3       |

| Technologie     | 0,18 μm    | AMS        | AMS        | 0,25 μm    | TSMC               | 0,5 μm     |

| (CMOS)          |            | 0,35μm     | 0,35µm     |            | 0,18µm             |            |

| Résultat        | Simulation | Simulation | Simulation | Simulation | Mesure             | Simulation |

|                 |            |            |            |            | 798μm <sup>2</sup> |            |

|                 |            |            |            |            |                    |            |

Tableau I-2: Inductance active [21] et filtres à inductance active [22] [23] [24] [25][26]

# III.2.4. <u>Les filtres actifs LC à facteur de qualité compensé (Qenhanced LC)</u>

Comme mentionné précédemment, la principale limitation des filtres RF actifs sélectifs est le faible facteur de qualité des inductances utilisées dans les résonateurs du filtre. Afin d'augmenter ce facteur de qualité, il faut minimiser la valeur de la résistance série des inductances passives. Plusieurs techniques ont été utilisées pour pallier ce problème à l'aide des méthodes passives telle que l'ajout d'un "écran électrostatique" au dessous de l'inductance spirale [27]. Malheureusement, ce facteur de qualité reste toujours limité à une valeur inférieure à 24 dans la technologie CMOS [28] [29].

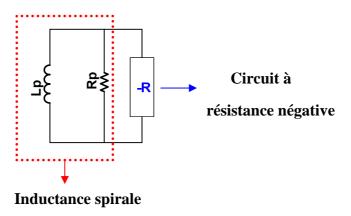

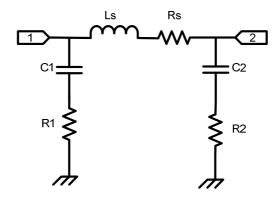

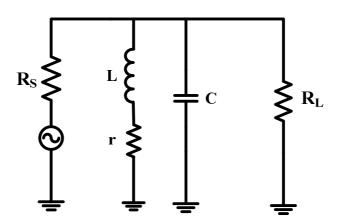

Les filtres actifs LC à facteur de qualité compensé utilisent un dispositif actif qui permet de générer une résistance négative pour compenser les pertes dans les inductances lors de l'intégration des filtres passifs LC (Figure I-13). Toutefois, l'importante surface occupée par les inductances passives augmente le coût de production de ce type de filtre.

Figure I-13 : Principe de compensation du facteur de qualité

Etant donné que cette résistance négative est associée en parallèle avec l'inductance spirale formant le résonateur, le circuit équivalent série qui modélise l'inductance spirale est transformé en un circuit parallèle comme montre la Figure I-14.

Figure I-14: Transformation d'un circuit résonnant série vers un circuit résonnant parallèle

Avec:

$$\begin{cases} L_p = L_s(\frac{Q^2 + 1}{Q^2}) \\ R_p = R_s(Q^2 + 1) \end{cases}$$

$$Q = \frac{L_s \omega}{R_s}$$

(I-5)

Le facteur de qualité de l'inductance spirale (Q) est très supérieur à 1 donc l'équation (I-5) devient :

$$L_p = L_s$$

$$R_{p} = R_{s}(Q^{2}) = \frac{\omega^{2}Ls^{2}}{R_{s}}$$

Pour compenser les pertes de l'inductance spirale la valeur de la résistance négative pour une fréquence donnée s'exprime par :

$$R_{\text{neg}} = \frac{-\omega^2 L_s^2}{R_s}$$

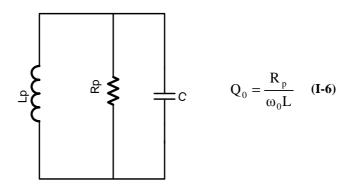

En outre, le facteur de qualité à vide d'un résonateur RLC parallèle (Figure I-15) s'exprime par :

Figure I-15: Résonateur RLC parallèle

En remplaçant Rp (équation (I-6)) par sa valeur trouvée dans l'équation (I-5) on obtient :

$$Q \approx Q_0$$

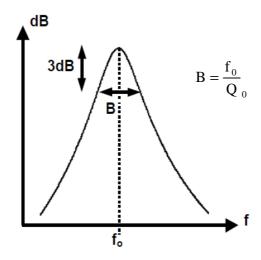

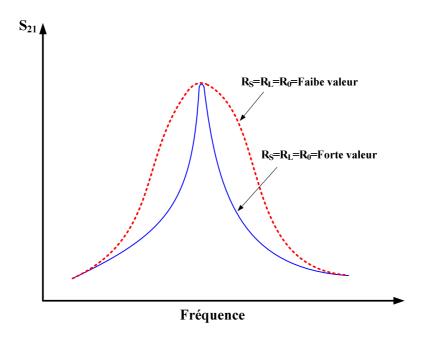

Cela montre que le facteur de qualité du résonateur est pratiquement égal au facteur de qualité de l'inductance seule. La relation entre le facteur de qualité du résonateur et la bande passante a -3dB est illustrée dans la Figure I-16. Cela montre aussi que logiquement la sélectivité du filtre dépend du facteur de qualité du résonateur.

Figure I-16 : Relation entre facteur de qualité Q du résonateur et la bande passante à -3dB (B)

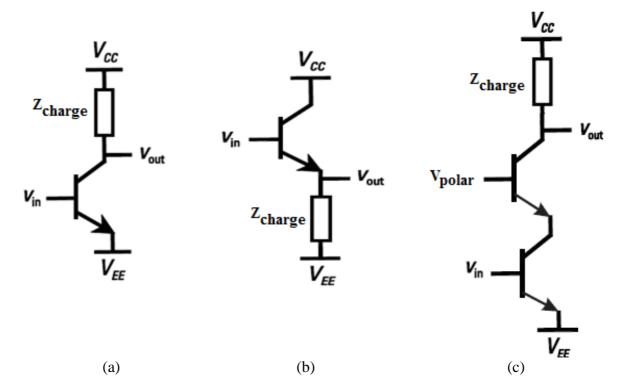

#### III.2.4.1. Architectures de résistances négatives

Dans la littérature, nous trouvons que la résistance négative est réalisée à partir de quatre types d'architectures.

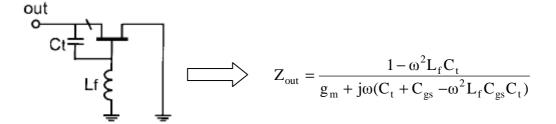

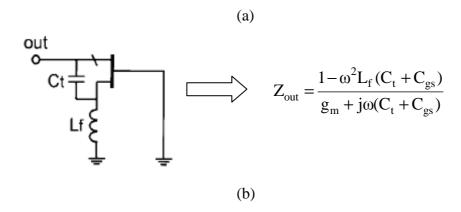

La première architecture (en supposant que l'on utilise un transistor à effet de champ) est de type grille commune avec rétroaction inductive série Figure I-17 (a) ou drain commun avec rétroaction inductive série Figure I-17 (b) [30]. Ce montage permet l'accord en fréquence de la résistance négative à travers la capacité Ct. Le fait d'utiliser un seul transistor dans cette architecture permet d'avoir une faible consommation du circuit.

Figure I-17 : (a) Grille commune avec rétroaction inductive série. (b) Drain commun avec rétroaction inductive série

La partie réelle de l'impédance de sortie  $Z_{out}$  représente la valeur de la résistance négative, et à pour expression  $\frac{g_m(1-\omega^2L_f(C_t+C_{gs}))}{g_m^2+\omega^2(C_t+C_{gs})^2}$  (Figure I-17 (b)). La résistance négative est obtenue en choisissant correctement les valeurs de l'inductance  $L_f$  et des capacités  $C_t$  et  $C_{gs}$ .

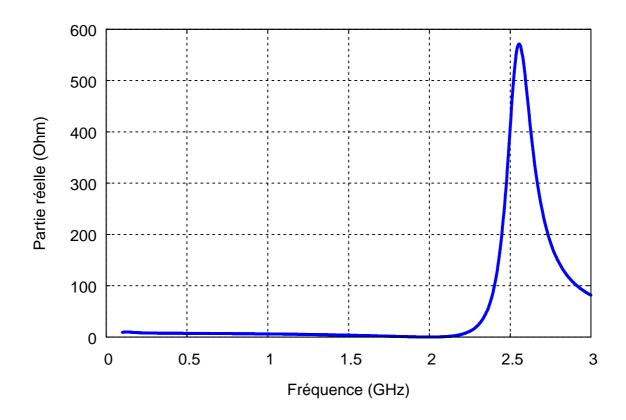

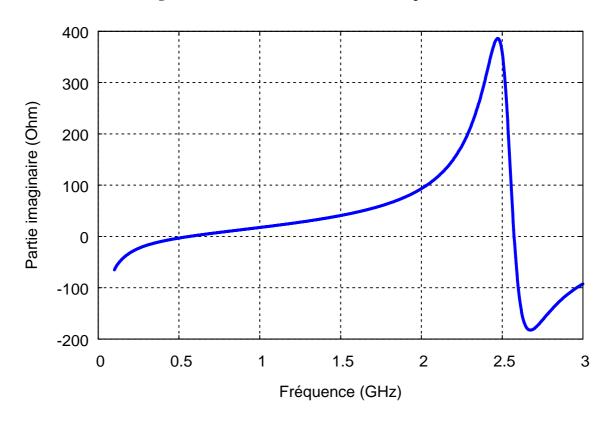

La Figure I-18 présente les résultats de mesure de la partie réelle et imaginaire de l'impédance Zout du montage drain commun avec rétroaction inductive série. Nous remarquons d'après la figure que la résistance négative est obtenue entre 4,6 à 5,5 GHz. Sa valeur maximale est -3,1 Ohm.

Figure I-18 : Partie réelle et imaginaire de l'impédance de sortie du montage drain commun avec rétroaction inductive série

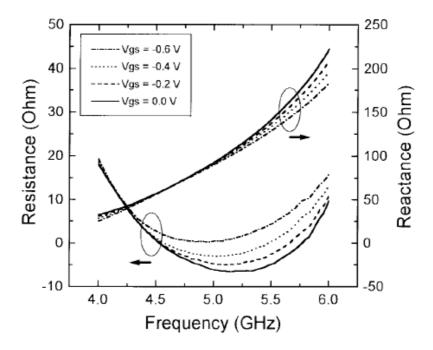

La deuxième architecture est constituée d'une paire de transistors couplés (Figure I-19). Le réglage de la résistance négative est réalisé grâce à la source de courant connectée aux sources des 2 transistors. Plusieurs travaux et réalisations ont été présentés concernant cette architecture en technologie CMOS [31] [32] [33] et bipolaire-BiCMOS [34] [35].

Figure I-19 : Paire des transistors couplés réalisant une résistance négative

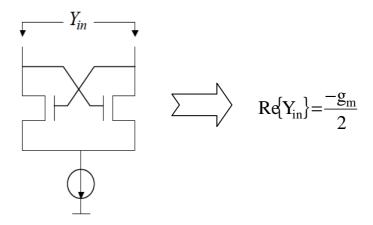

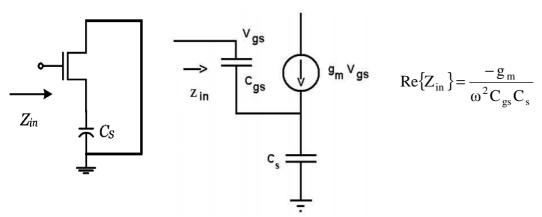

La troisième architecture est représentée sur la figure I-20 [36]. Elle est composée d'un transistor NMOS associé à une capacité  $C_s$  connectée à la source. Ce type de montage est utilisé dans les applications à bande étroite et simple accès.

Figure I-20 : Résistance négative à un seul accès et schéma équivalente

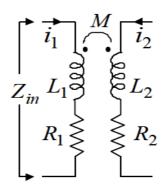

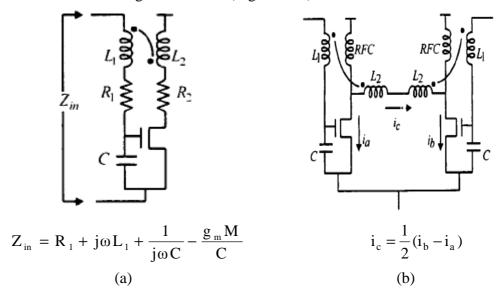

La quatrième architecture présente une technique originale de compensation des pertes [37]. La mutuelle inductance M produite par le couplage magnétique entre deux inductances L1 et L2 forme une résistance négative. Cette résistance négative compense les pertes de l'inductance L1 (Figure I-21).

Figure I-21 : Couplage magnétique entre deux inductances L1 et L2

L'impédance d'entrée Z<sub>in</sub> est donnée par la relation suivante :

$$\begin{split} Z_{in} &= R_1 + j\omega L_1 + j\omega M\,\frac{i_2}{i_1} = R_{eff}\,+\,j\omega L_{eff} \\ Et: &\qquad \frac{i_2}{i_1} = Ae^{\,j\theta} = A(\cos\,\theta + j\sin\,\theta) \end{split}$$

L'expression de R<sub>eff</sub> est alors :

$$R_{\rm eff} = R_1 - \omega MA \sin \theta$$

M est la mutuelle entre les inductances. A et  $\theta$  représentent respectivement le module et la phase du rapport entre le courant  $i_2$  et le courant  $i_1$ . Ces deux grandeurs influent directement sur la valeur de la résistance Reff. La valeur de la résistance négative est égale à :

$$R_{neg} = \omega MA \sin \theta$$

La résistance négative peut être obtenue lorsque la différence de phase entre le courant  $i_1$  et le courant  $i_2$  est  $90^0$  ou  $270^0$ .

L'avantage principal de cette technique est qu'elle peut être implantée dans un montage simple accès ou dans un montage différentiel (Figure I-22).

Figure I-22 : Implémentation du circuit (a) simple accès (b) Différentiel

Basés sur cette architecture, deux exemples de filtres actifs LC sont abordés dans la suite.

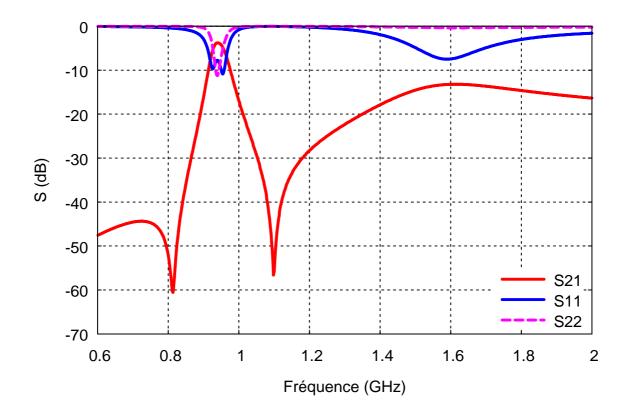

## III.2.4.2. Filtres actifs à résistance négative

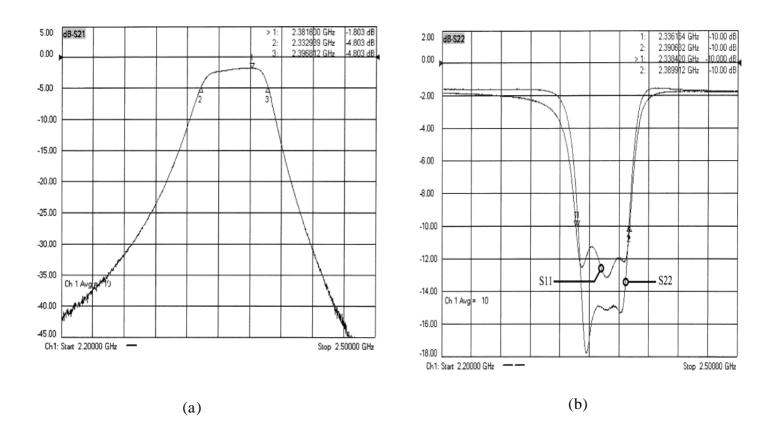

Les Figures I-23 et I-24 présentent la réalisation d'un filtre actif intégré d'ordre 3 dont la fréquence centrale est de 2368 MHz avec compensation des pertes à travers le couplage entre deux inductances [38]. La réponse du filtre peut être reconfigurée grâce au contrôle de la valeur des inductances compensées. La bande passante de ce filtre est 60 MHz et il consomme 5,84 mA à 1,8V. Les niveaux d'adaptation d'entrée et de sortie sont respectivement de -11 dB et -15 dB. Ce filtre est conçu en technologie 0,18 μm CMOS. Les dimensions du circuit sont de 1,5 mm par 1,5 mm.

L'avantage principal de ces filtres est la platitude du gain dans la bande passante avec une faible perte d'insertion (<1,8 dB). Cependant, la limitation principale est la sensibilité à la variation des tensions de polarisation des transistors.

Figure I-23 : Schéma du filtre

Figure I-24 : Exemple de filtre actif à résistance négative.

(a) Réponse S21. (b) Réponse S11 et S22

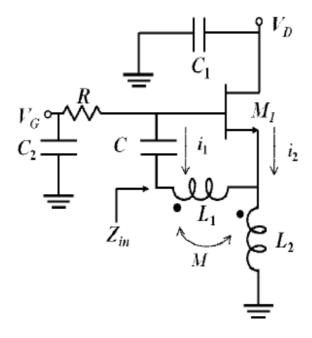

Un autre exemple récent utilisant le même principe est présenté dans la Figure I-25 [39].

Figure I-25 : schématique du circuit simulant une résistance négative

L'impédance d'entrée de ce circuit est donnée par l'expression suivante :

$$Z_{in} = (R_1 + R_2 - \frac{Mg_m}{C} - \frac{L_2g_m}{C}) + j\omega(L_1 + L_2 + 2M + \frac{g_mR_2}{\omega C})$$

Avec  $R_1$  et  $R_2$  correspondant aux pertes résistives des inductances  $L_1$  et  $L_2$ .  $C_1$  et  $C_2$  représentent les capacités de découplage RF.

Les pertes résistives de cette topologie peuvent être compensées par un choix judicieux de la mutuelle M entre les deux inductances et de la valeur de l'inductance  $L_2$ .

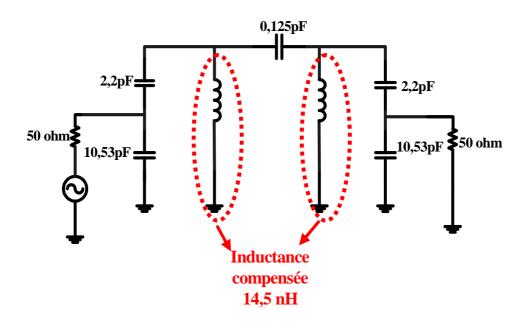

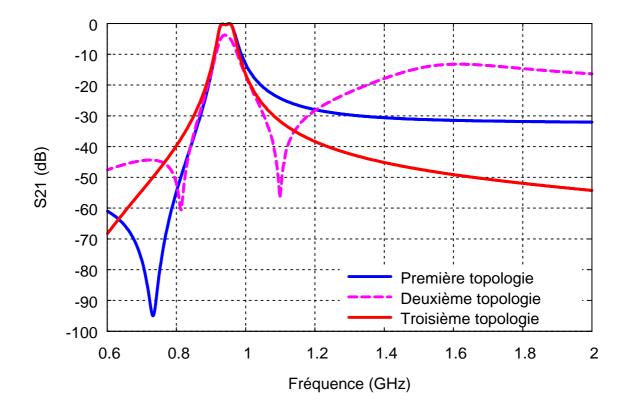

La Figure I-26 présente le filtre d'ordre 2 utilisant le circuit montré ci-dessus. La fréquence centrale est de 2,65 GHz et la bande passante est 300 MHz. Les mesures de ce circuit montrent que ce filtre présente une consommation de 2,4 mW et 1 dB de perte d'insertion. Ce filtre est conçu en technologie 0,18 µm CMOS. Les dimensions du circuit sont de 0,7 mm par 0,9 mm. Cette topologie permet d'obtenir l'accordabilité fréquentielle par l'intermédiaire des varactors. L'inconvénient principal de cette topologie est le faible niveau de réjection en hautes fréquences (Figure I-26 (b)).

Figure I-26 : Deuxième exemple de filtre actif à résistance négative.

(a) Schéma du circuit. (b) réponse S21 et S11

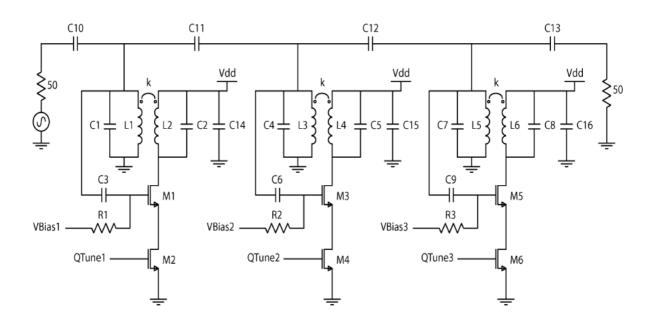

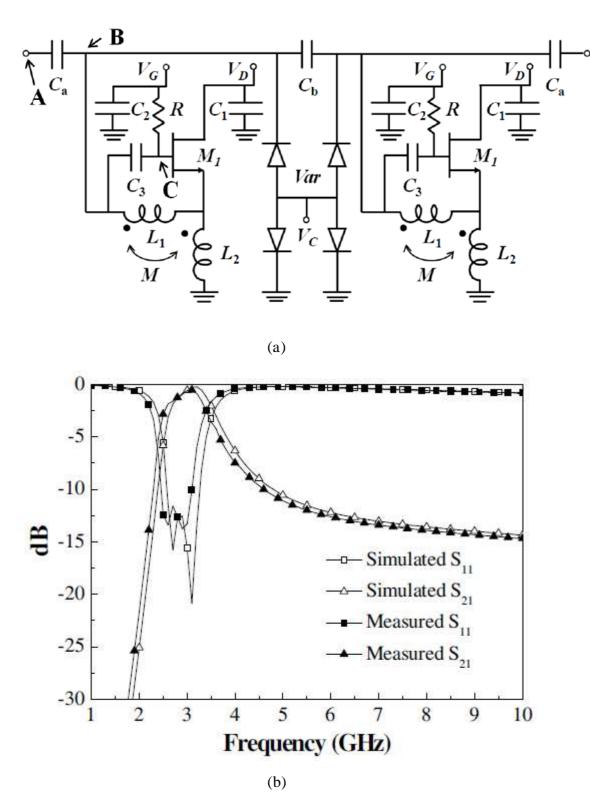

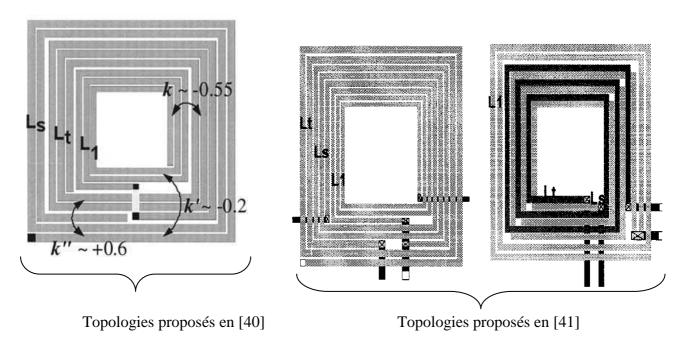

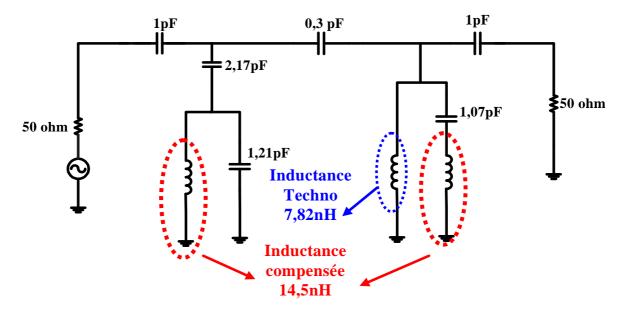

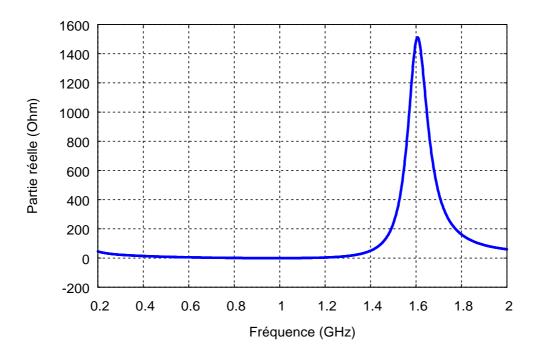

L'architecture de filtre utilisée dans ce travail de thèse est basée sur le principe de compensation des pertes à travers le couplage magnétique entre les inductances. Une étude bibliographique a permis de mettre à jour deux publications utilisant ce principe [40] [41]. Contrairement à la plupart des circuits présentés ci-dessus qui montrent des limitations lors de leur utilisation aux radiofréquences (consommation élevée, bruit important), la solution proposée dans ce manuscrit est basée sur le principe du couplage magnétique entre 3 inductances (Figure I-27). Ceci permet de réduire les pertes de l'inductance équivalente donc d'augmenter son facteur de qualité.

Figure I-27: Filtre LC passe bande basé sur le principe du couplage entre trois inductance

L'auteur dans la référence [40] présente un filtre LC d'ordre 1 basé sur ce principe.

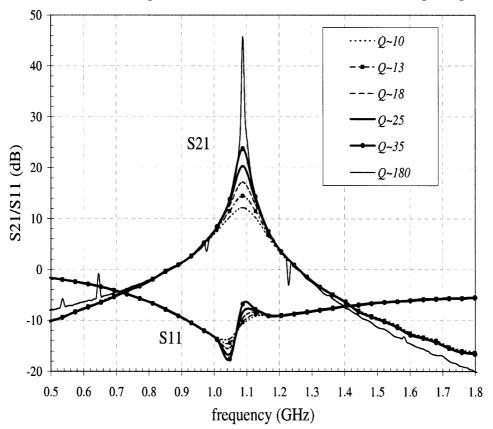

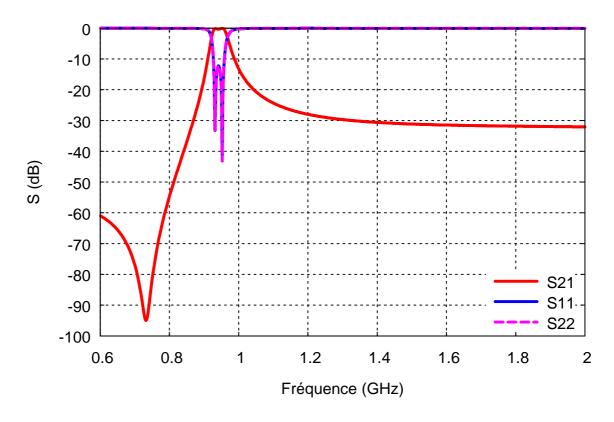

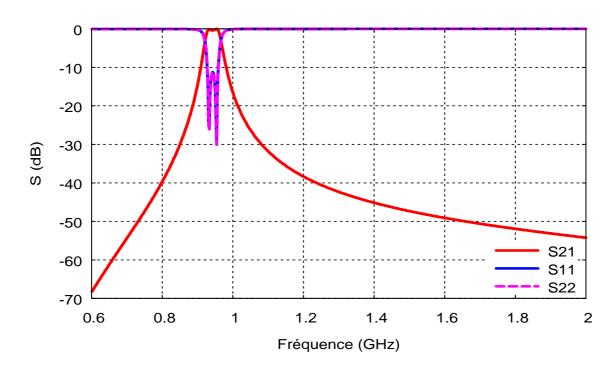

Figure I-28 : Réponse S21 et S11 du filtre

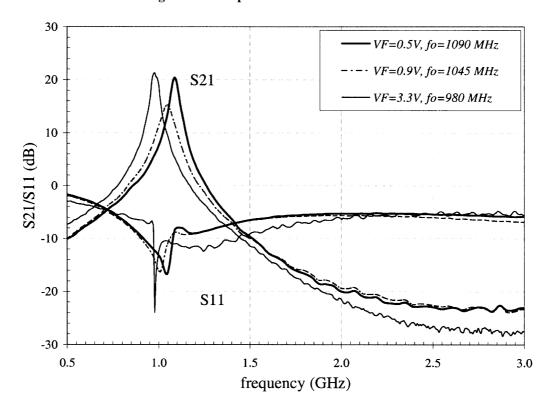

Figure I-29 : Réponse S21 et S11 avec balayage de la fréquence centrale

La Figure I-28 montre la fonction de filtrage (S21) et le facteur de qualité (Q) qui varie de 10 à 180 lorsque le générateur de tension de polarisation placé sur la source de transistor  $V_Q$  varie entre 0,7 à 1,5 V. La figure I-29 représente aussi la fonction du filtrage faisant apparaître un balayage fréquentiel de la fréquence centrale. La fréquence centrale varie de 980 MHz à 1090 MHz. Dans cette bande de fréquence le gain est de 20 dB.

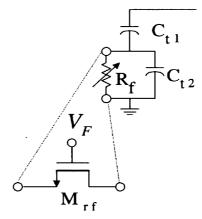

Ce balayage est commandé par le réseau ci-dessous :

Figure I-30 : Réseau du balayage en fréquence

Ce réseau est formé de deux capacités  $C_{t1}$  et  $C_{t2}$  et d'une résistance  $R_f$  (cf. Figure I-30). La résistance  $R_f$  est réalisée avec un transistor MOS  $(M_{rf})$ . La tension de polarisation  $V_F$  contrôle la valeur de  $R_f$ .

La Figure I-31 montre les possibilités d'implémentation du transformateur à trois inductances couplées proposées dans ces 2 articles.

Figure I-31: Topologies proposées

La difficulté principale pour la conception de ces circuits consiste à optimiser le transformateur avec un logiciel d'analyse électromagnétique tel que Momentum. Les inductances doivent avoir des facteurs de qualité élevés et être fortement couplées.

L'étude théorique de ce type de filtre ainsi le choix de la topologie des trois inductances couplées et le choix du réseau de balayage en fréquence sont détaillés dans les chapitres qui suivent. Un filtre LC à facteur de qualité compensé va être développé dans le troisième chapitre de cette thèse en technologie BiCMOS 0,25µm de NXP pour une application GSM 3G.

Le tableau I-3 résume les performances de filtres actif LC à facteur de qualité compensé.

|                            | [33] 2011  | [42] 2007   | [43] 2003  | [44] 2002   | [37] 2002   | [34] 1996   |

|----------------------------|------------|-------------|------------|-------------|-------------|-------------|

| Fréquence                  | 0,94-1,77  | 3,67        | 2,44       | 1,882       | 2,14        | 1,8         |

| centrale (GHz)             |            |             |            |             |             |             |

| Facteur                    | -          | 25-50       | -          | -           | -           | 3-350       |

| de qualité                 |            |             |            |             |             |             |

| Bande                      | -          | 35-90       | 100        | 150         | 60          | -           |

| passante (MHz)             |            |             |            |             |             |             |

| Ordre de filtre            | 1          | 6           | 3          | 4           | 3           | 3           |

| Consommation               | 22         | 72          | 3          | 18          | 7           | 8,7         |

| (mA)                       | Pour 2,5V  | Pour 1,8V   | Pour 1.8V  | Pour 3V     | Pour 2,5V   | Pour 2,8V   |

| Technologie                | 0,25       | 0,18        | 0,18       | 0,25        | 0,25        | 0,8         |

| (μm)                       | BiCMOS     | CMOS        | CMOS       | BiCMOS      | CMOS        | Bipolaire   |

| Réalisation et             |            |             |            |             |             |             |

| surface (mm <sup>2</sup> ) | Simulation | Réalisation | Simulation | Réalisation | Réalisation | Réalisation |

|                            |            | 0,81        |            | 7,14        | 3,51        | 0.38        |

|                            |            |             |            |             |             |             |

Tableau I-3 : Filtres actifs LC à facteur de qualité compensé

## IV. Conclusion

Dans ce chapitre nous avons présenté le rôle des filtres RF dans une chaine d'émission-réception. Nous avons également présenté les avantages et les inconvénients de différentes topologies déjà développées dans le domaine du filtrage actif. Le choix parmi ces topologies dépend des contraintes de filtrage, du gabarit, de la fréquence de travail, du coût et de l'encombrement pour l'application visée. Toutefois, nous remarquons que la topologie LC à facteur de qualité compensé est particulièrement intéressante en raison des avantages suivants : large bande de fréquence de fonctionnement, faible encombrement et consommation réduite, possibilité de régler la fréquence centrale.

## V. Références Bibliographiques

[1] B. Zheng, Z. Q. Zhao, and Y. X. Lv

"Design of wideband substrate integrated circular cavity(SICC) filter using  $TM_{01}$  mode coupling"

Progress In Electromagnetics Research Letters, Vol. 16, 79-87, 2010

#### [2] B. Lopez-Garcia, D.V.B. Murthy, A. Corona-Chavez

"Half mode microwave filters based on ep-silon near zero and mu near zero concepts"

Progress In Electromagnetics Research, Vol. 113, 379-393, 2011

#### [3] C.-F. Yang

"Design and fabrication of a compact quad-band bandpass filter using two different parallel positioned resonator"

Progress In Electromagnetics Research, Vol. 115, 159-172, 2011

#### [4] C.-M.Lin , T.-T.Wu ,Y.-Y. Chen

"Improved frequency responses of Saw Filters with interdigitated interdigital transducers on Zno/Diamond/Si layered structure"

Journal of Mechanics, Vol. 23, No. 3, September 2007

#### [5] W. B. Kuhn, D. Nobbe, D. Kelly, A. W. Orsborn

"Dynamic range performance of On-Chip RF Bandpass Filters"

IEEE Transactions on circuits and systems-IL:Analog and digital signal processing,Vol. 50, No. 10, October 2003

#### [6] **Z. Sassi**

"Etude et Conception de Structures de Filtrage Actif Radiofréquence Intégrées en Technologie CMOS et BiCMOS pour Application à la Téléphonie Cellulaire"

Thèse de Doctorat de l'Université de Limoges, Sept. 2006.

#### [7] F. BERGERAS

"Etude de nouvelles structures de filtres actifs intégrées en Hyperfréquences" Thèse de Doctorat de l'Université de Limoges, Décembre 2010.

#### [8] **J. M. Khoury**

"Design of a 15-MHz CMOS Continuous-Time Filter with On-Chip Tuning" IEEE journal of solid-state circuits, Vol. 26, No.12, December 1991

#### [9] R. Alini, A. Baschirotto, R. Castello

"Tunable BiCMOS Continuous-time Filter for High-Frequency Applications" IEEE journal of solid-state circuits, Vol. 27, No. 12, December 1992

#### [10] Z.-Yuan Chang, D. Haspeslagh, J. Verfaillie

"A Highly Linear CMOS – Bandpass Filter with On-Chip Frequency Tuning" IEEE journal of solid-state circuits, Vol. 32, No. 3, March 1997

#### [11] H. Shinichi, M. Tadashi, Y. Hitoshi, M. Noriaki, N. Keiichi

"A widely tunable CMOS Gm-C filter with a negative source degeneration resistor transconductors"

Proceedings of the 29th European Solid-State Circuits Conference, page(s):449-452, sept 2003.

#### [12] R. Thirugnanam, D. Sam Ha, B. Hyuk Park, Sang S. Choi

"Design of a Tunable Fully Differential GHz Range Gm-C Lowpass Filter in 0.18 μm CMOS for DS-CDMA UWB Transceivers"

IEEE International Symposium on, Circuits and systems, September 2006

#### [13] T.-Yu Lo, C.-Chih Hung

"A Wide Tuning Range Gm-C Continuous-Time Analog Filte"

IEEE Transactions on circuits and systems-I: regular papers, Vol. 54, No. 4, April 2007

#### [14] A. Kumar, P.E. Allen

"An 80MHz Noise Optimized ContinuousTime Bandpass Filter in 0.25μm BiCMOS" Custom Integrated Circuits Conference, 2007. CICC '07, .IEEE 16-19 Sept. 2007 Page(s):679 - 682.

#### [15] R. Gabriel Bozomitu, N. Cojan

"A VLSI Implementation of a new low voltage 5th Order Differential Gm-C Low-Pass Filter with Auto-tunning loop in CMOS technology"

Advances in electrical and computer engineering volume 11, Number 2011

#### [16] Wan Chuanchuan, Li Zhiqun, Hou Ningbing

"CMOS Gm-C complex filter with on-chip automatic tuning for wireless sensor network application"

Journal of semiconductors Vol. 32, No .5, May 2011

#### [17] S. DARFEUILLE

"Conception de Filtres Actifs Analogiques Radiofréquences Récursifs et Channélisés en Technologie Monolithique BiCMOS Silicium"

Thèse de Doctorat de l'Université de Limoges, Février 2006.

#### [18] **F.Yuan**

"CMOS Active Inductors and transformers Principle, Implementation, and Applications"

Springer Science + Business Media, 2008.

#### [19] K. LIANG, C. HO, C. KUO, Y. CHAN

"CMOS RF Band-pass Filter Design Using the High Quality Active Inductor" IEICE Tran.electron, vol.E88-C, No.12, December 2005.

#### [20] H. Ugur Uynaik. Nil Tarim

"Compact low voltage high-Q CMOS active inductor suitable for RF applications" Analog Integrated Circuits and Signal Processing, vol. 51, No. 3, pp. 191-194, Jun. 2007.

#### [21] M. Ebrahimzadeh

"A low voltage, High Quality Factor floating gate tunable active inductor with independent inductance and quality factor tuning"

International journal of computer and electrical engineering, Vol. 3, No. 2, April, 2011

#### [22] W. EL Hamdani, F. Temcamani, B. Delacresonnière, M. Alami, M. El Bekkali

"Nouvelle topologie d'un filtre passe-bande RF du 4ème ordre accordable à base d'inductances actives"

Mediterranean Telecommunication Journal vol. 1, n°1, 2011

#### [23] D. Cordova, J. De la cruz, C. Silva

"A 2.3-GHZ CMOS High-Q Bandpass Filter Design Using an Active Inductor" XV Workshop Iberchip, Buenos Aires-Argentina, 25-27 de Marzo de 2009

#### [24] G. Zhiqiang, Y. Mingyan, Y. Yizheng, M. Jianguo

"A CMOS RF Bandpass Filter Based on The Active Inductor"

ASICON the 6th International Conference On ASIC, Vol. 2, 24-27, page(s): 604-607 October 2005

## [25] X. Haiqiao, R. SchaumannS, W.R Daaasch, P.K. Wong, B. Pejcinovic

"A radio-frequency CMOS active inductor and its application in designing high-Q filters"

Proceedings of the International Symposium on Circuits and Systems,

Vol. 4, page(s): IV - 197-200, mai 2004

### [26] Y. Chang, J. Choma, J. Wills

"THE DESIGN AND ANALYSIS OF A RF CMOS BANDPASS FILTER"

IEEE International Symposium on circuits and systems, Geneva, Switzerland, May 2000

#### [27] C. Patrick Yue, , S. Simon Wong

"On-Chip Spiral Inductors with Patterned Ground Shields for Si-Based RF IC's"

IEEE journal of solid-state circuits, Vol. 33, No. 5, May 1998 74

# [28] Y. Cao, R. A. Groves, X. Huang, N. D. Zamdmer, J. Plouchart, R. A. Wachnik, T. King, C. Hu.

"Frequency-Independent Equivalent-Circuit Model for On-Chip Spiral Inductors"

IEEE journal of solid-state circuits, Vol. 38, No. 3, March 2003

## [29] S. Pei, Z. Wanrong, H. Lu, J. Dongyue, X. Hongyun

"Improving the quality factor of an RF spiral inductor with non-uniform metal width and non-uniform coil spacing"

Journal of Semiconductors, Vol. 32, No. 6, June 2011

#### [30] Y.-HO Cho, S.-Cheol Hong, Y.-Se Kwon

"A Low-Power Monolithic GaAs FET Bandpass Filter Based on Negative Resistance Technique"

IEEE microwave and guided wave letters, Vol. 8, No. 4, April 1998

#### [31] W. B. Kuhn, N. K. Yanduru, A. S. Wyszynski

"Q-Enhanced LC Bandpass Filters for Integrated Wireless Applications"

IEEE transactions on microwave theory and techniques, Vol. 46, No. 12, December 1998

#### [32] J. Tangenberg, E.A.M Klumperink, J.W. Th Eikenbroek, B. Nauta

"A CMOS Q-enhancement Bandpass-Filter for use in Paging Receivers"

In: Proceedings of the 9<sup>th</sup> IEEE/ProRISC Workshop on Circuits,Systems and signal Processing,1998

#### [33] L. Collot, J. Lintignat, B. Viala, D. Morche, J-P. Michel, B. Barelaud, B. Jarry

"Reconfigurable Filtering Differential Low Noise Amplifier Using MEMS tunable Inductor"

Microwave Conference (EuMC), 2010 European

### [34] S. Pipilos, Y. P. Tsividis, J. Fenk, Y. Papananos

"A Si 1.8 GHz RLC Filter with Tunable Center Frequency and Quality Factor"

IEEE journal of solid-state circuits, Vol. 31, No. 10, October 1996

#### [35] R. A. Duncan, K. W. Martin, A. S. Sedra

"A Q-Enhanced Active-RLC Bandpass Filter"

Department of Electrical and Computer Engineering University of Toronto Ontario CANADA M5S 1A4 1993 IEEE

#### [36] D.Li, Y. Tsividis

"Active LC filters on silicon"

IEEE Proc-Circuits Devices Syst, Vol. 147, No. I. February 2000

#### [37] T. Soorapanth, S. Wong

"A 0 dB IL 2140 ±30MHz Bandpass Filter utilizing Q-enhanced spiral inductors in standard CMOS"

IEEE J. Solid-State Circuits, vol. 37, No. 5, MAY 2002.

#### [38] J. Kulyk, J. Haslett

"A Monolithic CMOS 2368±30 MHz Transformer Based Q-Enhanced Series-C Coupled Resonator Bandpass Filter"

IEEE journal of solid-state circuits, Vol. 41, No. 2, February 2006

#### [39] S. Wang, R.X. Wang

"A tunable bandpass filter using q-enhanced and semi-passive inductors at S-band in 0.18-um CMOS"

Progress In Electromagnetics Research B, Vol. 28, 55-73, 2011

#### [40] S. Bantas, Y. Koutsoyannopoulos

"CMOS Active-LC Bandpass Filters with Coupled-Inductor Q-Enhancement and Center Frequency tuning"

IEEE transactions on circuits and systems, vol.51, n° 2, February 2004.

#### [41] S. Bantas, Y. Papananos, Y. Koutsoyannopoulos

"CMOS tunable bandpass RF filters utilizing coupled on-chip inductors"

In Proc. ISCAS'99, vol. 2, Orlando, FL, June 1999, pp. 581–584.

#### [42] A. Dinh, J. Ge

"A Q-Enhanced 3.6 GHz, Tunable, Sixth-Order Bandpass Filter Using 0.18 μm CMOS" Research Article ID 84650 Volume 2007

#### [43] B. Georgescu, H. Pekau, J. Haslett and J. McRory

"Tunable Coupled Inductor Q-Enhancement for Parallel Resonant LC Tanks"

IEEE Transactions on circuits and systems-II: analog and digital signal processing, Vol. 50, No. 10, October 2003

#### [44] D. Li, Y. Tsividis

"Design Techniques for Automatically Tuned Integrated Gigahertz-Range Active LC Filters"

IEEE J. Solid-State Circuits, vol. 37, NO. 8, AUGUST 2002.

Chapitre II : Inductance compensée à trois inductances couplées et modélisation du transformateur en technologies CMOS 65 nm et BiCMOS 0,25 µm

# I. Introduction

L'utilisation, en technologie MMIC d'une inductance passive dans des structures performantes de filtrage radiofréquence et microonde rencontre plusieurs problèmes tels que :

- La difficulté de réaliser des inductances de fortes valeurs,

- L'impossibilité de faire varier "électriquement" la valeur de l'inductance,

- Sa dimension géométrique importante,

- L'impossibilité de réaliser des inductances sans pertes (faible facteur de qualité).

Ces dernières caractéristiques empêchent la réalisation de filtres passifs intégrés très sélectifs. Plusieurs techniques ont été utilisées pour résoudre ces problèmes présentant des topologies d'inductances actives (gyrateurs) ou bien des topologies d'inductances compensées (inductances passives compensées par une résistance négative). Malheureusement, ces solutions montrent toujours des limitations lors de leur utilisation aux radiofréquences comme une consommation en courant élevée et une dégradation en bruit et en linéarité. Ces travaux de thèse portent sur la conception d'une nouvelle méthode de compensation des pertes à travers le couplage magnétique entre trois inductances qui permet de réduire les pertes de l'inductance équivalente et donc d'augmenter son facteur de qualité. Cette technique utilise un seul transistor commandé en tension et permet de réduire la consommation du circuit global.

Dans la première partie de ce chapitre, nous présentons cette nouvelle topologie d'inductance compensée utilisant un transformateur à trois inductances couplées, ainsi que le dessin du transformateur.

Dans la deuxième partie, nous détaillons la méthodologie de modélisation électrique développée pour le transformateur réalisé en technologies CMOS 65 nm et BiCMOS 0,25  $\mu$ m de NXP.

Enfin, la troisième partie est consacrée à la recherche des architectures de types passe bande utilisant l'inductance compensée.

## II. Conception de l'inductance compensée

## II.1. Principe de fonctionnement

#### II.1.1. Introduction

La conception de l'inductance compensée s'inspire des références [1], [2] et [3]. Cette nouvelle architecture consiste à mettre en œuvre un transformateur à trois inductances couplées associé à un transistor de compensation.

Pour comprendre le principe de fonctionnement de ce circuit, nous commençons par étudier le concept du couplage entre deux inductances, puis nous analysons l'association transformateur-transistor de compensation afin de trouver la condition permettant d'améliorer le facteur de qualité de l'inductance compensée.

#### II.1.2. Concept du couplage entre deux inductances

Les deux grandeurs caractéristiques qui quantifient le couplage entre deux inductances couplées sont le facteur de couplage k et la mutuelle inductance M. Pour deux inductances couplées de valeurs L1 et L2, k et M sont reliés par la relation suivante :

$$k = \frac{M}{\sqrt{L_1 L_2}}$$

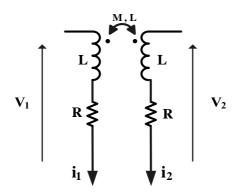

Afin de simplifier le calcul, nous supposons que les deux inductances sont identiques de valeur L et de résistances de pertes R (cf. Figure II-1).

Figure II-1: Deux inductances couplées

Les relations entre les courants et les tensions dans les deux branches sont définies:

$$V_1 = (R + jL\omega)i_1 + jM\omega i_2$$

(II-1)

$$V_2 = (R + jL\omega)i_2 + jM\omega i_1$$

L'expression de l'impédance d'entrée est alors :

$$Z_{in} = \frac{V_1}{i_1} = jL\omega + R + jM\omega \frac{i_2}{i_1}$$

(II-2)

On pose :  $\alpha + j\beta = \frac{i_2}{i_1}$  et M = kL (II-3)

En remplaçant (II-3) dans (II-2), l'expression de Z<sub>in</sub> peut être exprimée comme suit :

$$Z_{in} = R - \beta k L \omega + j \omega L (1 + \alpha k)$$

(II-4)

A partir de (II-4), nous trouvons les expressions de l'inductance effective  $L_{\text{eff}}$  et la résistance effective  $R_{\text{eff}}$ :

$$L_{\rm eff} = L(1 + \alpha k) \tag{II-5}$$

$$R_{eff} = R - \beta k L \omega$$

(II-6)

Le facteur de qualité à vide  $Q_0$  de chaque inductance est égal à :

$$Q_0 = \frac{L\omega}{R} \Rightarrow L\omega = RQ_0$$

(II-7)

L'expression de la résistance effective (II-6) est alors :

$$R_{eff} = R(1 - \beta k Q_0)$$

(II-8)

Le facteur de qualité effective est donné par la relation :

$$Q_{\text{eff}} = \frac{L_{\text{eff}}\omega}{R_{\text{eff}}} = \frac{\omega L(1 + \alpha k)}{R(1 - \beta k Q_0)}$$

(II-9)

A partir de l'expression (II-9), on retrouve les deux conditions pour lesquelles le facteur de qualité  $Q_{\text{eff}}$  est maximum :

| Conditions | α   | k   | β                         | R <sub>eff</sub> et L <sub>eff</sub>       | Q <sub>eff</sub>   |

|------------|-----|-----|---------------------------|--------------------------------------------|--------------------|

| 1          | α>0 | k>0 | $0<\beta<(kQ_0)^{-1}$     | $R_{eff}\downarrow$ et $L_{eff}\uparrow$   | Q <sub>eff</sub> ↑ |

| 2          | α<0 | k<0 | $(kQ_0)^{-1} < \beta < 0$ | $R_{eff} \downarrow$ et $L_{eff} \uparrow$ | Q <sub>eff</sub> ↑ |

Tableau II-1 : Valeurs de α, k et β pour que Q<sub>eff</sub> soit maximum

#### II.1.3. Inductance compensée à trois inductances couplées

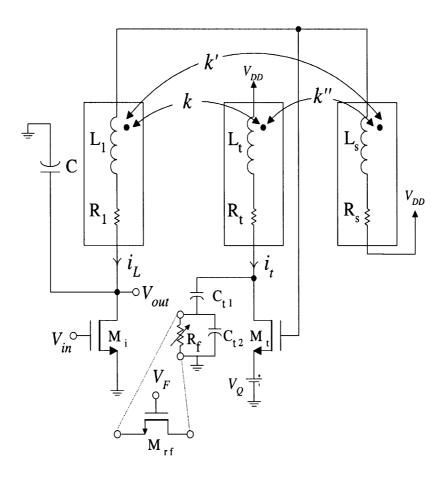

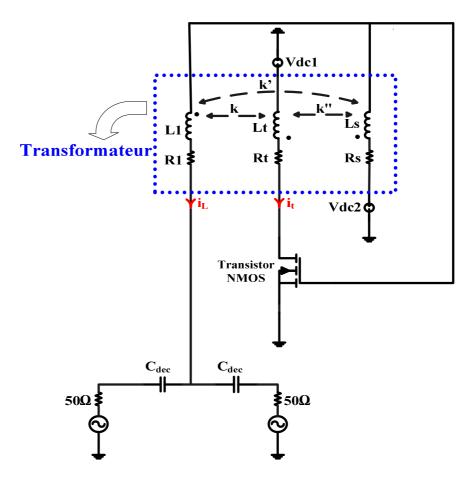

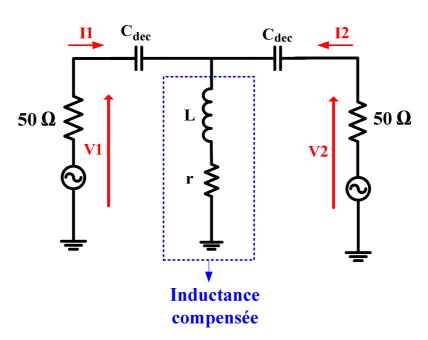

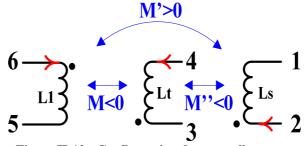

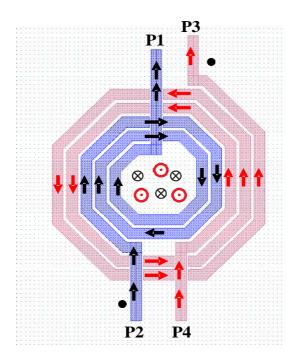

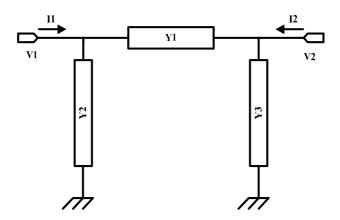

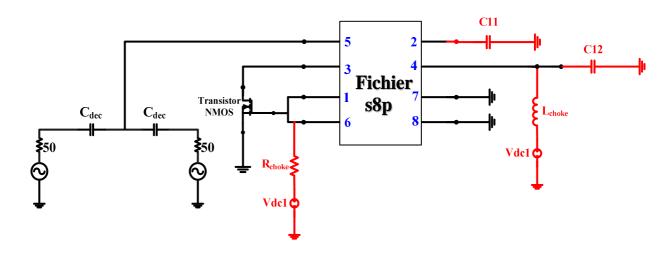

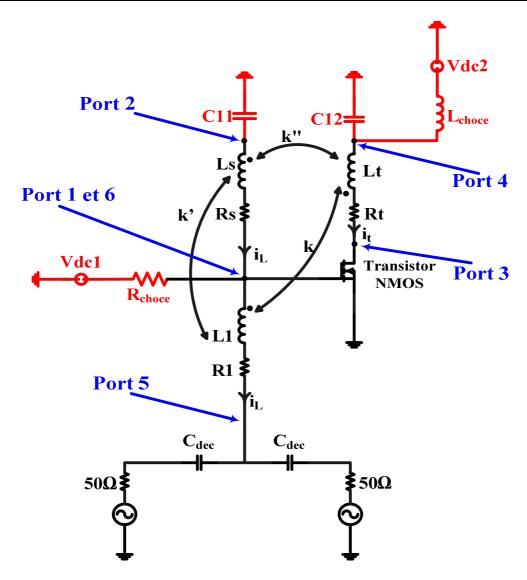

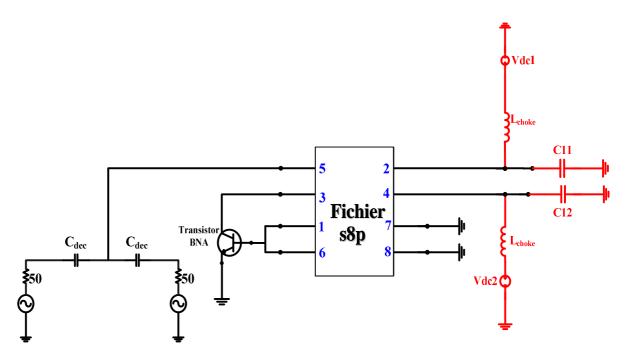

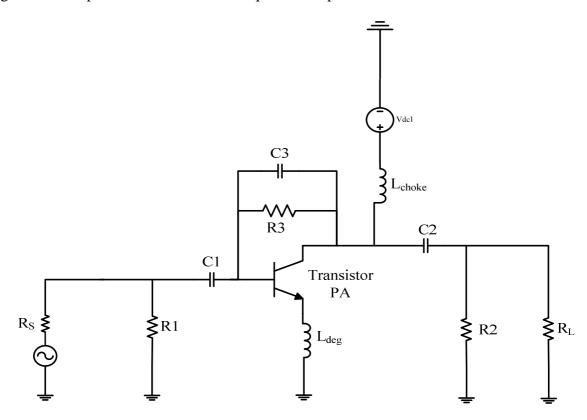

Le schéma de l'inductance compensée est représenté sur la Figure II-2. Elle est composée de deux parties. La première partie est la partie passive constituée d'un transformateur à 3 inductances couplées *L1,Lt et Ls*. Pour ce transformateur, k représente le coefficient de couplage entre *L1* et *Lt*, k' celui entre *L1* et *Ls* et k'' entre *Lt* et *Ls*. La deuxième partie est constituée d'un transistor NMOS dans le cas de la technologie CMOS 65nm ou bipolaire dans le cas de la technologie BiCMOS QuBIC4X. Ce transistor joue le rôle d'une source de courant commandée par les tensions Vdc1 et Vdc2. De plus, les capacités «Cdec » sont ajoutées pour découpler le courant continu.

Figure II-2 : Schéma de l'inductance compensée

## II.1.3.1. <u>Inductance compensée utilisant un transistor NMOS</u>

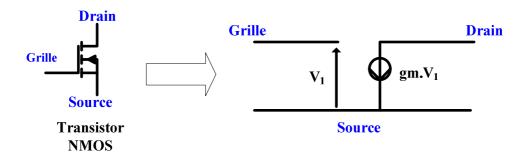

A l'aide du modèle petit signal du transistor à effet de champ NMOS illustré dans la Figure II-3, nous pouvons analyser le comportement petit signal de l'inductance compensée comme montré sur la Figure II-4.

Figure II-3 : Schéma petit signal du transistor NMOS

Figure II-4 : Circuit petit signal de l'inductance compensée

En analysant le circuit de la Figure II-4, nous pouvons considérer le circuit comme une structure composée de deux branches (similaire au cas de la Figure II-1). Une branche est constituée de l'inductance principale formée par L1 et Ls et l'autre est constituée de l'inductance de compensation Lt.

Pour déterminer la partie réelle ( $R_{eff}$ ), la partie imaginaire ( $L_{eff}$ ) ainsi que le facteur de qualité ( $Q_{eff}$ ) de l'inductance compensée, nous supposons que les trois inductances possèdent une valeur identique L (L1=Lt=Ls=L), et une résistance de perte identique R (R1=Rt=Rs=R). De plus, on suppose négligeable le courant de grille du transistor NMOS.

La tension en entrée V de la Figure II-4 est donnée par la relation :

$$V = (2j\omega L + 2R + 2j\omega M')i_{L} + jM''\omega i_{t} + jM\omega i_{t}$$

(II-10)

En divisant l'expression (II-10) par le courant  $i_L$  et en posant  $\alpha + j\beta = \frac{i_t}{i_L}$ , nous retrouvons

l'expression de l'impédance d'entrée de l'inductance compensée comme suit :

$$\frac{V}{i_L} = 2R - M''\omega\beta - M\omega\beta + j\omega(2L + 2M' + M''\alpha + M\alpha)$$

(II-11)

On a:

$$M = kL \text{ et } Q_0 = \frac{L\omega}{R}$$

(II-12)

En remplaçant (II-12) dans (II-11), on retrouve l'expression finale de l'impédance effective :

$$Z_{\text{eff}} = R(2 - k''Q_0\beta - kQ_0\beta) + j\omega L(2 + 2k' + \alpha k'' + \alpha k)$$

(II-13)

Le circuit est donc équivalent à une inductance simple accès reliée à la masse. Elle est composée d'une inductance idéale de valeur  $L_{\rm eff}$  en série avec une résistance de valeur  $R_{\rm eff}$ .

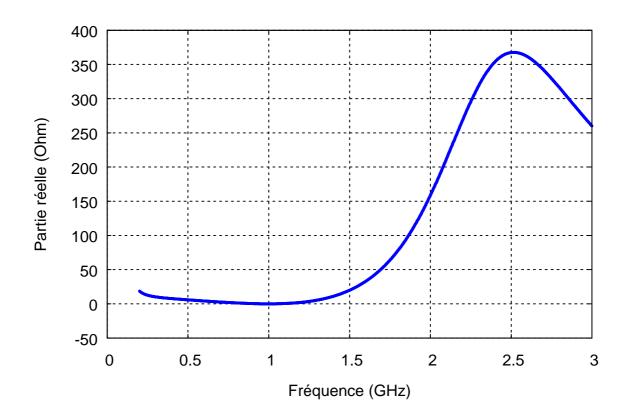

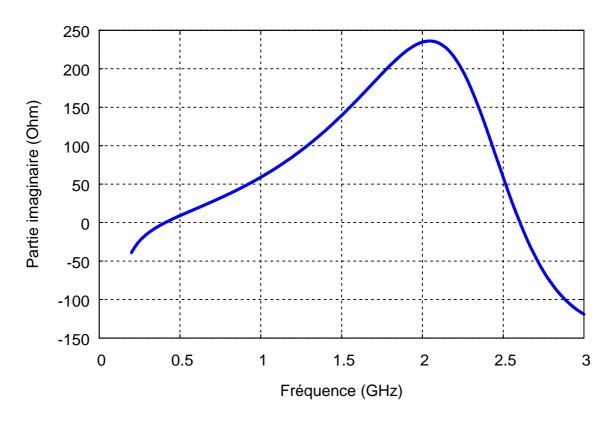

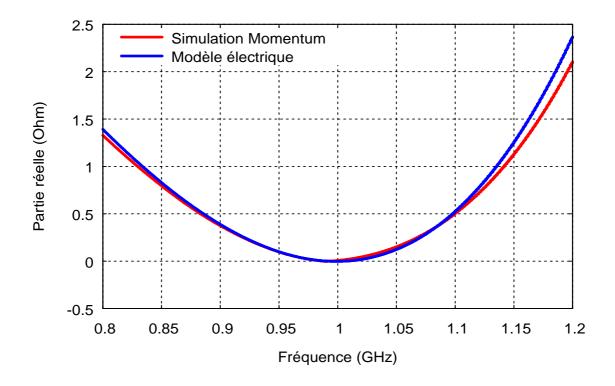

Les expressions de L<sub>eff</sub>, R<sub>eff</sub> et Q<sub>eff</sub> sont les suivantes :

$$\begin{split} L_{\rm eff} &= L(2+2k'\!+\!\alpha k''\!+\!\alpha k) \\ R_{\rm eff} &= R(2-k''Q_0\beta\!-\!kQ_0\beta) \\ Q_{\rm eff} &= \frac{L_{\rm eff}\omega}{R_{\rm eff}} = \frac{L\omega(2+2k'\!+\!\alpha k''\!+\!\alpha k)}{R(2\!-\!k''Q_0\beta\!-\!kQ_0\beta)} \end{split} \tag{II-14}$$

A partir de l'expression (II-14), on retrouve la condition pour laquelle le facteur de qualité  $Q_{\text{eff}}$  est maximum :

|           | α et β   | Coef. de couplages | R <sub>eff</sub> et L <sub>eff</sub>     | $Q_{\mathrm{eff}}$ |

|-----------|----------|--------------------|------------------------------------------|--------------------|

| Condition | α<0, β<0 | k<0, k''<0 et k'>0 | $R_{eff} \downarrow et L_{eff} \uparrow$ | Q <sub>eff</sub> ↑ |

Tableau II-2: Condition pour que Qeff soit maximum

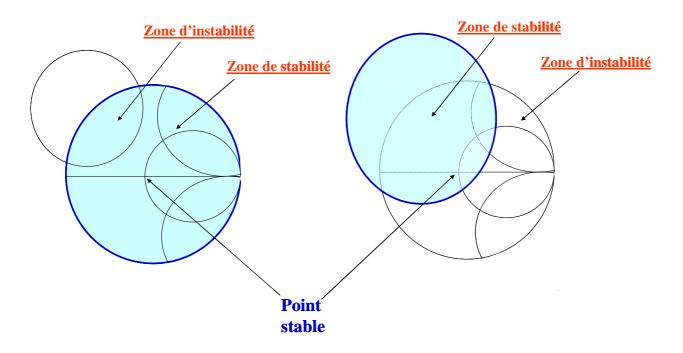

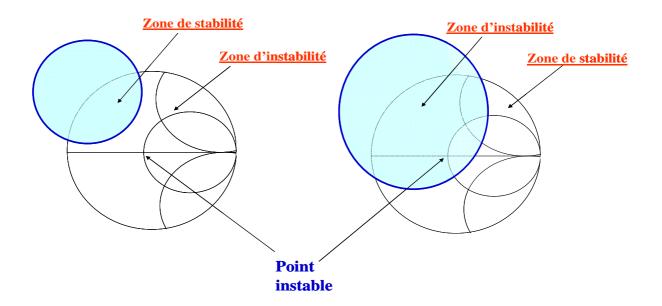

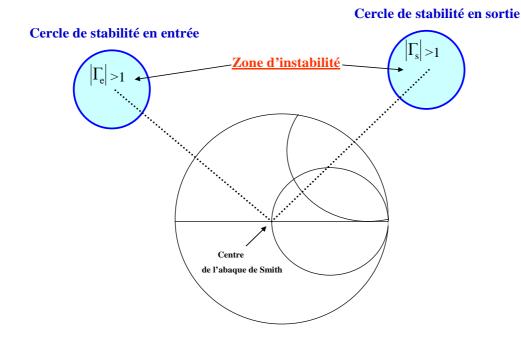

Pour assurer la stabilité du circuit, il faut que le dénominateur de l'expression (II-14) soit toujours positif. Ceci implique que le circuit est stable si  $\beta$  respecte la condition suivante :

$$k''Q_0\beta + kQ_0\beta < 2$$

$$\Rightarrow |\beta| < \frac{2}{Q_0(k''+k)}$$

(II-15)

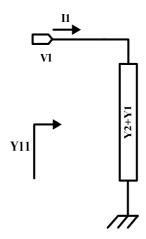

Les parties réelle ( $R_{eff}$ ) et imaginaire ( $L_{eff}$ ) de l'inductance compensée sont déduites de l'analyse du montage de la Figure II-5 :

$$Z11 = \frac{V1}{I1}\Big|_{I2=0} = R_{eff} + j\omega L_{eff}$$

Figure II-5 : Inductance compensée à deux ports

Afin de concevoir un résonateur LC, cette inductance compensée peut être associée à une capacité C. La fréquence de résonance f<sub>0</sub> du résonateur est donnée par l'expression suivante :

$$f_0 = \frac{1}{2\pi\sqrt{L_{eff}C}} = \frac{1}{2\pi\sqrt{LC(2+2k'+\alpha k''+\alpha k)}}$$

(II-16)

On remarque d'après la relation (II-16) que  $f_0$  est fonction du facteur  $\alpha$  et ne dépend pas de  $\beta$ . De plus, la résistance effective  $R_{eff}$  (équation II-14) ne dépend que de  $\beta$ . Donc la compensation des pertes est assurée en faisant varier  $\beta$ .

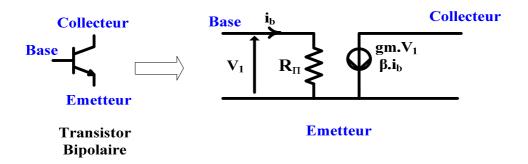

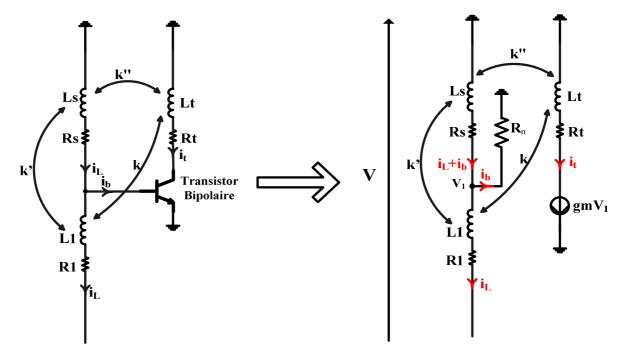

#### II.1.3.2. Inductance compensée avec un transistor bipolaire

Dans le cas de l'inductance compensée utilisant un transistor bipolaire de compensation le calcul est similaire. Le schéma équivalent petit signal du transistor est présenté sur la Figure II-6 et le circuit équivalent petit signal de l'inductance compensée est montré dans la Figure II-7.

Figure II-6 : Schéma petit signal du transistor

Figure II-7 : Schéma petit signal de l'inductance compensée

Le courant  $i_L$  est très supérieur à  $i_b$  (donc  $i_L+i_b\approx i_L$ ) et la résistance  $R_\pi$  est de forte valeur, on obtient donc les mêmes équations que celles trouvées précédemment pour l'inductance  $L_{eff}$  et la résistance  $R_{eff}$  ainsi que la condition conduisant à obtenir  $Q_{eff}$  maximum:

$$L_{eff} = L(2 + 2k' + \alpha k'' + \alpha k)$$

$$R_{eff} = R(2 - k''Q_0\beta - kQ_0\beta)$$

$$Q_{\text{eff}} = \frac{L_{\text{eff}}\omega}{R_{\text{eff}}} = \frac{L\omega(2+2k'+\alpha k''+\alpha k)}{R(2-k''Q_0\beta-kQ_0\beta)}$$

|           | α et β   | Coef.de couplages  | R <sub>eff</sub> et L <sub>eff</sub>     | $Q_{ m eff}$       |

|-----------|----------|--------------------|------------------------------------------|--------------------|

| Condition | α<0, β<0 | k<0, k''<0 et k'>0 | $R_{eff} \downarrow et L_{eff} \uparrow$ | Q <sub>eff</sub> ↑ |

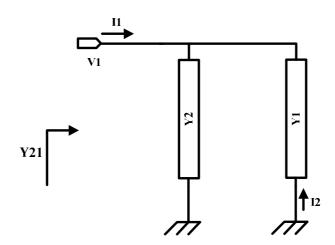

#### II.1.3.3. Calcul des paramètres α et β

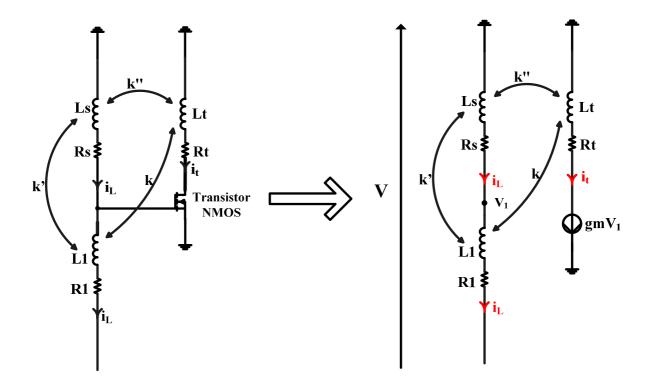

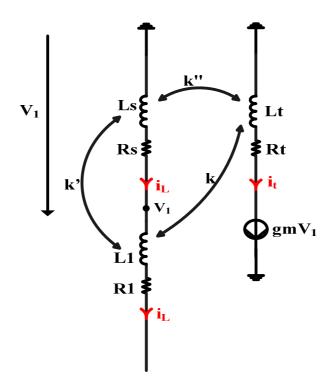

Pour calculer les valeurs des facteurs  $\alpha$  et  $\beta$  qui représentent la partie réelle et imaginaire du rapport des courants  $i_t$  et  $i_L$  dans les deux branches  $(\alpha + j\beta = i_t/i_L)$  nous analysons le circuit de la Figure II-8.

Figure II-8 : Schéma équivalent petit signal de l'inductance compensée

L'analyse du circuit donne :

$$V_{1} = -(jL\omega + R)i_{L} + jM'\omega i_{L} + jM''\omega i_{t}$$

(II-17)

En divisant l'expression (II-17) par i<sub>t</sub>, on obtient l'expression suivante :

$$\frac{V_1}{i_*} = \frac{i_L}{i_*} (-jL\omega - R + jM'\omega) + jM''\omega$$

(II-18)

Et:

$$i_t = g_m V_1 \Rightarrow \frac{V_1}{i_t} = \frac{1}{g_m}$$

(II-19)

$$M = kL$$

,  $M' = k'L$  et  $M'' = k''L$  (II-20)

En utilisant les expressions (II-18), (II-19) et (II-20), on retrouve l'expression finale du rapport entre les deux courants  $i_t$  et  $i_L$ :

$$\frac{i_{t}}{i_{L}} = \frac{L^{2}k''\omega^{2}g_{m}^{2} - g_{m}R - g_{m}^{2}k'k''L^{2}\omega^{2} + j(-L\omega g_{m} - Rk''L\omega g_{m}^{2} + k'L\omega g_{m})}{1 + g_{m}^{2}\omega^{2}k''^{2}L^{2}}$$

(II-21)

On a:

$$\frac{i_t}{i_L} = \alpha + j\beta$$

Alors:

$$\alpha = \frac{-g_{\rm m}R + L^2\omega^2 k'' g_{\rm m}^2 (1 - k')}{1 + g_{\rm m}^2 \omega^2 k''^2 L^2}$$

(II-22)

Et

$$\beta = \frac{-L\omega g_{m}(1-k') - Rk''L\omega g_{m}^{2}}{1 + g_{m}^{2}\omega^{2}k''^{2}L^{2}}$$

(II-23)

Si on considère que  $g_m << 1 \text{ A/V}$ :

L'équation (II-23) devient alors :

$$|\beta| = L\omega g_{m}(1-k') \tag{II-24}$$

La nouvelle condition de stabilité (II-15) est alors exprimée comme suit (II-25) :

$$L\omega g_{m}(1-k') < \frac{2}{Q_{0}(k''+k)}$$

$$\Rightarrow g_{\rm m} < \frac{2}{\omega LQ_0(1-k')(k''+k)}$$

(II-25)

Cette expression montre que la transconductance  $g_m$  du transistor est inversement proportionnelle au facteur de qualité de chaque inductance  $(Q_0)$  et aux coefficients de couplages entre les trois inductances, c'est-à-dire au facteur  $Q_0(1+|k|)(|k||+|k|)$ . Ceci nous permet de mettre en évidence une méthodologie pour minimiser la consommation de l'inductance compensée :

- Concevoir les inductances (L1, Lt, Ls) pour avoir un fort facteur de qualité  $Q_0$ ,

- Maximiser le couplage entre les inductances.

#### II.2. Layout du transformateur

#### II.2.1. Paramètres géométriques

La difficulté principale dans la conception de l'inductance compensée consiste à optimiser le transformateur avec un logiciel d'analyse électromagnétique tel que Momentum de ADS [1] [3].

Il existe de multiples possibilités pour réaliser un transformateur. Le choix de la géométrie dépend des paramètres suivants : le facteur de qualité des inductances, le coefficient de couplage entre les inductances, la valeur des inductances, la surface occupée et enfin la fréquence de résonance des inductances.

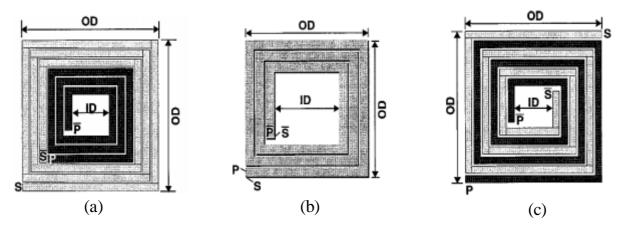

La Figure II-9 présente les trois possibilités d'implémentation des transformateurs les plus couramment utilisées dans la littérature [9].

Figure II-9 : Géométries des transformateurs

Nous résumons dans le tableau II-3 les caractéristiques de ces trois géométries.

|     | Surface | Coefficient   | Valeur          | Fréquence de |

|-----|---------|---------------|-----------------|--------------|

|     |         | de couplage k | de l'inductance | résonance    |

| (a) | élevée  | Faible        | moyenne         | élevée       |

| (b) | faible  | élevé         | élevée          | faible       |

| (c) | élevée  | moyen         | faible          | élevée       |

Tableau II-3 : Caractéristiques des trois topologies

D'après ce tableau nous remarquons qu'il n'existe pas de solution idéale et l'optimisation du transformateur se fera suivant le type d'application et la fréquence de travail souhaitée. Dans notre conception, nous avons choisi la première topologie (topologie (a)) parce qu'elle présente trois avantages : les inductances peuvent être réalisées avec le niveau de métallisation le plus éloigné du substrat afin de minimiser les pertes, la possibilité de réaliser de fortes valeurs d'inductances et finalement une fréquence de résonance pour chaque inductance élevée.

Dans le chapitre I nous avons démontré l'importance du facteur de qualité de l'inductance pour concevoir un filtre LC. L'objectif de ce paragraphe est de trouver la meilleure géométrie du transformateur à trois inductances couplées afin d'obtenir un facteur de qualité élevé de l'inductance compensée. Certaines lignes directrices pour le dessin des inductances sont utilisées [4] [5] [13] et sont les suivantes :

- **Séparation entre les lignes :** A basse fréquence (à 2 GHz ou moins), l'espacement entre les lignes doit être fixé à une valeur minimale (la mutuelle inductance diminue lorsque l'espacement entre les lignes augmente). A des fréquences plus élevées (>2GHz) et en raison du couplage entre les tours de l'inductance, un espacement plus grand est souhaitable.

- Niveaux de métallisations : Il est préférable d'utiliser le niveau de métallisation le plus éloigné du substrat. La raison est double : il est plus épais donc moins résistif et son éloignement du substrat minimise les effets capacitifs.

- **Géométrie de l'inductance :** La géométrie circulaire présente le facteur de qualité le plus élevé. Cependant, le dessin de ces inductances prend du temps et est difficile à modifier. Ceci nous conduit à utiliser des inductances de forme octogonale.

- Largeur des lignes : Plus une ligne est large, plus sa résistivité est faible. Il est donc nécessaire d'utiliser des lignes de largeur importante.

- **Surface :** Une grande surface contribue à augmenter l'effet des éléments parasites et à générer des pertes de substrat hautes fréquences plus importantes. Une inductance occupant une grande surface simule une inductance de forte valeur mais les effets capacitifs accentués vont diminuer la fréquence de résonance de l'inductance.

- Nombre de tours : Il est généralement préférable de choisir un nombre minimum de tours à condition que la valeur de l'inductance ne soit pas trop importante. Les tours

internes (au centre de l'inductance) contribuent moins à la valeur de l'inductance il est donc préférable de laisser le centre de l'inductance "vide".

• Plan de masse: Afin d'éviter les pertes dues au substrat silicium, nous utilisons un écran électrostatique ou « Shield » en anglais. Cet écran est utilisé sous l'inductance et il est composé de plusieurs barreaux conducteurs parallèles. Ces barreaux sont reliés à la masse et ils sont placés perpendiculairement aux lignes métalliques des trois inductances afin d'éliminer le courant qui se déplace dans le substrat, et donc de minimiser la résistance qui modélise le substrat dans les modèles en Pi.

#### II.2.2. Sens des enroulements et dessin du transformateur

Le coefficient d'inductance mutuelle peut être négatif ou positif compte tenu des deux facteurs suivants :

- Le sens positif des courants dans les inductances (choisi arbitrairement)

- Le sens du bobinage des enroulements.

La démarche de conception des trois inductances couplées comporte les étapes suivantes :

**Etape1**: Choix du sens des courants dans les inductances.

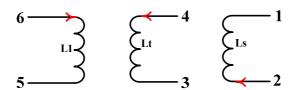

On suppose que le courant circule dans les inductances, comme illustré dans la Figure II-10.

Figure II-10: Choix du sens des courants

**Etape 2 :** Choix du sens du bobinage.

Pour ce choix il faut qu'on respecte la condition trouvée dans le tableau II-2:

$$k<0$$

,  $k''<0$  et  $k'>0$

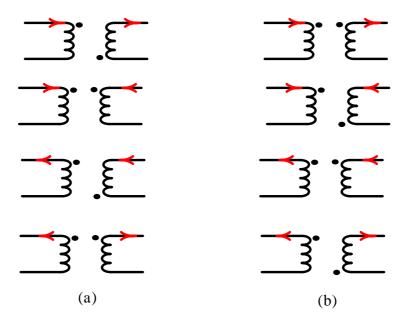

Pour cela on représente sur la Figure II-11 le signe de M:

- Quand M est positif (k>0), les flèches indiquant les sens positifs de circulation des courants sont placées de la même façon par rapport aux deux points indiquant les sens des enroulements (dans le sens ou dans le sens inverse des aiguilles d'une montre).

- Quand M est négatif (k<0), les flèches indiquant les sens positifs de circulation des courants sont placées de façon différente par rapport aux points indiquant les sens des enroulements.

Figure II-11 : Représentation du signe de la mutuelle inductance M. (a) M>0 : Les 2 courants entrent (sortent) du coté des points. (b) M<0 : Un courant entre, l'autre sort du coté des points.

La configuration choisie est représentée sur la figure II-12.

Figure II-12: Configuration des mutuelles

#### **Etape 3 :** Dessin du transformateur

A partir de la Figure II-12 nous commençons le dessin du transformateur. La Figure II-13 représente le principe du couplage entre l'inductance *Ls* et l'inductance *Lt*. Le flux dans l'inductance *Lt* est de sens contraire à celui crée dans l'inductance *Ls*; les deux flux se

retranchent et la mutuelle inductance entre les deux inductances est alors négative. Les deux points en noir indiquent le sens des enroulements. Ils sont placés à côté du port où le courant entre dans l'inductance dans le cas où le bobinage est dans le sens des aiguilles d'une montre. Dans le cas où le bobinage est dans le sens inverse des aiguilles d'une montre le point est à côté du port où le courant sort de l'inductance. Cela est montré sur la Figure II-13.

Figure II-13 : Principe du couplage entre l'inductance Lt et Ls

Le cas est similaire pour l'inductance L1 et Lt (Figure II-14 (a)).Donc M est négatif.

Figure II-14: Principe du couplage (a) entre L1 et Lt (b) entre L1 et Ls

Dans le cas de la Figure II-14 (b) le flux dans l'inductance L1 a le même sens que le flux crée par l'inductance Ls; les deux flux s'ajoutent donc M est positif.

# II.2.3. <u>Présentation des deux technologies utilisées dans cette thèse et layout des transformateurs</u>

Dans cette thèse et dans le cadre du programme SRAMM deux processus technologiques de NXP sont utilisés. Les technologies CMOS 65nm et BiCMOS 0,25 μm. Par souci de simplicité il a été successivement décidé de développer une application en CMOS à 2 GHz (UMTS) puis une application à 1GHz (GSM) en BiCMOS SiGe. Nous présentons ici les inductances compensées conçues dans ce cadre.

#### II.2.3.1. La technologie CMOS 65 nm

La technologie CMOS 65 nm comprend cinq procédés de fabrication permettant d'optimiser la conception selon l'application visée. Les cinq procédés sont les suivants : CLN65G, CLN65GP, CLN65LP, CLN65LPG, CLN65ULP. Le procédé qui nous intéresse est le CLN65LP. Ce procédé est dédié aux applications de type basse consommation (procédé Low-Power) : tension d'alimentation VDD =1,2 V, épaisseur de l'oxyde de grille Tox = 1,8 nm, longueur de grille Lg=65nm. Cette technologie offre sept niveaux de métallisation parmi lesquels deux sont épais (M6-M7). Concernant les inductances, plusieurs géométries sont disponibles (carrée, octogonale symétrique).

#### II.2.3.2. La technologie BiCMOS 0,25 µm

La technologie BiCMOS QUBIC4X comporte des transistors PMOS et NMOS de longueur de grille 0,25µm et des transistors bipolaires avec une fréquence de transition de 140 GHz. Cette technologie de type SiGe:C offre cinq niveaux de métallisation, des capacités MIM, des capacités variables (Varicap) et plusieurs types de résistances. Ce procédé permet de supporter des tensions d'alimentations comprises entre 1V et 2,5V.

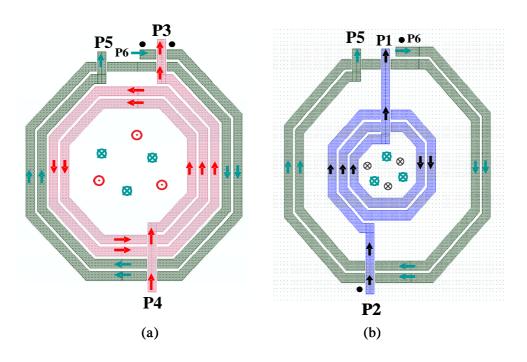

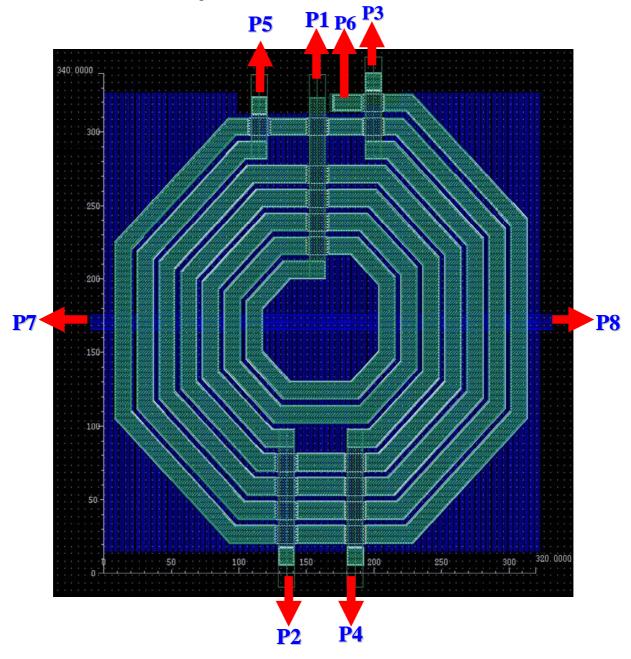

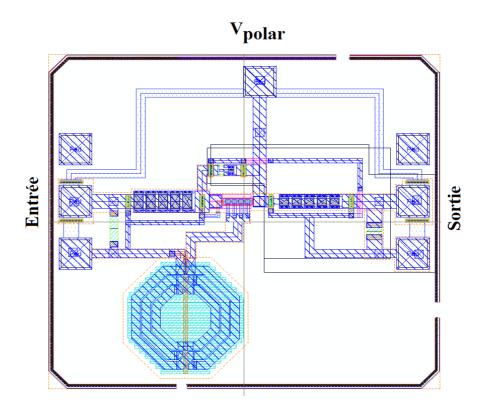

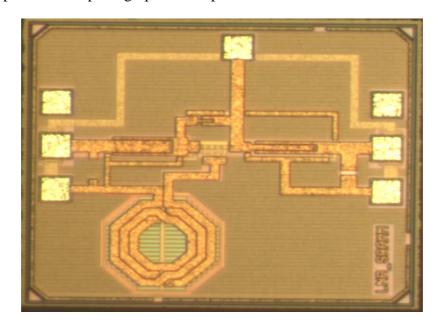

# II.2.3.3. Exemple de layout du transformateur en technologie <u>CMOS 65nm</u>

La Figure II-15 montre le dessin du transformateur à trois inductances en technologie CMOS 65nm. Les inductances *Ll*, *Lt et Ls* sont placées respectivement entre les accès 5-6, 3-4 et 1-2. Les inductances *Ll*, *Lt* et *Ls* sont réalisées à l'aide de deux enroulements pour les deux premières et trois pour la dernière. Ces trois inductances utilisent deux niveaux de métallisation (M6 et M7) et le tout est de forme symétrique. Les accès 7 et 8 correspondent aux accès de l'écran électrostique et sont reliés à la masse.

Figure II-15 : Dessin du transformateur en technologie CMOS 65 nm (unité d'échelle en µm)

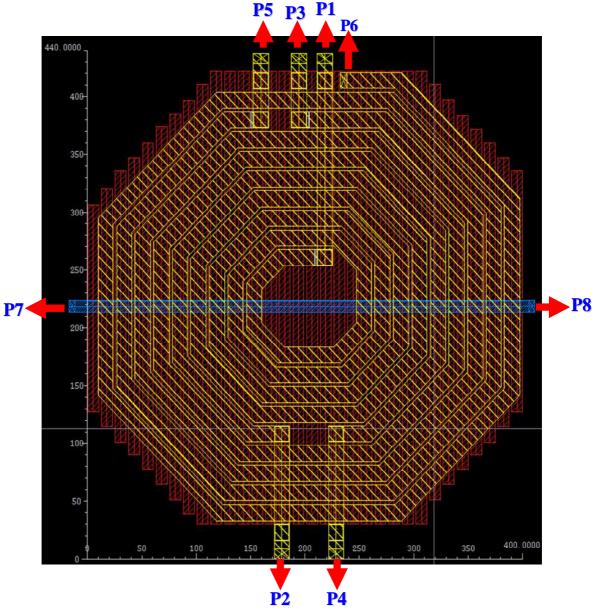

# II.2.3.4. Exemple de layout du transformateur en technologie <u>BiCMOS 0,25 μm</u>

La Figure II-16 montre le dessin du transformateur à trois inductances couplées en technologie QuBic4x. Les inductances *Ll*, *Lt et Ls* sont placées respectivement entre les accès 5-6, 3-4 et 1-2. La première inductance *L1* est formée par deux enroulements, la deuxième *Lt* est formée par deux tours et demi et enfin la troisième *Ls* est formée par trois tours et demi. Les trois inductances utilisent un seul niveau de métallisation (M6). La couche rouge (cf. Figure II-16) représente le « shield », c'est une couche de polysilicium placée comme précédemment entre les lignes des trois inductances et le substrat.

Figure II-16 : Dessin du transformateur en technologie BiCMOS 0,25 μm (unité d'échelle en μm)

## III. Modélisation du transformateur

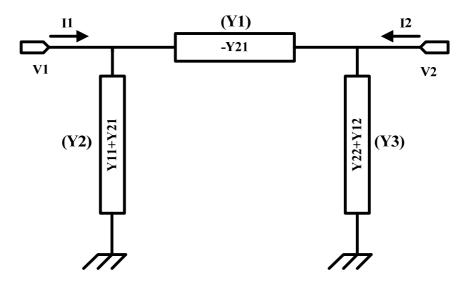

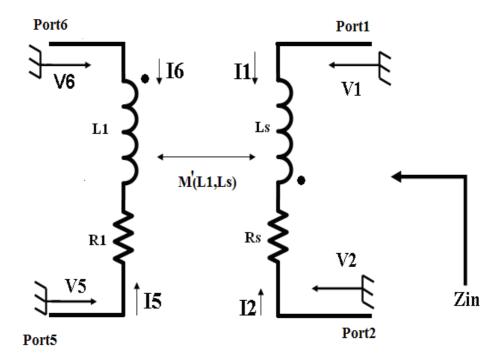

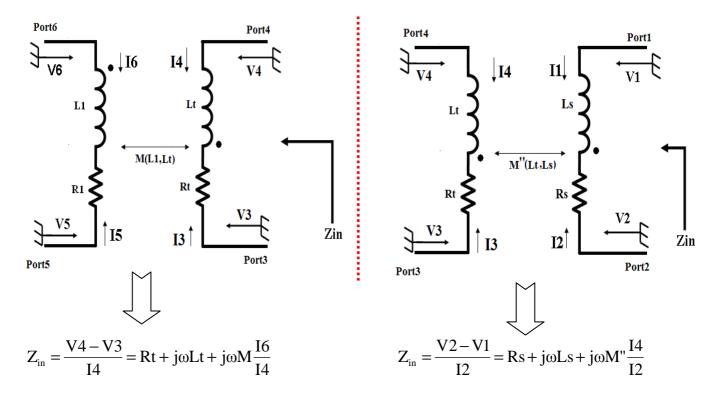

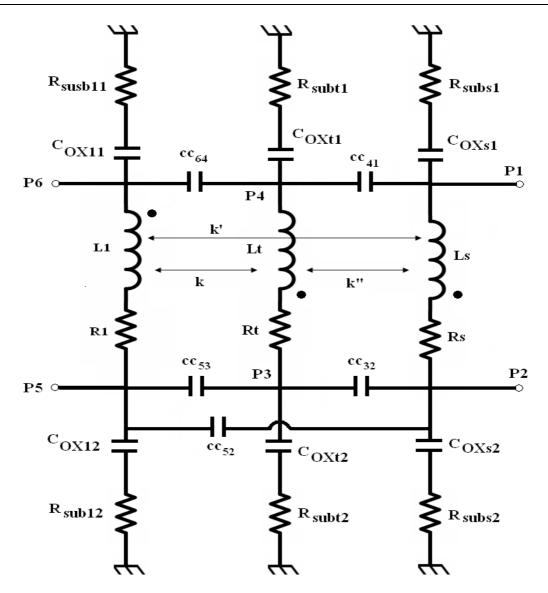

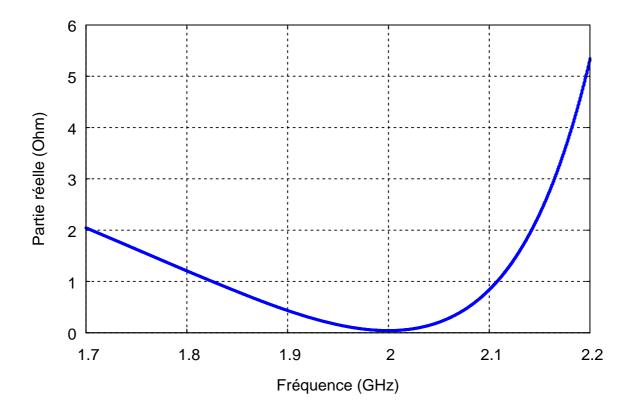

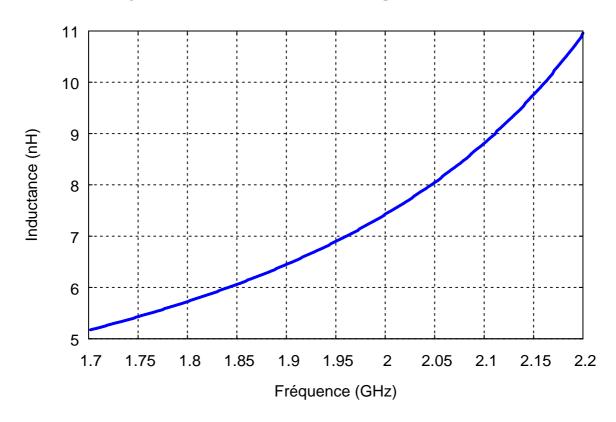

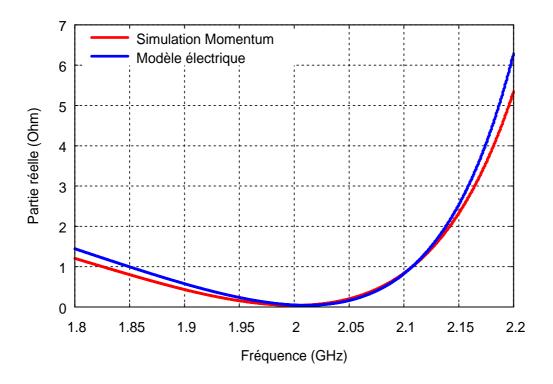

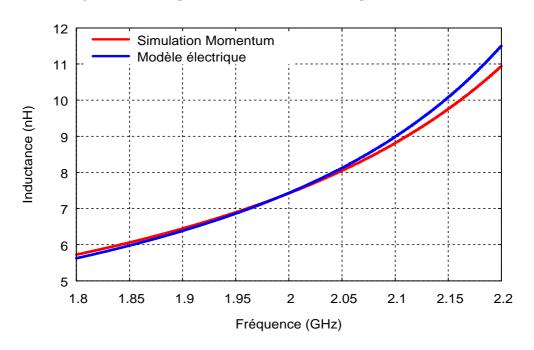

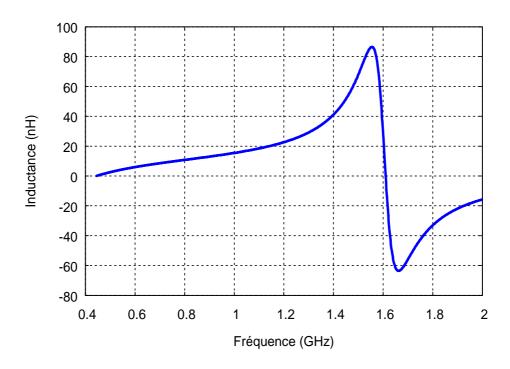

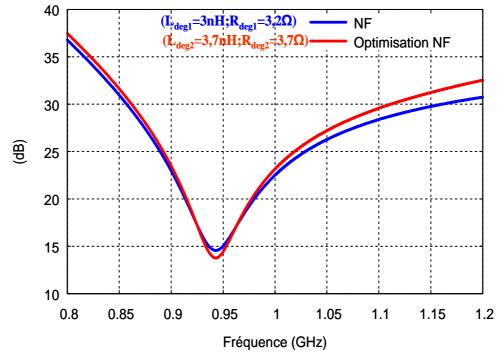

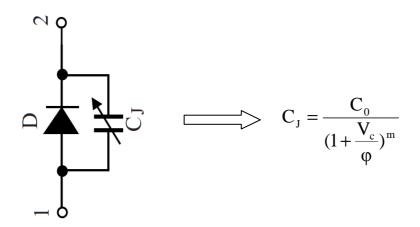

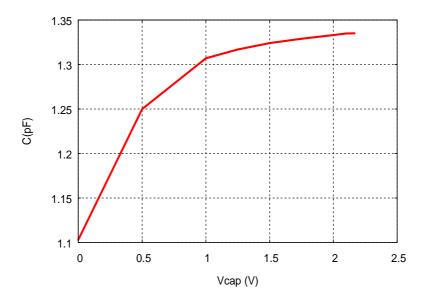

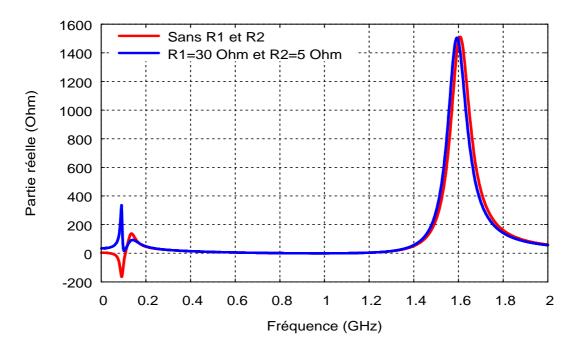

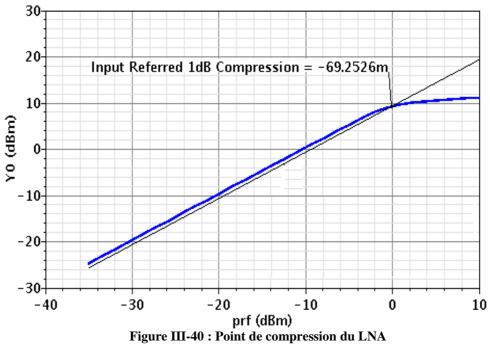

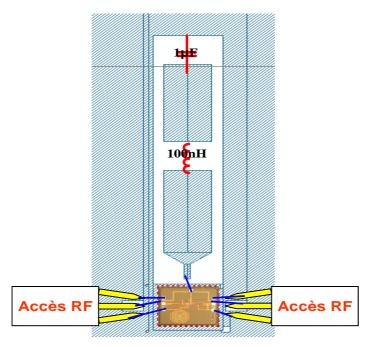

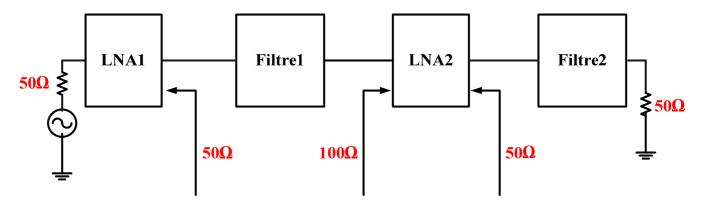

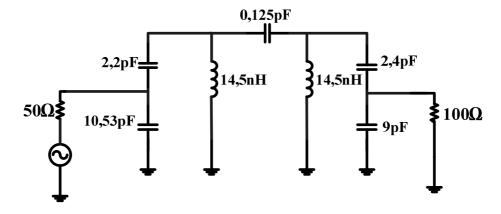

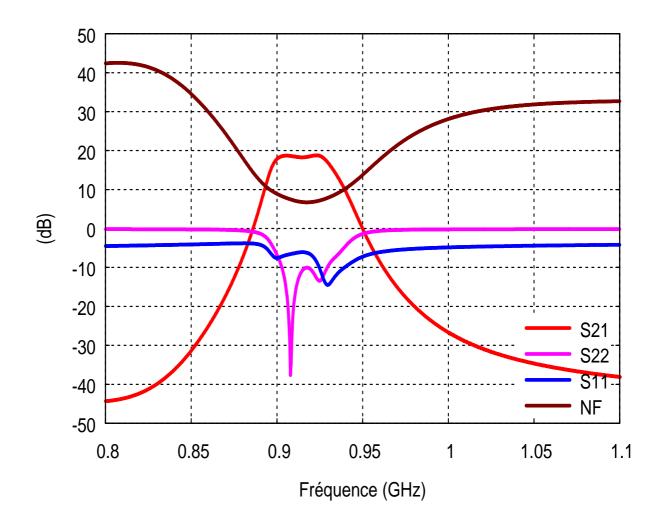

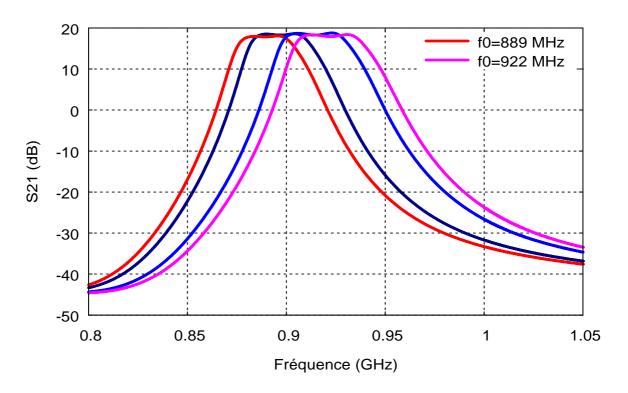

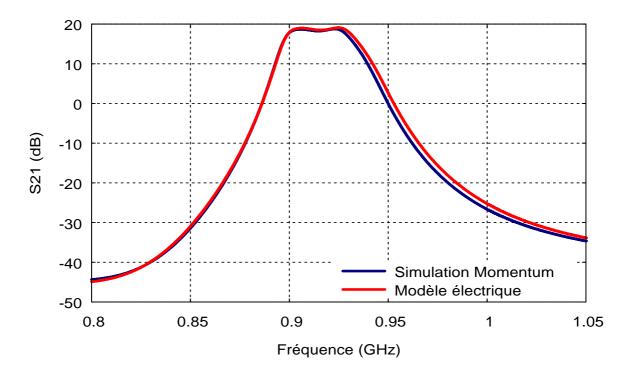

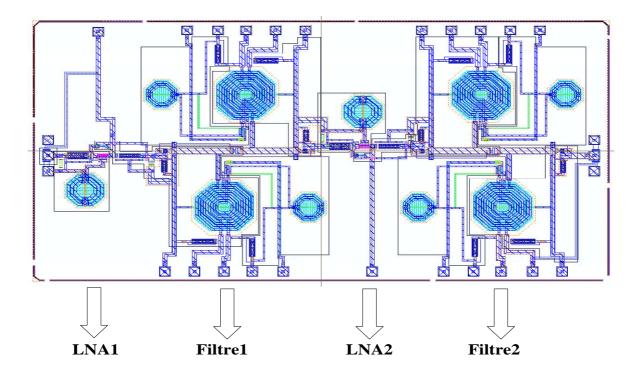

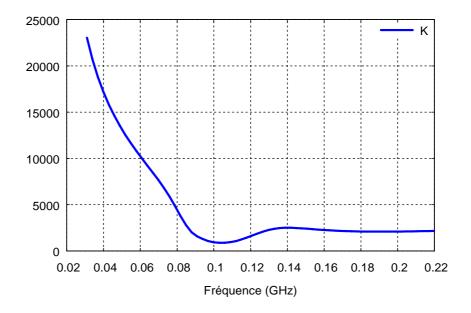

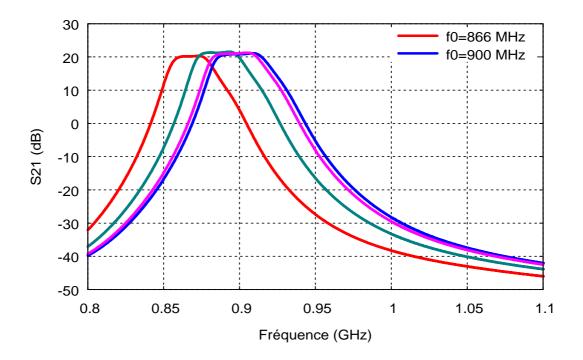

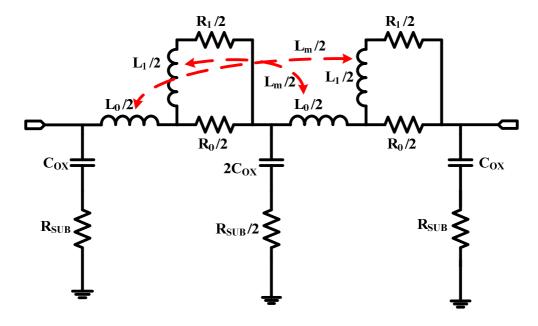

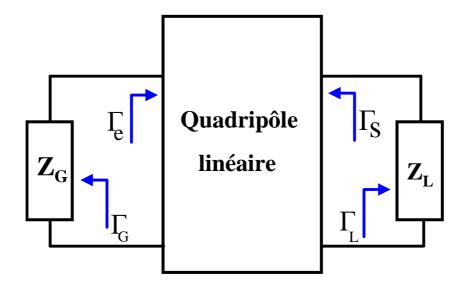

## III.1. Problématique