# UNIVERSITE DE LIMOGES

# ECOLE DOCTORALE Science - Technologie - Santé

# FACULTE DES SCIENCES ET TECHNIQUES

Année : 2006 Thèse N° xx-2006

# **Thèse**

pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITE DE LIMOGES

Discipline : "Electronique des Hautes Fréquences et Optoélectronique"

présentée et soutenue par

**Cyril LAGARDE**

le 29 Septembre 2006

# MODELISATION DE TRANSISTOR DE PUISSANCE EN TECHNOLOGIE GaN : CONCEPTION D'UN AMPLIFICATEUR DE TYPE DOHERTY POUR LES EMETTEURS A PUISSANCE ADAPTATIVE

# Thèse dirigée par Philippe BOUYSSE et Jean-Michel NEBUS

# JURY:

### Président :

Mr le Professeur Raymond QUERE (Université de Limoges)

### **Rapporteurs:**

Mr le Professeur Yide WANG (Université de Nantes)

Mr Claude DUVANAUD HDR (Université de Poitiers)

### **Examinateurs:**

Mr Stéphane FORESTIER (Alcatel Alenia Space Toulouse)

Mr le Professeur Jean-Michel NEBUS (Université de Limoges)

Mr Philippe BOUYSSE (Université de Limoges)

### Invités:

Mr Alain MALLET (CNES Toulouse)

Mr Stéphane PIOTROWICZ (Alcatel Thales III-V Labs)

# **REMERCIEMENTS:**

Ce travail a été réalisé au sein du laboratoire XLIM, sur le site de l'IUT G.E.I.I. de Brive. Je tiens à remercier Monsieur le Professeur P. Y. GUILLON de m'avoir accueilli dans ce laboratoire.

J'exprime mes sincères remerciements à Monsieur le Professeur R. QUÉRÉ pour l'honneur qu'il m'a fait en m'accueillant dans l'équipe « Circuits et sous-ensembles électroniques non linéaires hautes fréquences », maintenant dénommée département C2S2 (Composants, Circuits, Systèmes, Signaux) et en acceptant de présider le jury de cette thèse.

Je voudrais également remercier Monsieur Y. WANG, Professeur au laboratoire IREENA (Institut de Recherche en Electrotechnique et Electronique de Nantes Atlantique) à l'Université de Nantes, et Monsieur C. Duvanaud, maître de conférence Habilité à Diriger les Recherches au laboratoire d'automatique et d'informatique industriel de l'Université de Poitiers, qui ont accepté la responsabilité de juger ce travail en qualité de rapporteurs.

Mes remerciements vont également à Alcatel Alénia Space et tout particulièrement à Monsieur S. FORESTIER, Ingénieur de la société à Toulouse pour sa participation au jury mais surtout pour sa disponibilité et sa contribution à ces travaux en apportant son savoir et ses conseils.

J'ai l'honneur de compter parmi les membres du Jury, la présence de Monsieur A. Mallet, Ingénieur au CNES de Toulouse et de Monsieur S. Piotrowicz, Ingénieur à Alcatel-Thales III-V labs.

J'exprime également ma reconnaissance à Monsieur le Professeur J.M. NEBUS et P. BOUYSSE, Maître de conférence à l'Université de Limoges qui ont plus particulièrement suivi ce travail. Je les remercie pour leur confiance qu'ils m'ont accordée pendant ces trois années.

Je ne voudrais pas oublier Mademoiselle H. BREUZARD, Secrétaire du département C2S2 sur le site de Brive, pour son efficacité et sa disponibilité.

J'associe à mes remerciements Madame M.C.LEROUGE, Secrétaire du département C2S2 sur le site de Limoges, pour son efficacité dans toutes les démarches qu'elle a réalisées sur Limoges.

Enfin, plutôt que d'établir une liste qui se voudrait exhaustive, je ne veux pas oublier dans ces remerciements toute l'équipe de l'IUT G.E.I.I. de Brive et plus particulièrement tous les camarades thésards dont j'ai fait la connaissance durant ces trois années brivistes pour les bons moments passés et pour le courage qu'ils ont eut à me supporter.

# **TABLE DES MATIERES:**

# **TABLE DES MATIERES:**

| CHAPITRE I : Potentialité des différentes technologies de transistors pour l'ampl | ification |

|-----------------------------------------------------------------------------------|-----------|

| de puissance                                                                      |           |

| INTRODUCTION:                                                                     | 7         |

| I. Le GaN vis à vis des autres technologies de transistors de puissance           | 8         |

| I.1. Les transistors bipolaires                                                   | 8         |

| I.1.1. Principe des transistors bipolaires à homojonction                         | 8         |

| I.1.2. Transistors bipolaires à hétérojonction (TBH).                             | 10        |

| I.2. Les transistors à effet de champ.                                            | 11        |

| I.2.1. Principe.                                                                  | 11        |

| I.2.2. Les transistors FET à hétérojonction                                       | 12        |

| I.3. Les principaux transistors FETs de puissance.                                | 12        |

| I.3.1. Les transistors MOSFETs                                                    | 12        |

| I.3.2. Les transistors LDMOS                                                      | 13        |

| I.3.3. Les transistors HEMTs AsGa et PHEMTs AsGa                                  | 14        |

| I.3.4. Les transistors de puissance grand gap.                                    | 17        |

| I.3.4.1. Les transistors MESFETs SiC                                              | 17        |

| I.3.4.2. Les transistors HEMTs GaN                                                | 21        |

| I.4. Synthèse: comparaison des propriétés des transistors de puissance FETs       | 25        |

| I.4.1. Comparaison des paramètres physiques des semi-conducteurs                  | 25        |

| I.4.2. Comparaison des transistors sur les caractéristiques de fréquenc           | e et de   |

| puissance.                                                                        | 26        |

| II. Etat de l'art des transistors de puissance GaN                                | 27        |

| II.1. Historique                                                                  | 27        |

| II.2. Tableau des performances relevées sur les transistors de puissance GaN      | 31        |

| III. Limitations actuelles : effets thermiques et phénomènes de pièges            | 32        |

| III.1. Les effets thermiques dans les transistors HEMTs GaN                       | 32        |

| III.2. Les phénomènes de pièges dans les transistors HEMTs GaN                    | 34        |

| III.2.1.Notion de piège                                                   | 34      |

|---------------------------------------------------------------------------|---------|

| III.2.2.Self-backgating                                                   | 35      |

| III.2.3.Gate-lag                                                          | 37      |

| CONCLUSION:                                                               | 41      |

|                                                                           |         |

| CHAPITRE II: Modélisation non-linéaire d'un transistor HEMT AlGaN/GaN i   | ncluant |

| les effets thermiques et les phénomènes de pièges                         |         |

| INTRODUCTION :                                                            | 49      |

| I. Caractérisation du composant.                                          | 50      |

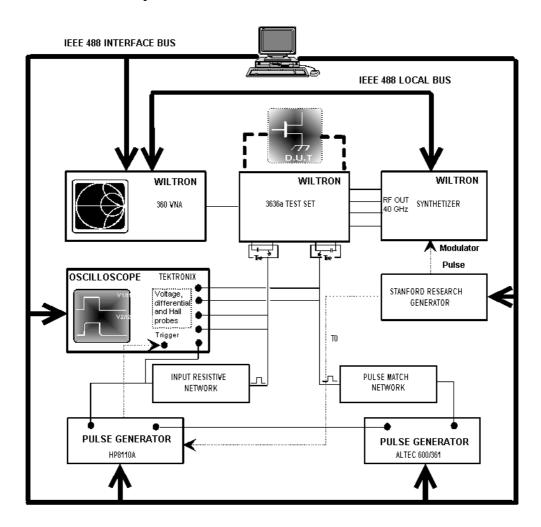

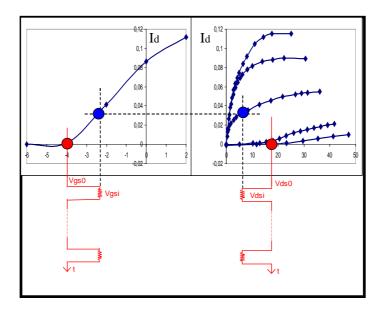

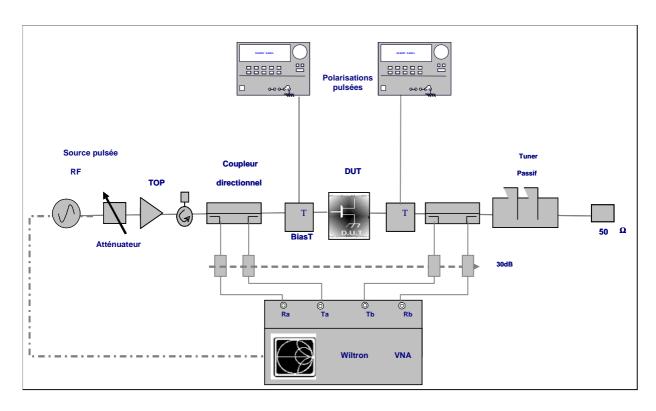

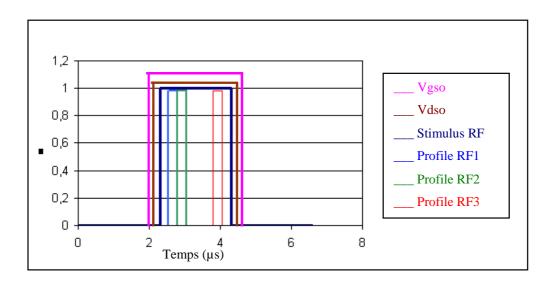

| I.1. Principe du banc de mesure I(V) et paramètres [S] impulsionnel       | 50      |

| I.2. Principe des mesures en température                                  | 52      |

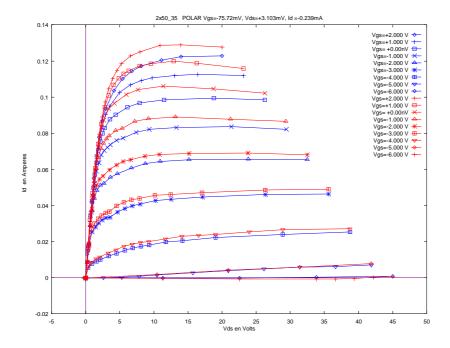

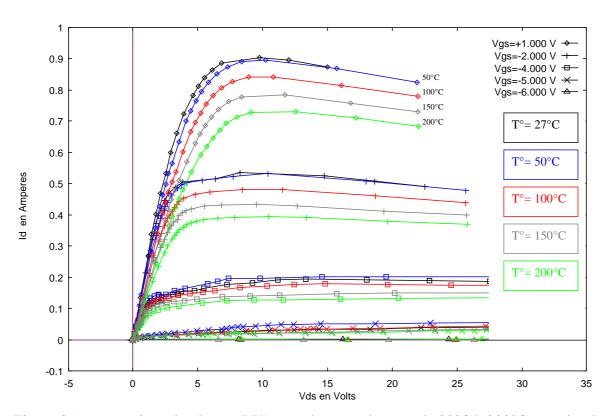

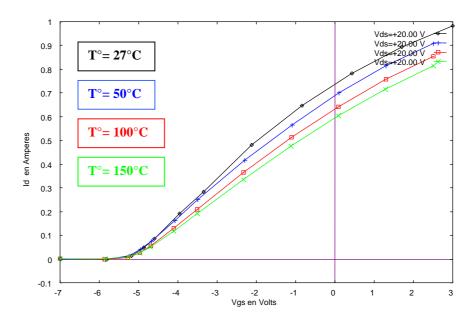

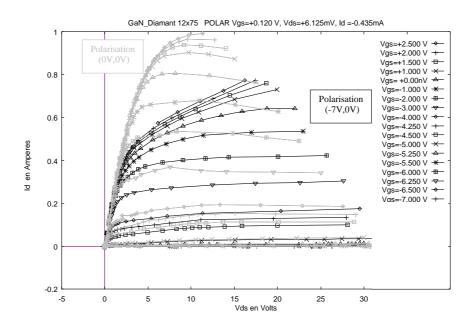

| I.3. Mise en évidence des phénomènes thermiques du transistor GaN 12x75µm | 53      |

| I.3.1. Evolution des réseaux I(V) en fonction de la température           | 53      |

| I.3.2. Principe de mesure de la résistance thermique.                     | 55      |

| I.4. Mise en évidence des phénomènes de pièges.                           | 57      |

| I.4.1. Mise en évidence des "pièges de drain"                             | 57      |

| I.4.2 Mise en évidence des "pièges de grille"                             | 58      |

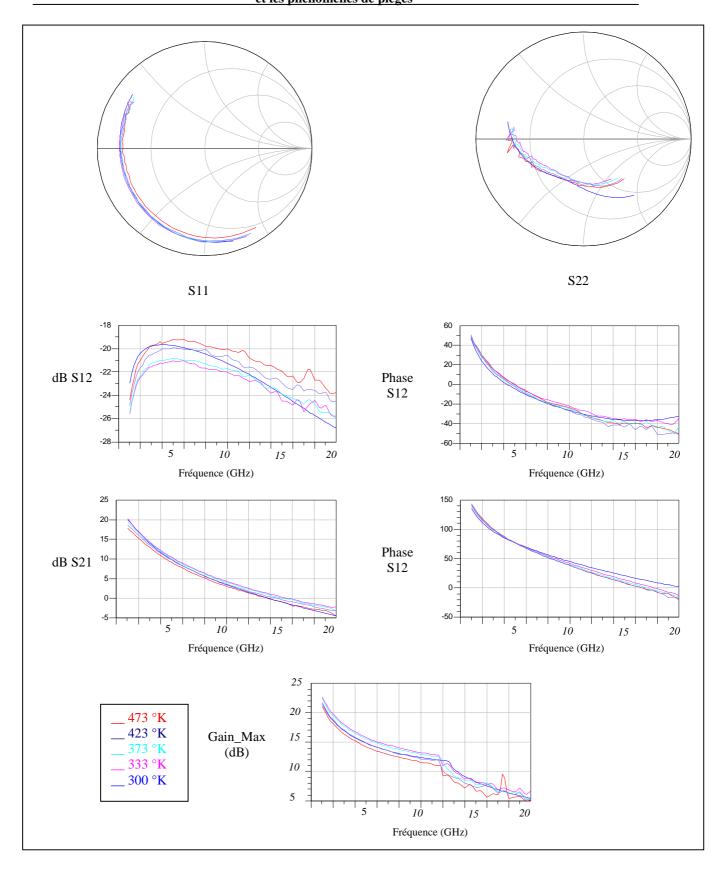

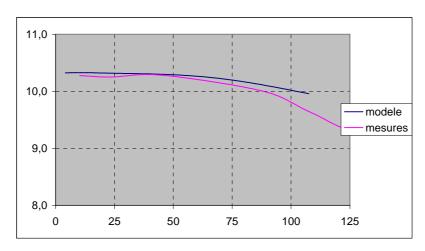

| I.5. Evolution des paramètres [S] en fonction de la température           | 59      |

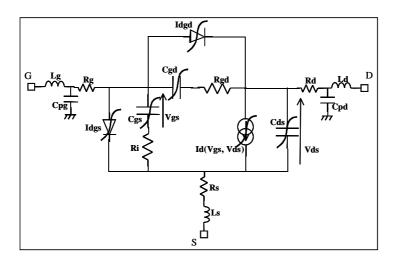

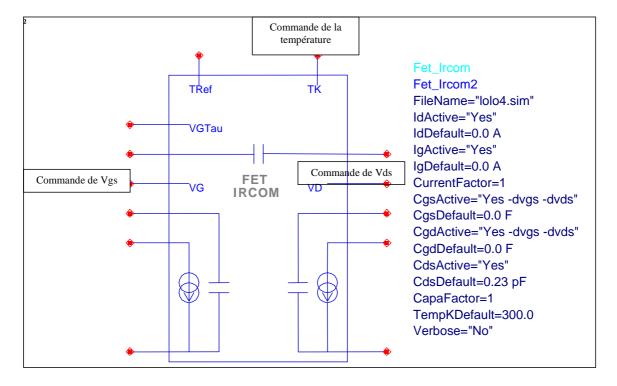

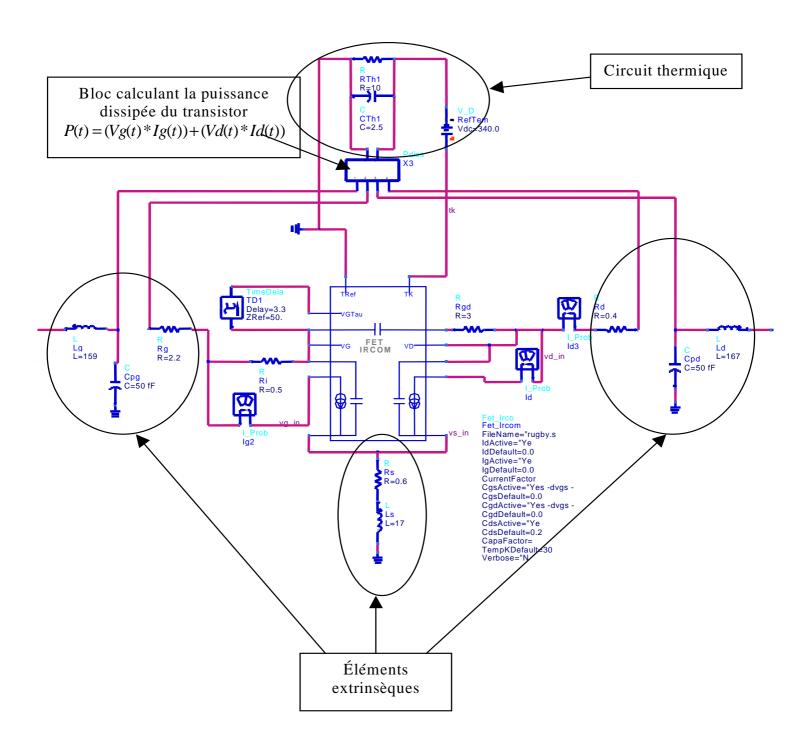

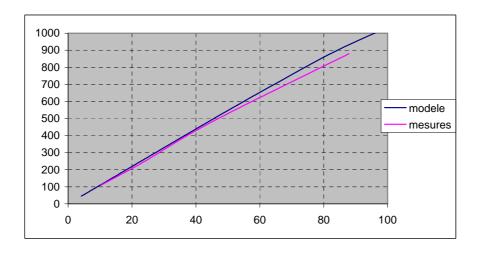

| II. Modélisation de transistor par un modèle tabulaire électrothermique   | 61      |

| II.1. Introduction au modèle.                                             | 61      |

| II.1.1. Modèle par équations phénoménologiques                            | 61      |

| II.1.2. Modélisation par table 3D.                                        | 62      |

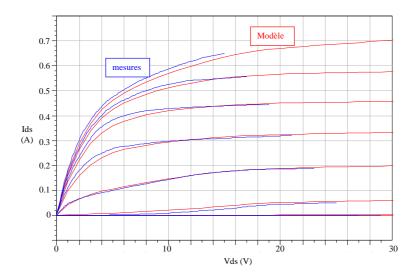

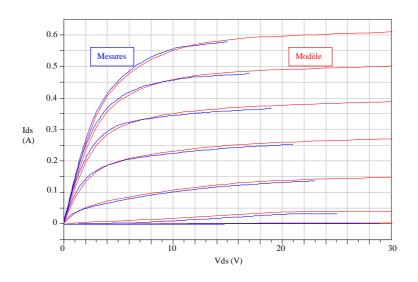

| II.2. Modélisation du transistor GaN 12*75µm                              | 65      |

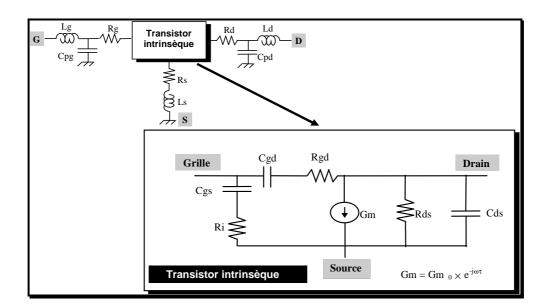

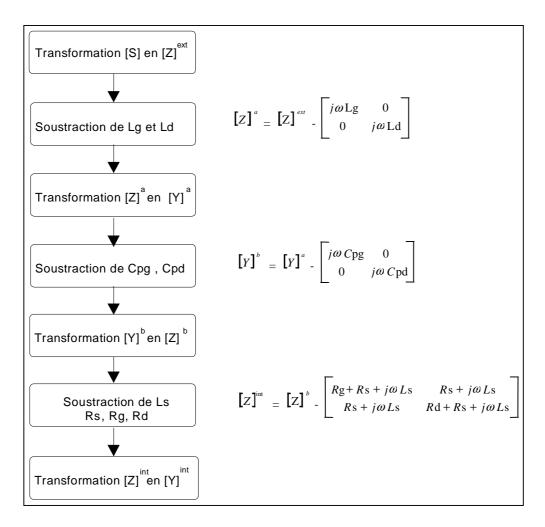

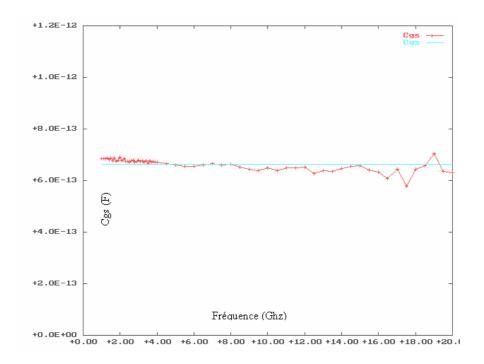

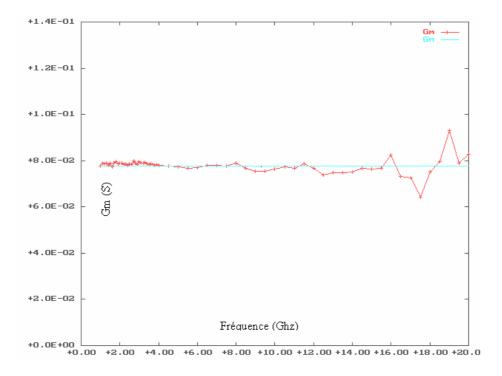

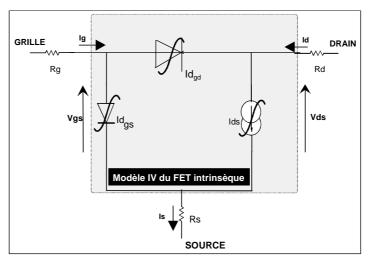

| II.2.1.Modèle électrique petit signal                                     | 65      |

| II.2.2. Modèle électrique non-linéaire.                                   | 71      |

| II.2.2.1. Eléments non-linéaires convectifs.                              | 71      |

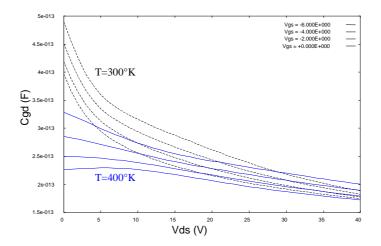

| II.2.2.2. Modèle non-linéaire des capacités                               | 73      |

| II.2.3. Circuit thermique.                                                | 76      |

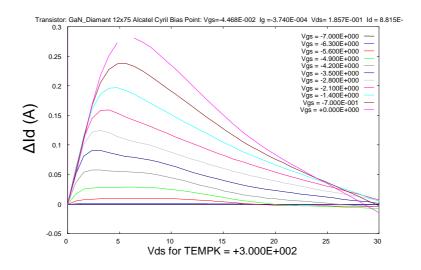

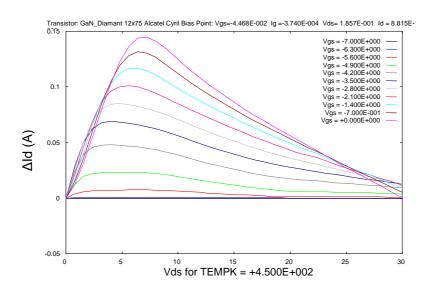

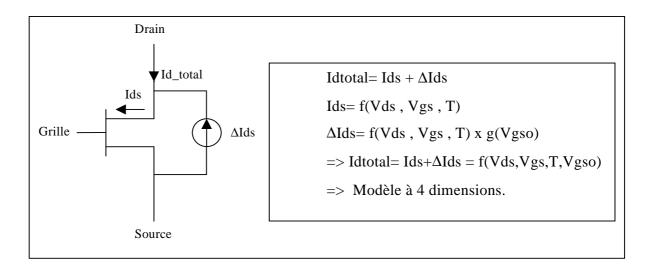

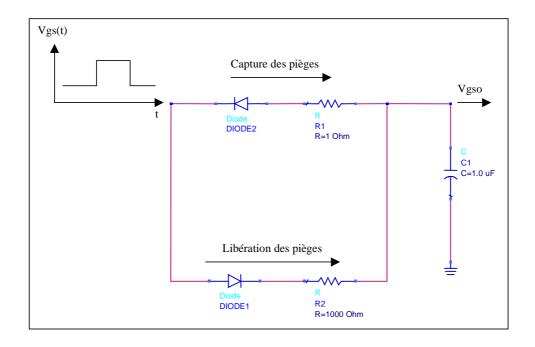

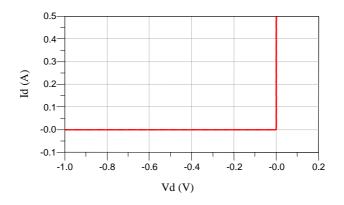

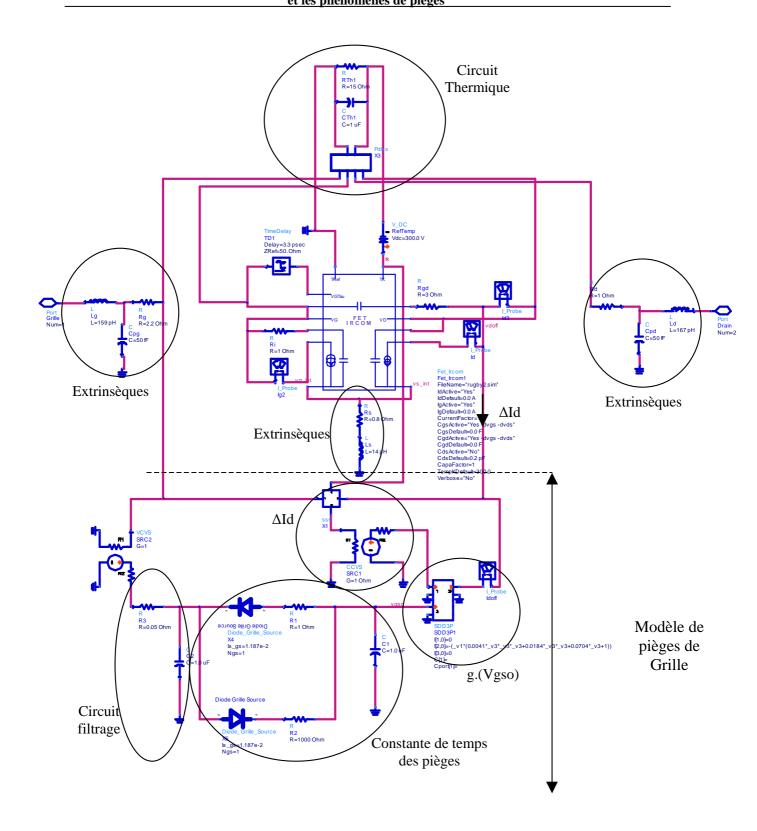

| III. Développement d'un modèle de pièges de grille                        | 78      |

| III.1. Présentation                                                       | 78      |

| III.2. Principe du modèle de pièges                                       | 78      |

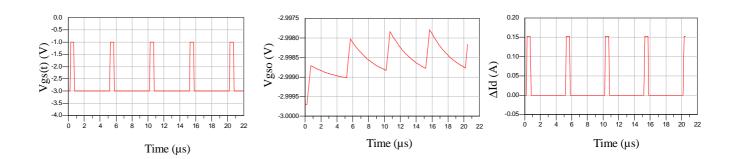

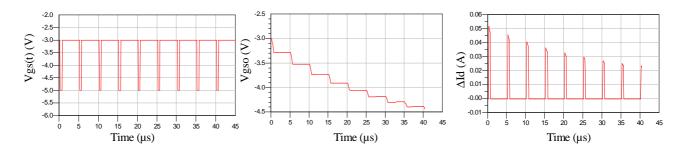

| III.3. Simulations temporelles des effets de piège                        | 83      |

| III.3.1. Premier exemple de simulation temporelle                         | 83      |

|      | III.3.2. Deuxième exemple de simulation temporelle.                                                                     | 84           |

|------|-------------------------------------------------------------------------------------------------------------------------|--------------|

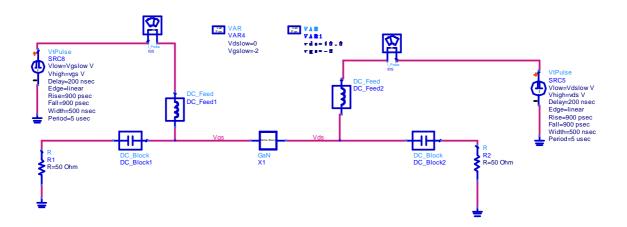

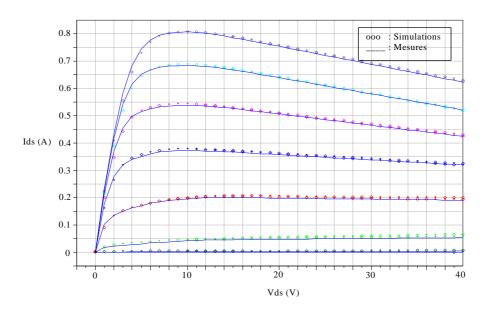

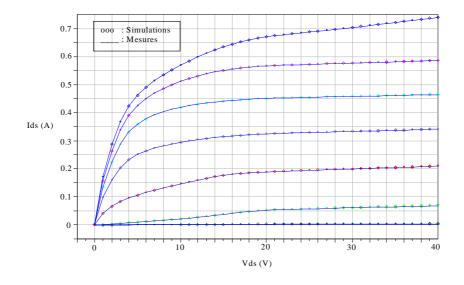

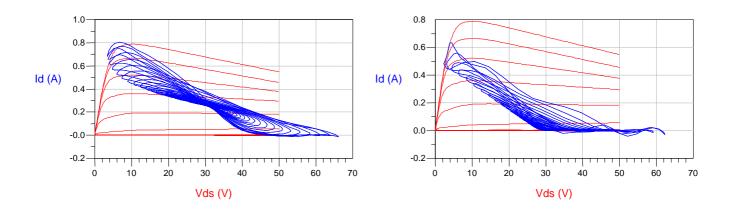

| ]    | III.4. Simulations I(V) pulsées                                                                                         | 84           |

| IV   | . Validation en puissance du modèle                                                                                     | 88           |

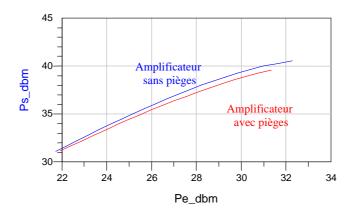

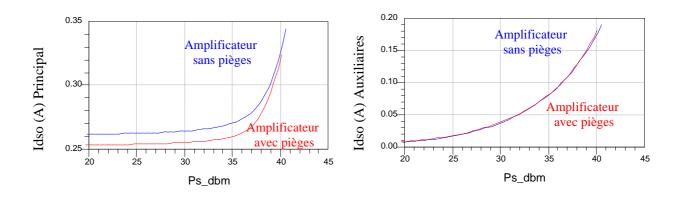

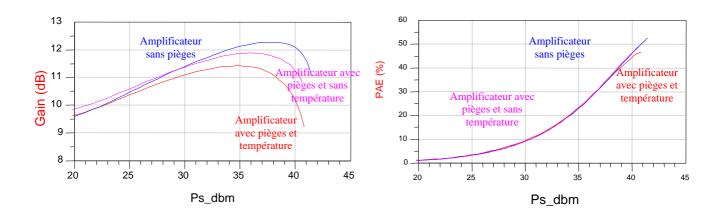

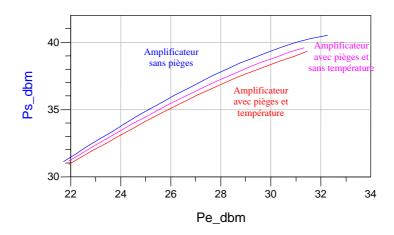

| ]    | IV.1. Comparaisons en puissance Modèle / Mesures                                                                        | 89           |

|      | IV.1.1. Configuration $n^{\circ}1$ : point de polarisation Vgs=-3.3V et Vds=29V                                         | et point de  |

|      | repos (Vgso=0V, Vdso=20V)                                                                                               | 90           |

|      | IV.1.2. Point de polarisation vgs=-5.5V et Vds=29V et point de repos (                                                  | Vgso=-7V,    |

|      | Vdso=20V)                                                                                                               | 92           |

| ]    | IV.2. Influence des effets de piège sur les performances en puissance                                                   | 93           |

| CON  | CLUSION:                                                                                                                | 96           |

|      | APITRE III : Description des principales techniques de gestion du c<br>ement-linéarité des amplificateurs de puissance. | compromis    |

| INTR | RODUCTION                                                                                                               | 101          |

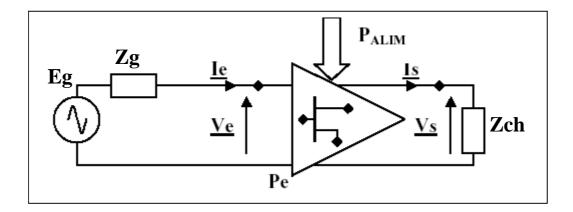

| I.   | Problématique des amplificateurs de puissance.                                                                          | 102          |

| ]    | I.1. Introduction sur l'amplification de puissance                                                                      | 102          |

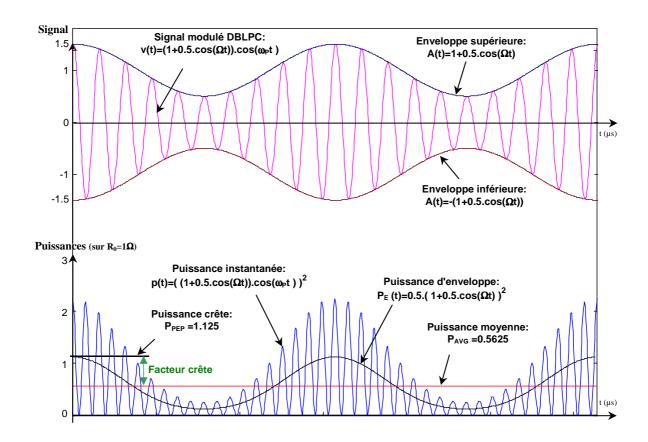

|      | I.1.1. Caractéristiques des signaux à enveloppe variable.                                                               | 102          |

|      | I.1.1.1 Définitions spécifiques des signaux à enveloppe variable                                                        | 102          |

|      | I.1.1.2. Caractéristiques de quelques modulations à enveloppe variable                                                  | 104          |

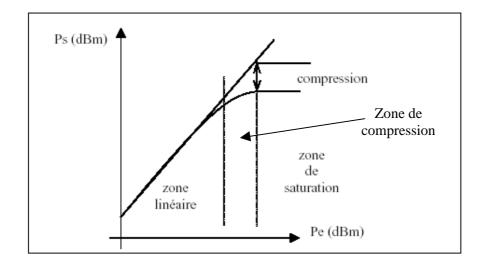

|      | I.1.2. Evaluation des performances d'un amplificateur de puissance                                                      | 105          |

|      | I.1.2.1. Puissances et rendement                                                                                        | 105          |

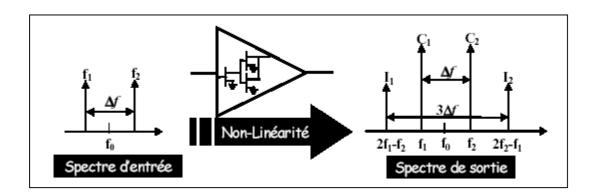

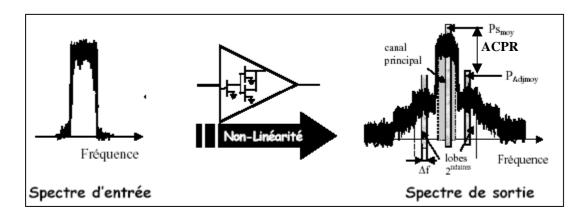

|      | I.1.2.2. Grandeurs caractéristiques du comportement non linéaire des amp                                                | lificateurs. |

|      |                                                                                                                         | 109          |

| ]    | I.2. Présentation de la problématique puissance / rendement / linéarité                                                 | 112          |

| ]    | I.3. Principes des techniques de linéarisation : systèmes de correction des                                             | distorsions  |

| 1    | non-linéaires.                                                                                                          | 114          |

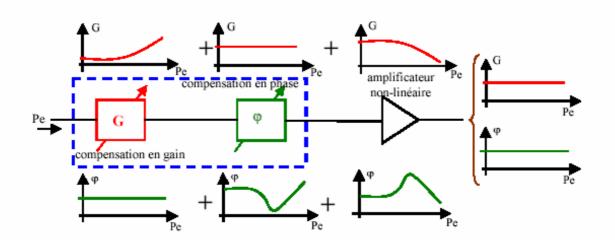

|      | I.3.1. Linéarisation par pré-distorsion.                                                                                | 114          |

|      | I.3.2. Contre- réaction : Feedback                                                                                      | 115          |

|      | I.3.3. LINC (Linear amplification with Non-linear Components)                                                           | 116          |

|      | I.3.4. CALLUM (Combined Analog Locked-Loop Universal Modulator)                                                         | 117          |

|      | I.3.5. Feedforward                                                                                                      | 118          |

| ]    | I.4. Principes des techniques de haut rendement : contrôle actif d'un pa                                                | ramètre de   |

| ]    | l'amplificateur                                                                                                         | 120          |

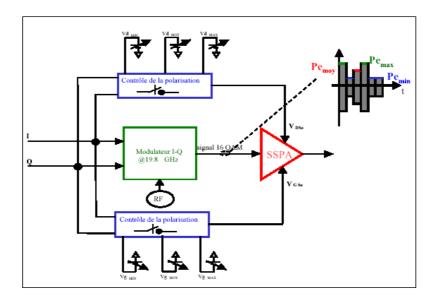

| I.4.1. Gestion dynamique des polarisations                                          | 120                      |

|-------------------------------------------------------------------------------------|--------------------------|

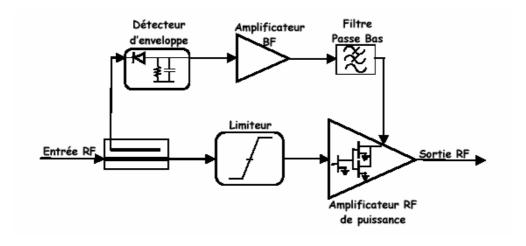

| I.4.2. E.E.R. (Elimination de l'Enveloppe et Restauration)                          | 122                      |

| II. Présentation de la technique Doherty.                                           | 124                      |

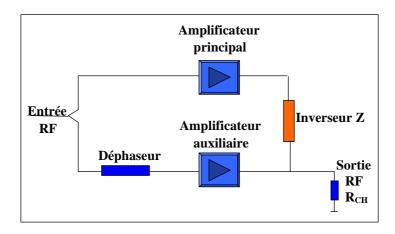

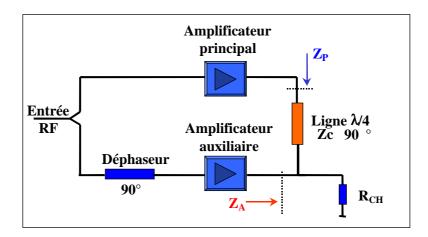

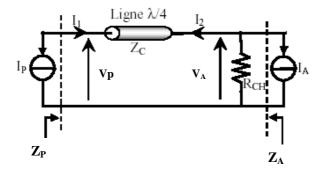

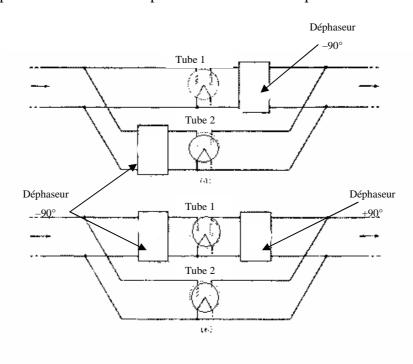

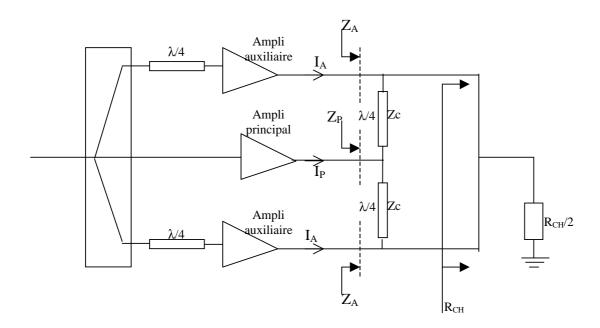

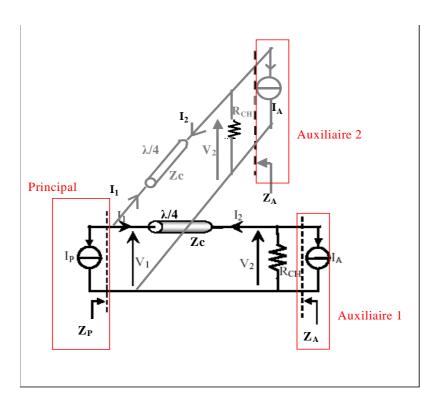

| II.1. Schéma de principe de l'amplificateur Doherty                                 | 124                      |

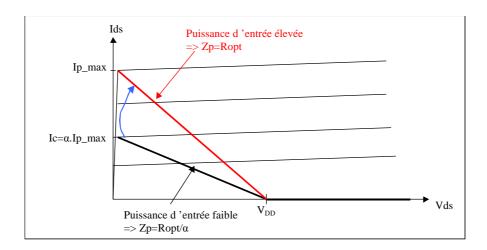

| II.2. Etude théorique générale de l'amplification Doherty                           | 127                      |

| II.2.1. Relations de base                                                           | 127                      |

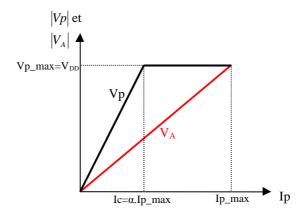

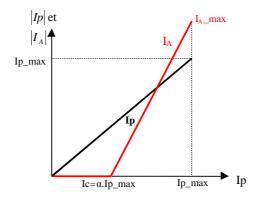

| II.2.2. Evolution des tensions en fonction du niveau de puissance                   | 128                      |

| II.2.3. Evolution des courants en fonction du niveau de puissance                   | 130                      |

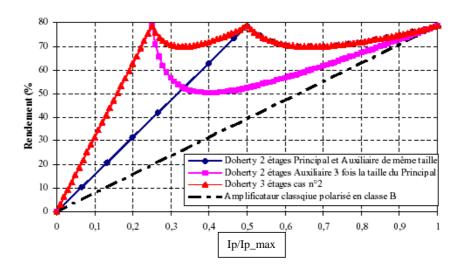

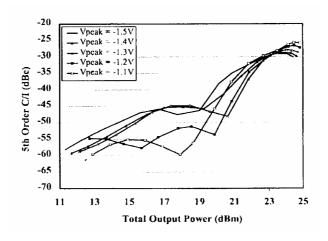

| II.2.4. Evolution du rendement en fonction du niveau de puissance                   | 131                      |

| II.2.5. Calcul de l' « Output Back-off »                                            | 134                      |

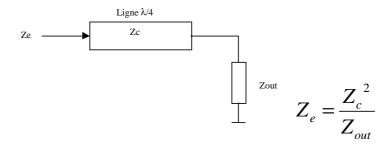

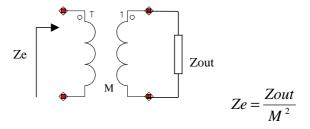

| II.3. Application pour un amplificateur Doherty classique (transistors de mêm       | e taille) 135            |

| II.3.1. Détermination de l'impédance caractéristique Zc et de la résistance         | e de charge              |

| R <sub>CH.</sub>                                                                    | 135                      |

| II.3.2. Evolution des impédances de charge des deux amplificateurs                  | 136                      |

| II.3.3. Evolution du rendement                                                      | 137                      |

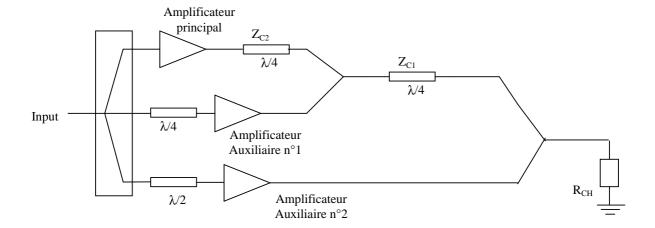

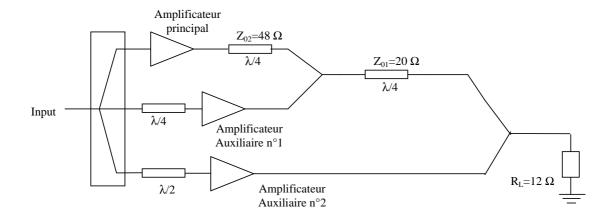

| II.4. Application pour un Amplificateur Doherty à auxiliaire double                 | 138                      |

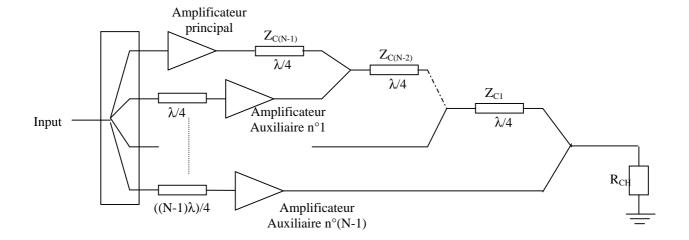

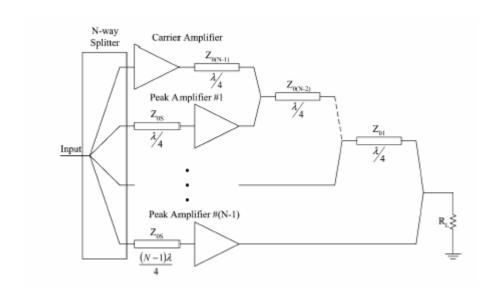

| II.5. Doherty à N étages.                                                           | 140                      |

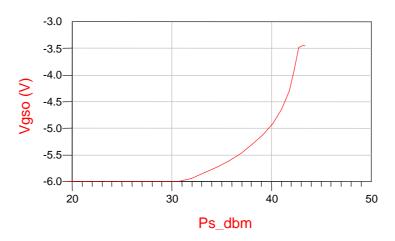

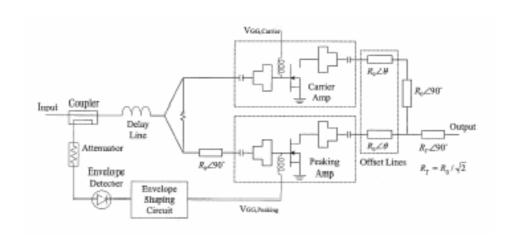

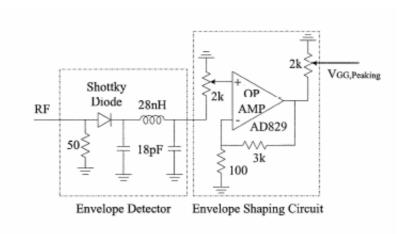

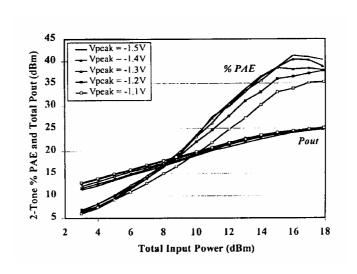

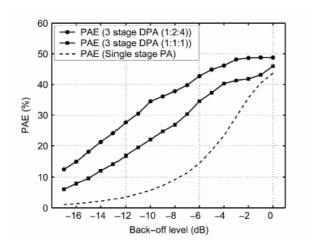

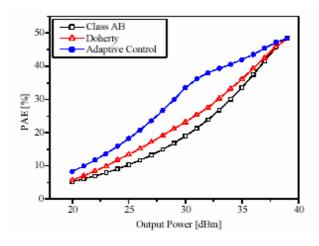

| II.6. Doherty à commande dynamique de polarisation.                                 | 143                      |

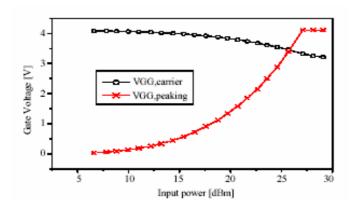

| II.6.1. Commande de grille des auxiliaires                                          | 143                      |

| II.6.2. Commande de drain du principal                                              | 145                      |

| III. Etat de l'art de la technique Doherty.                                         | 147                      |

| III.1. Historique.                                                                  | 147                      |

| III.2. Synthèse des réalisations d'amplificateur Doherty publiées                   | 155                      |

| CONCLUSION                                                                          | 156                      |

| CHAPITRE IV: Conception d'un amplificateur Doherty à transistors GaN et symétrique. | à structure              |

| INTRODUCTION                                                                        | 163                      |

| I. Etude du nouvel amplificateur Doherty proposé                                    | 164                      |

| I.1. Principe de fonctionnement                                                     | 164                      |

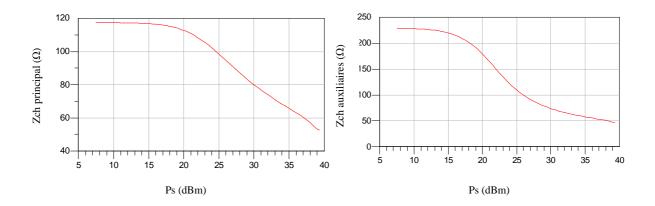

| I.2. Détermination des impédances de charge des amplificateurs                      | 165                      |

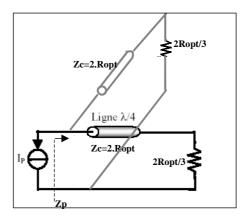

| I.3. Détermination de l'impédance caractéristique Zc et de la résistance de c       | charge R <sub>CH</sub> . |

|                                                                                     | 166                      |

| I.4. Evolution des impédances de charge des deux amplificateurs                 | 167            |

|---------------------------------------------------------------------------------|----------------|

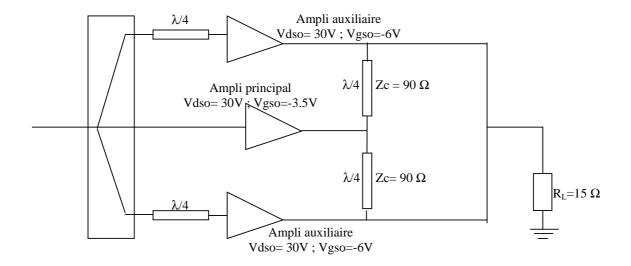

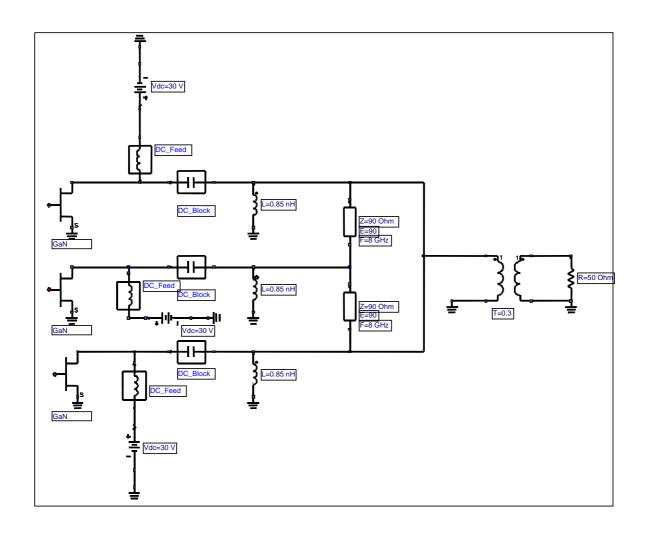

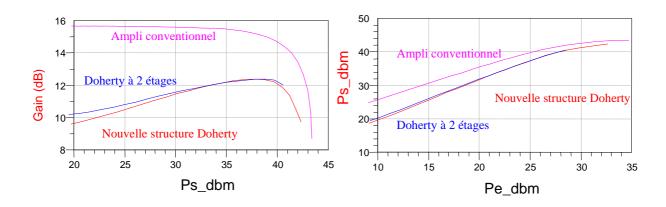

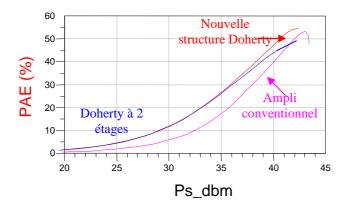

| I.5. Simulations de l'amplificateur de puissance proposé                        | 168            |

| I.5.1.Simulations en puissance                                                  | 168            |

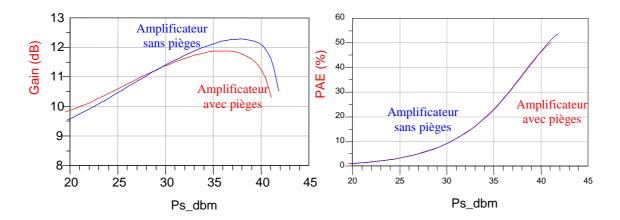

| I.5.2. Influence des effets de pièges et de température                         | 173            |

| I.5.2.1. Influence des effets de piège.                                         | 173            |

| I.5.2. Influence des effets de température.                                     | 175            |

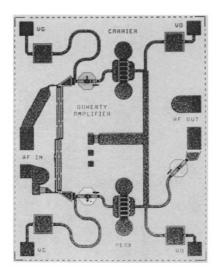

| II. Conception de l'amplificateur.                                              | 177            |

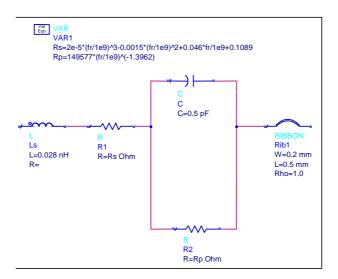

| II.1. Modèles électriques des différents éléments de la conception              | 178            |

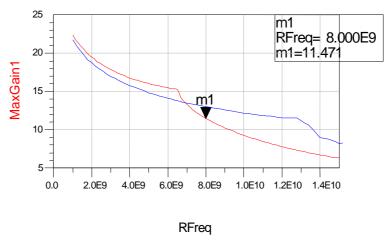

| II.1.1. Modèle électrique du transistor.                                        | 179            |

| II.1.2. Capacités de liaison.                                                   | 180            |

| II.2. Conception des Mics.                                                      | 180            |

| II.2.1. Substrat utilisé.                                                       | 180            |

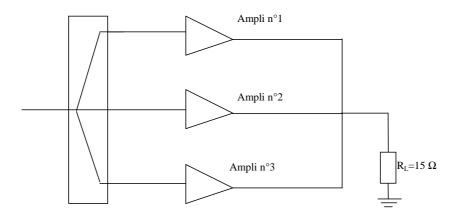

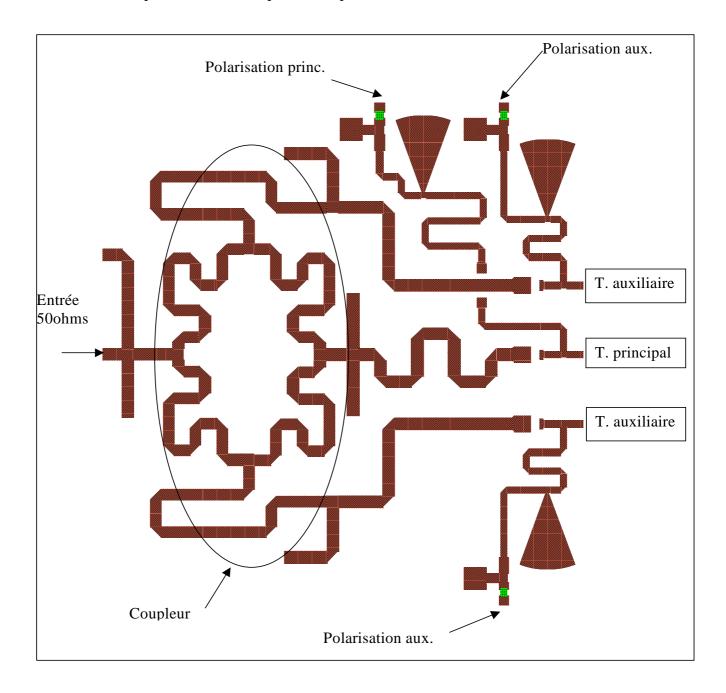

| II.2.2. Diviseur de puissance 1 voie vers 3                                     | 181            |

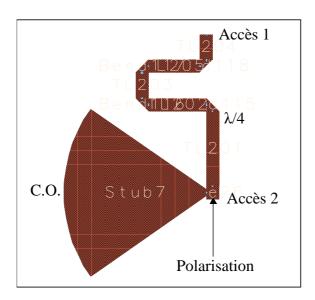

| II.2.3. Circuits de polarisations.                                              | 183            |

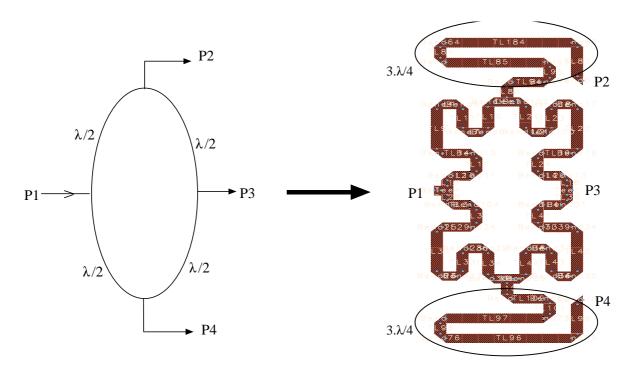

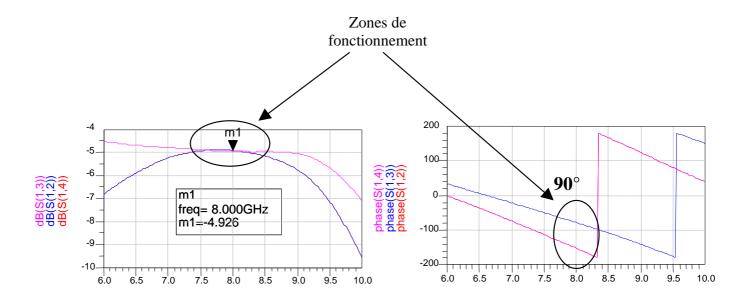

| II.2.4. Circuit hybride de sortie.                                              | 184            |

| II.2.5. Circuit hybride d'entrée.                                               | 186            |

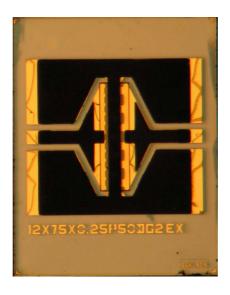

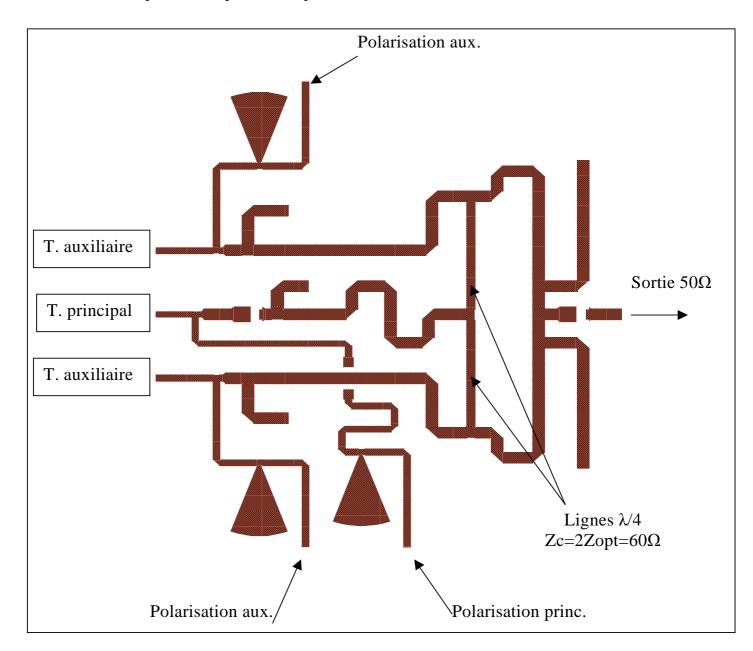

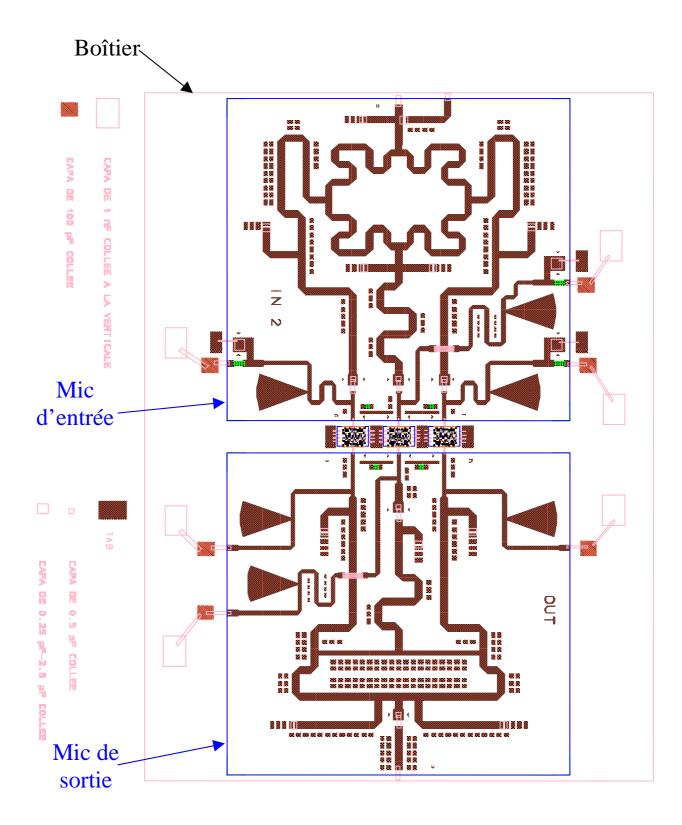

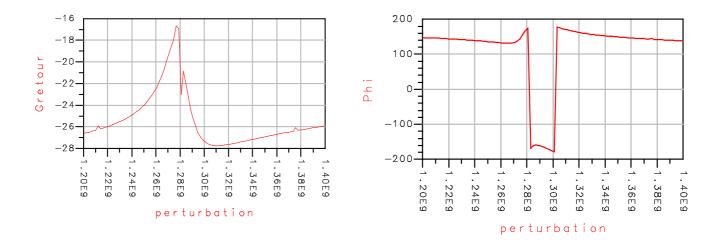

| II.2.6. Amplificateur conçu                                                     | 188            |

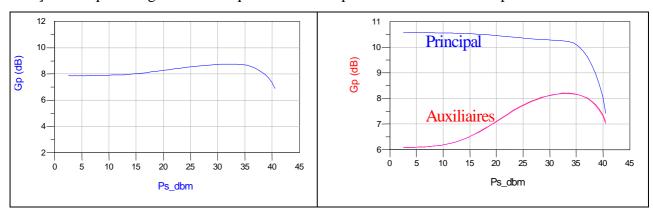

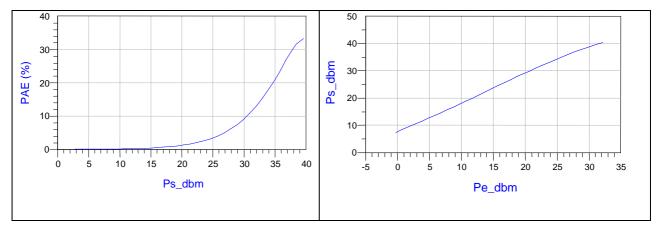

| II.3. Résultats de simulations.                                                 | 189            |

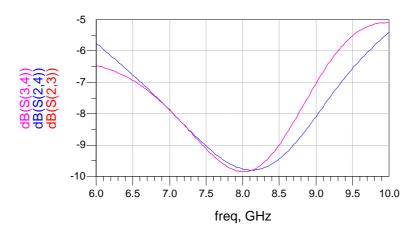

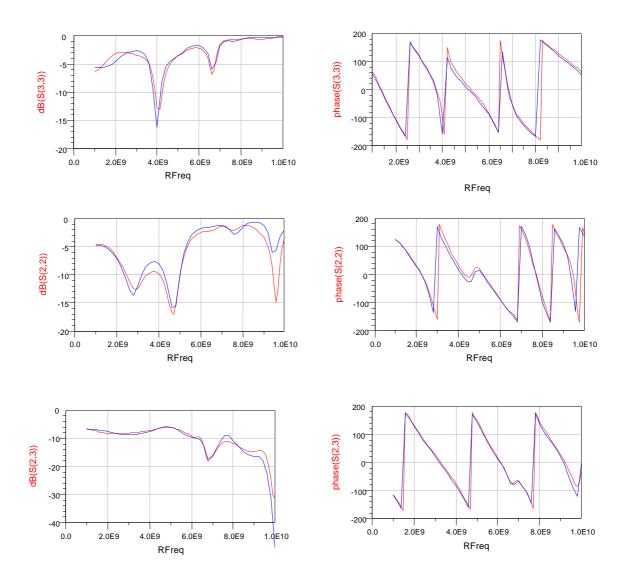

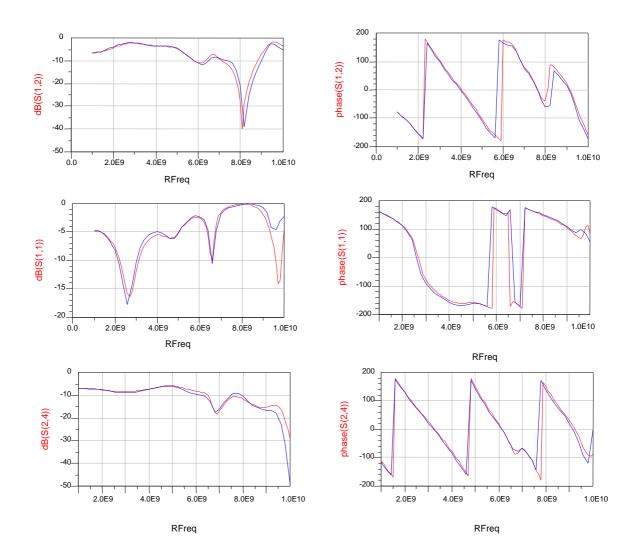

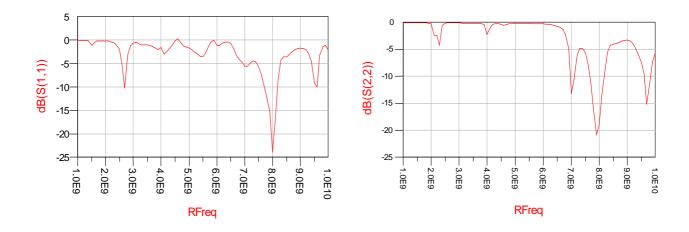

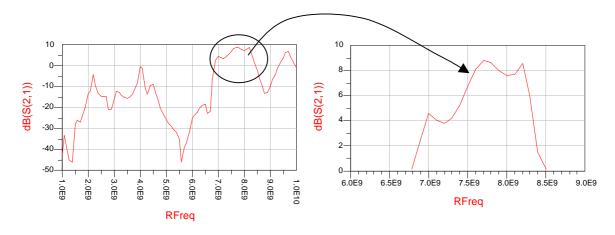

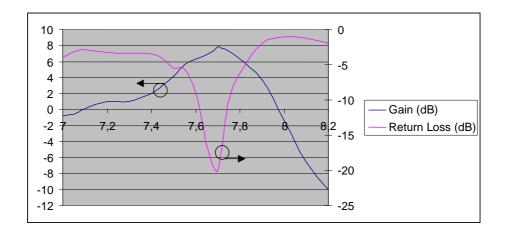

| II.3.1. Simulations paramètres [S]                                              | 189            |

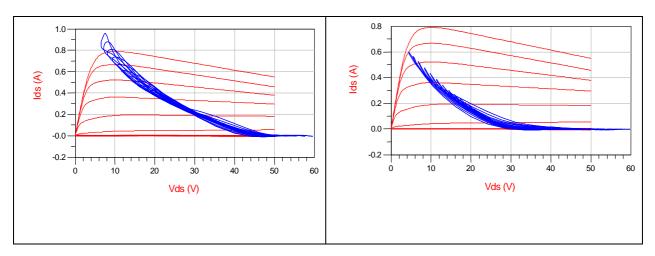

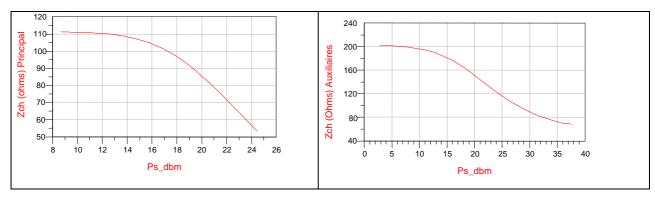

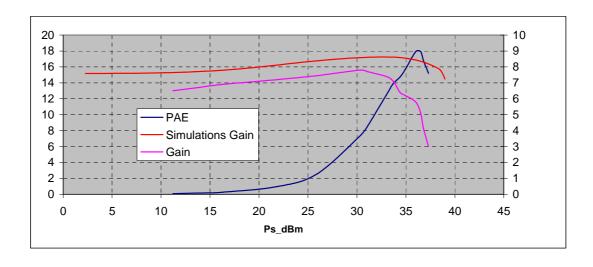

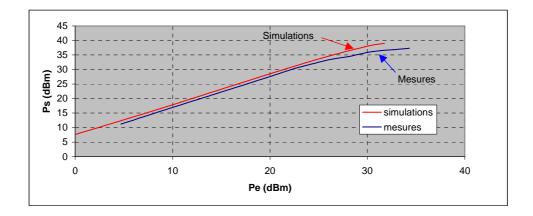

| II.3.2. Simulations en puissance.                                               | 190            |

| II.3.3. Tableau de synthèse des simulations.                                    | 192            |

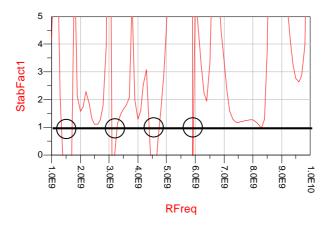

| III. Etude de la stabilité                                                      | 193            |

| III.1. Stabilité petit signal : facteurs K et b.                                | 193            |

| III.2. Stabilité non-linéaire par identification de la réponse fréquentielle en | boucle fermée  |

|                                                                                 | 195            |

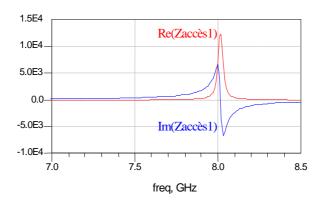

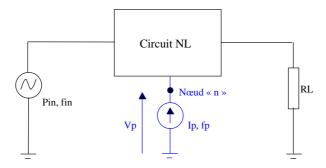

| III.2.1. Technique d'analyse STAN.                                              | 195            |

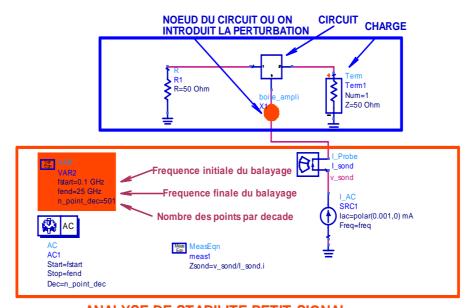

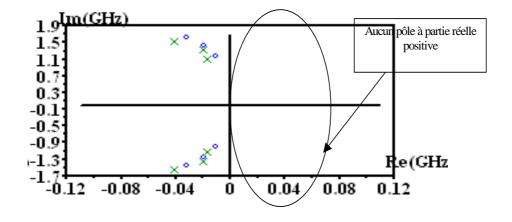

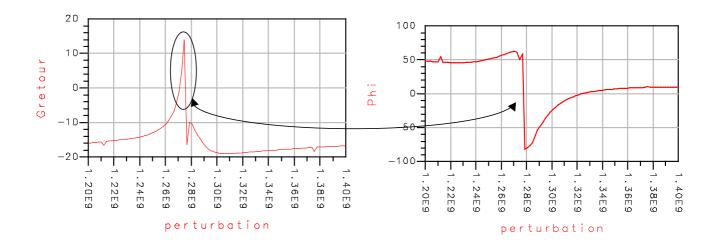

| III.2.2. Analyse de stabilité linéaire.                                         | 197            |

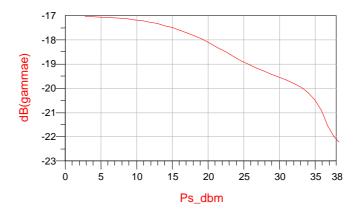

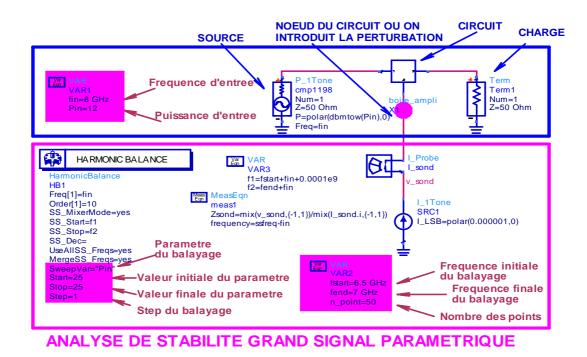

| III.2.3. Analyse de stabilité non-linéaire.                                     | 198            |

| III.3. Analyse de la stabilité non-linéaire par introduction d'une perturba     | tion en boucle |

| ouverte                                                                         | 200            |

| III.3.1. Technique d'analyse                                                    | 200            |

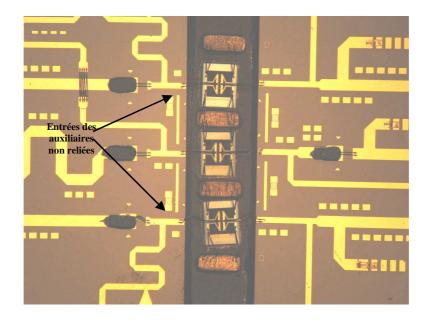

| III.3.2. Analyse d'une oscillation de type impair                               | 201            |

| III.4. Tableau de synthèse de la stabilité                                      | 203            |

| III.5. Corrélations avec les mesures.     | 204 |

|-------------------------------------------|-----|

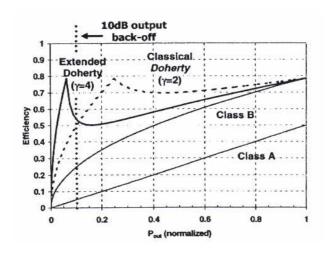

| IV. Résultats expérimentaux               | 205 |

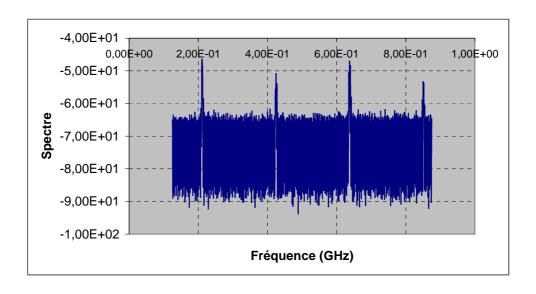

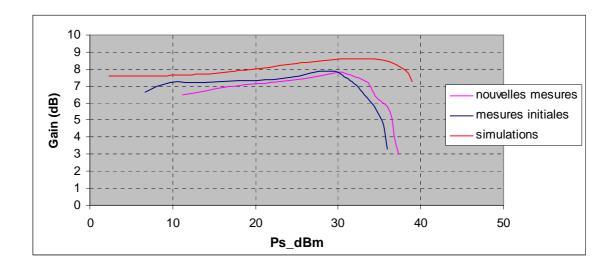

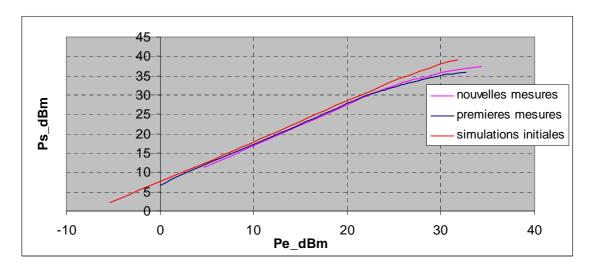

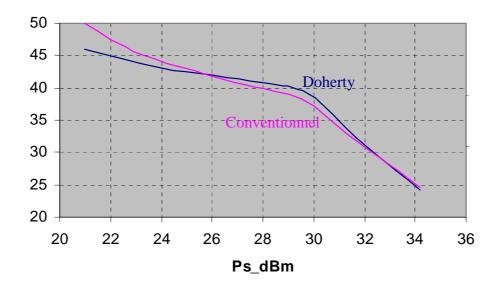

| IV.1. Mesures en puissance                | 206 |

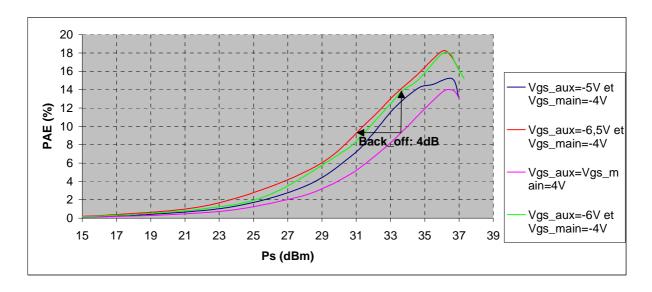

| IV.2. Démonstration de l'effet Doherty    | 209 |

| IV.3. Mesures en fonction de la fréquence | 210 |

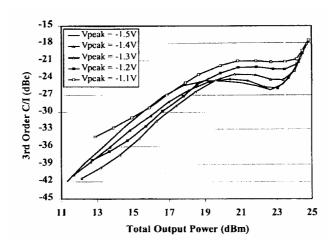

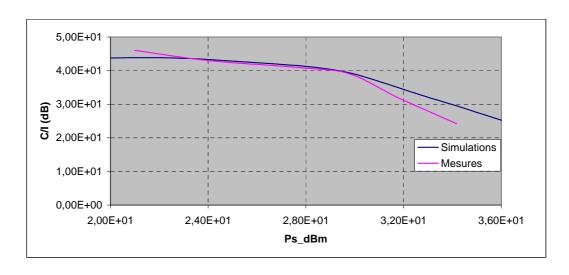

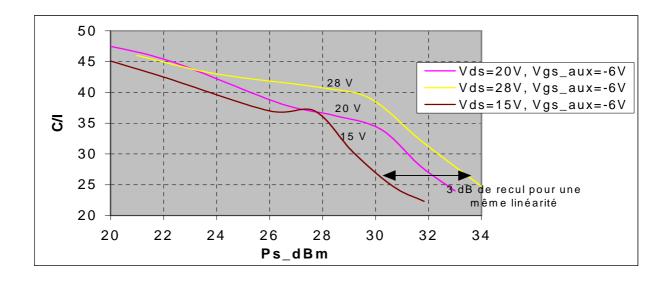

| IV.4. Mesures C/I                         | 211 |

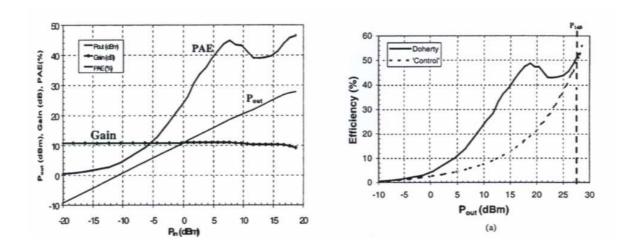

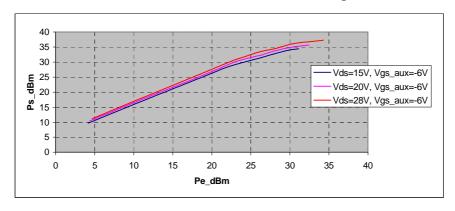

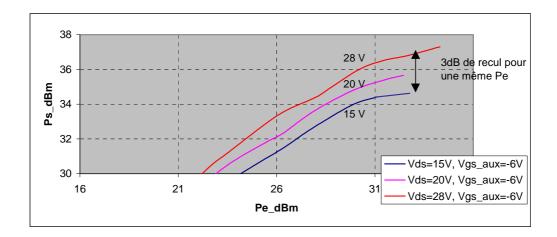

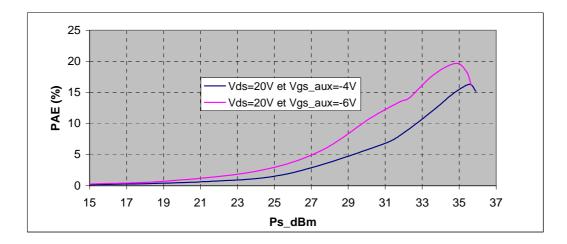

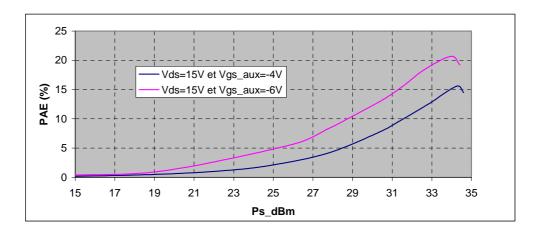

| IV.5. Mesures de flexibilité              | 213 |

| CONCLUSION                                | 216 |

| CONCLUSION ET PERSPECTIVES                | 219 |

# **INTRODUCTION GENERALE**

# **INTRODUCTION GENERALE**

Le développement des systèmes de communication s'inscrit dans un secteur de plus en plus concurrentiel. Au delà des contraintes de performances et de coût qui en découlent, les systèmes modernes doivent intégrer des possibilités de re-configurabilité pour traiter, le plus efficacement possible, l'information qu'ils acheminent qui peut croître en volume et être modifiée dans son format tout au long de l'exploitation du système.

Il en résulte une complexité toujours croissante d'architecture des systèmes, mais aussi des signaux modulés utilisés et du traitement numérique de ceux-ci.

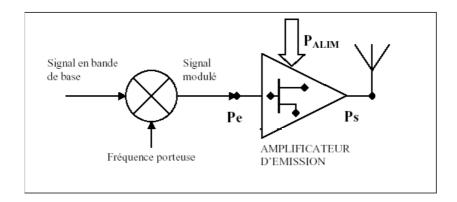

En ce qui concerne le segment analogique des systèmes, un des aspects réside dans la fonction d'amplification de puissance en émission.

Avec l'utilisation de signaux à forte efficacité spectrale qui sont des signaux à forte fluctuation de puissance, l'amplificateur doit satisfaire à des spécifications contraignantes de rendement et de linéarité.

Le rendement va conditionner la minimisation de la consommation du système et simplifier la gestion thermique. La linéarité est évidemment nécessaire pour respecter l'intégrité du signal transmis et elle est primordiale pour simplifier d'éventuels systèmes associés de linéarisation souvent synonymes de consommation supplémentaire non négligeable.

C'est dans ce cadre général que s'inscrivent ces travaux de thèse qui proposent l'étude et la conception d'un amplificateur intégrant des possibilités de flexibilité de puissance en conservant des bonnes performances en rendement et une sous contrainte de linéarité.

La conception optimisée d'amplificateurs de puissance ayant des topologies dites « non traditionnelles » passe obligatoirement par deux étapes essentielles :

- Une veille technologique concernant les composants semi-conducteurs candidats à l'amplification de puissance.

Une méthodologie de conception basée sur l'utilisation de modèles non linéaires de transistors précis et robustes pour effectuer des simulations grand signal.

Ces différentes étapes importantes ont été suivies au cours de ces travaux de thèse.

Le chapitre premier présente de manière générale les principales caractéristiques et potentialités des différentes technologies de transistors actuels pour l'amplification de puissance. Il est mis en évidence le très fort potentiel des transistors HEMT AlGaN/GaN pour l'amplification de très forte puissance dans le domaine micro-onde. Un tableau de synthèse de l'état de l'art publié à l'heure actuelle est donné.

Le chapitre deux s'attache à présenter les diverses étapes de modélisation non linéaire de transistor GaN. Un modèle intégrant les effets thermiques et de pièges présent dans la technologie GaN est proposé et a été élaboré pour un transistor de 900µm.

Le chapitre trois propose une synthèse des principales techniques de gestion de compromis rendement / linéarité dans les amplificateurs de puissance. Les différentes méthodes sont répertoriées en deux classes distinctes :

- Les techniques de linéarisation à proprement parlées, dont le principe directeur est le traitement du signal amplifié.

- Les techniques à haut rendement dont le principe directeur est le contrôle de polarisation et / ou de charge des cellules actives constituantes.

Ce chapitre se termine par une analyse du principe Doherty que nous retenons pour la suite de l'étude et le relevé des publications principales relatives à cette architecture d'amplificateur.

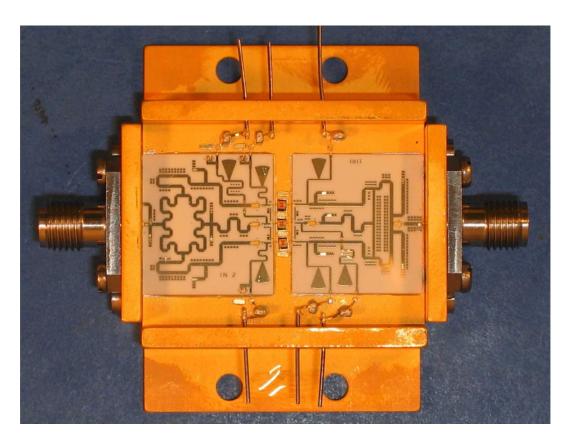

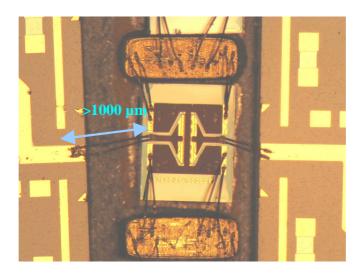

Le chapitre quatre traite de la conception d'un amplificateur Doherty à transistors GaN de puissance 10 Watts en bande X. L'architecture proposée est nouvelle à notre connaissance et offre l'avantage de symétrie qui est un critère intéressant en hyperfréquences. Les tests effectués sur la maquette réalisée ont visé essentiellement à valider l'effet Doherty et à montrer les capacités d'un tel amplificateur, à présenter un intérêt certain dans les systèmes

d'émission à flexibilité de puissance, fortement souhaité dans les applications spatiales et, en particulier, au sein de la société Alcatel Alenia Space Toulouse qui a soutenu ces travaux.

# **CHAPITRE I:**

Potentialité des différentes technologies de transistors pour l'amplification de puissance

# **INTRODUCTION:**

Ces dernières années, le besoin croissant de communiquer entre les hommes a conduit à un essor très important du secteur des télécommunications. Les rapides développements de la recherche et de l'industrialisation ont permis à un large public d'accéder aux moyens modernes de communication.

Cependant, il existe sans cesse un travail de recherche pour améliorer les différentes performances des systèmes de télécommunication. En effet, de nouvelles applications civiles ou militaires nécessitent l'utilisation de puissances plus importantes à des fréquences plus élevées.

C'est dans ce cadre là, que de nouvelles technologies dites « grands gaps » (Carbure de Silicium SiC et Nitrure de Gallium GaN) sont apparues pour la fabrication des transistors de puissance HF. Les propriétés physiques et électroniques de ces nouveaux matériaux semi-conducteurs permettent d'accroître les densités de puissances admissibles, ainsi que les fréquences de fonctionnement pour le GaN.

Un autre intérêt est également d'autoriser des températures de jonction plus élevées. Notons enfin qu'il est possible de générer la puissance RF dans des impédances de charge plus proches de 50 ohms comparativement aux autres technologies, ce qui permet de faciliter la conception et d'améliorer les performances des circuits de combinaison de puissance.

Dans ce chapitre, nous décrivons brièvement les différents types de transistors de puissance utilisés actuellement, par la suite, nous positionnons le transistor HEMT GaN par rapport aux autres technologies. De plus, un état de l'art des transistors de la technologie GaN est exposé. Enfin, nous terminerons ce premier chapitre en présentant les limites actuelles des semi-conducteurs en Nitrure de Gallium.

# I. Le GaN vis à vis des autres technologies de transistors de puissance.

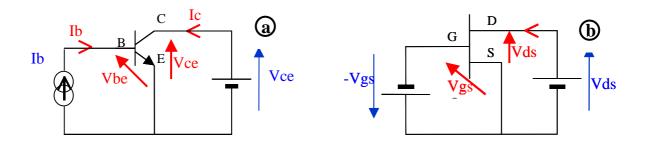

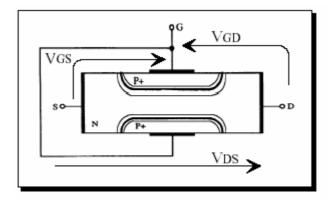

On distingue deux grandes familles de transistor : les transistors bipolaires (BJT) et les transistors à effet de champ (FET). En ce qui concerne les BJTs, les trois accès sont la base, le collecteur et l'émetteur. Un faible courant électrique appliqué sur la base permet la modulation du flux de courant entre le collecteur et l'émetteur (figure 1-a). Dans le cas des FETs, c'est la tension appliquée sur la grille qui permet de moduler le courant circulant entre le drain et la source (figure 1-b).

Figure 1 : Schématique des deux types de transistors : a) Transistor bipolaire b) Transistor à effet de champ

# I.1. Les transistors bipolaires

### I.1.1. Principe des transistors bipolaires à homojonction.

Historiquement, le transistor bipolaire à homojonction est le premier composant actif à semi-conducteur. Il a été inventé par Bardeen et Brattain en 1948. La théorie a été élaborée par Schokley en 1949 et le premier transistor a vu le jour en 1951.

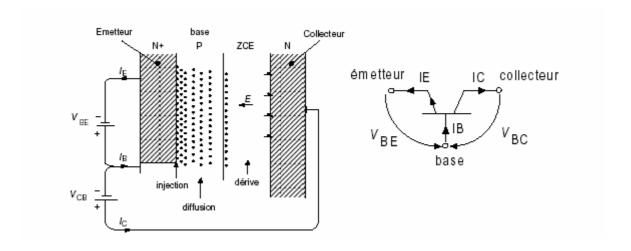

Un transistor bipolaire est un élément semi-conducteur constitué de deux jonctions PN tête-bêche présentant une région commune appelée base. Le collecteur et l'émetteur sont respectivement les deux régions restantes. Il peut y avoir deux types de transistors suivant que la région centrale est de type N ou P. Par exemple, la figure 2 présente une structure NPN polarisée dans son mode de fonctionnement dit « normal » ainsi que sa représentation schématique.

Figure 2 : Structure d'un transistor bipolaire

L'interaction forte entre la jonction émetteur-base et la jonction base-collecteur, induite par une faible épaisseur de base, est à l'origine de l'effet transistor. Ce dernier consiste à engendrer (comme le montre la Figure 2) un courant dans la jonction base-collecteur polarisée en inverse, par l'injection de porteurs minoritaires (ci-dessus des électrons) dans la base à partir de la jonction émetteur-base polarisée en direct. Pour cela, les porteurs minoritaires injectés dans la base par l'émetteur doivent se recombiner le moins possible. Il est donc nécessaire que l'épaisseur de base soit très inférieure à la longueur de diffusion des porteurs minoritaires.

Le transistor bipolaire possède différents régimes de fonctionnement qui diffèrent suivant les polarisations appliquées aux bornes des jonctions base-émetteur (BE) et base-collecteur (BC). On distingue les modes de fonctionnement suivants :

- normal : les jonctions BE et BC sont polarisées respectivement en direct et en inverse,

- saturé : les jonctions BE et BC sont toutes deux polarisées en direct,

- bloqué : les jonctions BE et BC sont toutes deux polarisées en inverse,

- inverse : les jonctions BE et BC sont polarisées respectivement en inverse et en direct.

# I.1.2. Transistors bipolaires à hétérojonction (TBH).

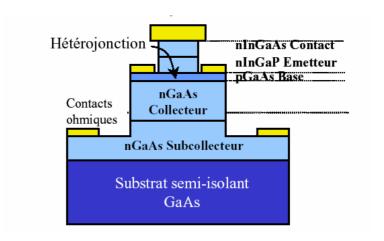

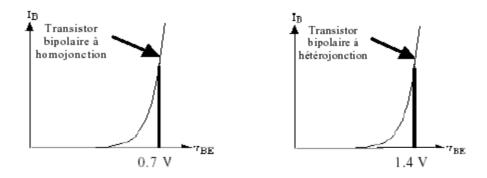

Le principe de fonctionnement du TBH (Figure 3) est proche de celui du transistor bipolaire à homojonction [1], [2]. La présence de l'hétérojonction entraı̂ne l'augmentation de la barrière de potentiel entre émetteur et base vue par les trous ; ce qui favorise le coefficient d'émission. L'étude phénoménologique d'un TBH est donc équivalente à celle d'un transistor bipolaire à homojonction ; la différence se traduit essentiellement par le décalage de la caractéristique courant / tension Ie = f(Vbe) (Figure 4).

De plus, pour un gain en courant identique, le dopage de base peut être plus important pour un TBH que pour un transistor bipolaire à homojonction. Ceci permet de diminuer la résistance de base et donc d'augmenter la fréquence maximale de fonctionnement.

Figure 3 : Vue en coupe d'un transistor bipolaire à hétérojonction

Figure 4 : Comparaison, transistors à homojonction et hétérojonction

# I.2. Les transistors à effet de champ.

# I.2.1. Principe.

Le principe du transistor à effet de champ (FET : Field Effect Transistor) a été décrit la première fois par Schockley en 1952 [3]. Il a été initialement appelé transistor unipolaire par opposition au transistor bipolaire car un seul type de porteur est utilisé (les électrons pour des raisons de célérité). L'effet fondamental est le suivant: le courant à contrôler circule dans un barreau de semi-conducteur appelé le canal, dont la section est contrôlée par l'application d'un champ électrique (Figure 5). Il existe deux types de modulation du canal, soit par enrichissement, soit par déplétion.

Figure 5 : Structure d'un transistor à effet de champ

Sur ce principe, différentes structures de transistors à effet de champ correspondant à différents contacts de grille ont été élaborées :

- le JFET (Junction Field Effect Transistor) : grille à jonction PN,

- le MOSFET (Metal Oxyde Semi-conductor Field Effect Transistor) : grille métallique isolée de la couche active par un oxyde isolant,

- le LDMOS (Lateraly diffused MOS)

- le MESFET (Metal Semi-conductor Field Effect Transistor) : grille métallique à barrière Schottky.

# I.2.2. Les transistors FET à hétérojonction

Le principe de fonctionnement des transistors à effet de champ à hétérojonction repose sur le principe de création et de contrôle d'un gaz d'électrons dans un matériau faiblement dopé où les électrons peuvent se déplacer plus rapidement.

A partir de cette structure conventionnelle, il existe plusieurs types de transistors à effet de champ à hétérojonction :

- le HEMT (**High Electron Mobility Transistor**);

- le TEGFET (Two dimensionnal Electron Gas Field Effect Transistor);

- le HFET (Heterostructure Field Effect Transistor);

- le MODFET (MOdulation Doped Field Effect Transistor) ;

- le PHEMT (Pseudomorphic Hight Electron Mobility Transistor);

- le PMHFET (**P**seudo**M**orphic **H**eterostructure **F**ield **E**ffect **T**ransistor).

Certains de ces transistors ont essentiellement des applications de puissance. Pour fabriquer ces transistors de puissance, plusieurs technologies de semi-conducteurs peuvent être envisagées. Le paragraphe suivant est une rapide présentation des différents transistors de puissance FET utilisés dans l'industrie et la recherche.

# I.3. Les principaux transistors FETs de puissance.

### I.3.1. Les transistors MOSFETs

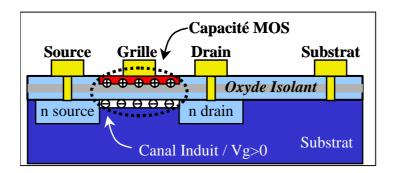

Le transistor MOSFET (*Metal Oxide Semiconductor Field Effect Transistor*) se caractérise par le dépôt d'une couche d'oxyde isolante entre la grille et le substrat constituant ainsi une capacité MOS (Figure 6) chargée d'enrichir ou d'appauvrir le canal de conduction entre la source et le drain par une tension de grille positive, [4],[5],[6].

Figure 6 : Vue en coupe d'un transistor MOSFET

Pour l'amplification de puissance aux fréquences micro-ondes, les transistors MOS classiques sont limités du fait de leur faible tension de claquage.

### I.3.2. Les transistors LDMOS

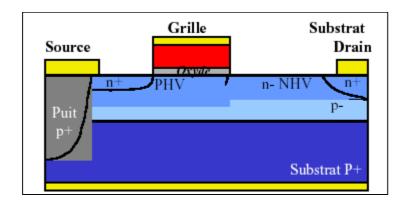

Une des filières développées, pour pallier les limites en puissance du MOSFET, est celle du LDMOS (*Lateraly diffused MOS*). Il se distingue du MOSFET par un puit dopé p+ (Figure 7) jouant le rôle de masse RF entre la source et la face arrière du composant.

Figure 7 : Vue en coupe d'un transistor LDMOS

Les transistors LDMOS sont des composants très répandus dans les stations de base pour téléphonie mobile. Dans une bande de fréquence limitée à environ 3 GHz, ils possèdent de très hautes tensions de claquage, ce qui permet des niveaux de polarisation élevés. Ericsson-Infineon [7] a développé un transistor LDMOS avec une tension de claquage égale à

110 V qui atteint une densité de puissance de 1W/mm @ 3.2 GHz pour une polarisation de 50 V et 2W/mm @ 1 GHz pour une polarisation de 70 V.

La tension de claquage du LDMOS dépend directement de la distance séparant la grille du drain. Les mesures sur LDMOS de 10mm [8] montrent qu'une variation de la distance grille drain de 2 à 4 $\mu$ m permet une augmentation de la tension de polarisation de drain de 32 à 40 V.

Cependant, un gain en puissance élevé à haute fréquence nécessite que le canal soit le plus court possible, favorisant le transit rapide des électrons. Ce constat s'oppose à l'augmentation de la distance grille drain. Ce type de transistor est donc limité à des fréquences d'utilisation maximales en bandes L ou S.

### I.3.3. Les transistors HEMTs AsGa et PHEMTs AsGa

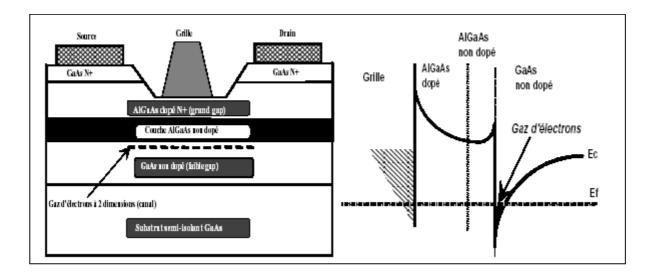

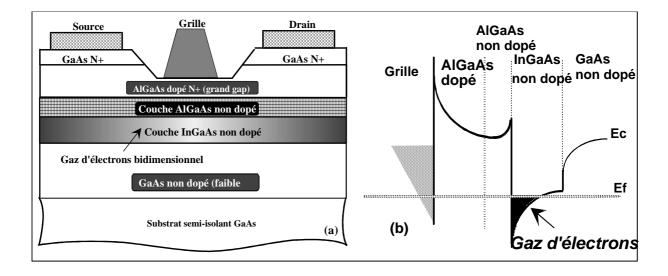

La structure des couches épitaxiées des HEMTs présente une hétérojonction, une jonction entre deux matériaux ayant des énergies de bande interdite différentes. La conséquence de cette hétérojonction est la création d'un canal très fin dans le matériau non dopé de très faible résistance, entraînant une mobilité d'électrons élevée (origine du nom HEMT). Cette couche est appelée gaz d'électrons à deux dimensions (origine du nom TEGFET). Ainsi la différence essentielle entre les MESFETs et les HEMTs se situe au niveau du principe même du contrôle du courant dans le canal. Alors que dans le cas du MESFET, l'électrode de grille contrôle la section de canal disponible pour la conduction, dans le cas du HEMT, elle contrôle la densité d'un gaz d'électrons libres dans une zone non dopée située sous l'hétérointerface qui constitue le canal du transistor. La Figure 8 représente la structure de couches ainsi que le diagramme de bande d'énergie d'un HEMT classique utilisant l'AsGa et l'AlGaAs comme couches actives.

Figure 8 : Structure de principe d'un HEMT classique associée à son diagramme de bande d'énergie

Si le HEMT a permis des utilisations en fréquence bien plus hautes que celles du MESFET, sa limite fréquentielle est de l'ordre de 60-70 GHz. Cette limite est principalement due aux propriétés de transport du matériau intrinsèque, c'est-à-dire l'Arséniure de Gallium.

Il est le composant privilégié pour des applications de puissance hautes fréquences ainsi que pour des applications à faible bruit telles que les circuits de pré-amplification des satellites ou encore les oscillateurs. En conséquence pour satisfaire aux besoins sans cesse croissants de montée en fréquence, l'idée de base a été de remplacer le GaAs du canal par un autre matériau à faible gap autorisant une vitesse à fort champ électrique la plus élevée possible : l'InGaAs. Les progrès technologiques en matière d'épitaxie ont donné, par la suite, naissance à un nouveau type de transistor à hétérojonction : le HEMT pseudomorphique (PHEMT).

Les transistors à effet de champ pseudomorphiques GaAs (*pseudomorphic HEMTs*) se différencient des transistors HEMTs par l'ajout d'une couche d'InGaAs intercalée entre les couches AlGaAs et GaAs (Figure 9). Par conséquent, la discontinuité de la bande de conduction à l'interface AlGaAs/InGaAs est plus large que dans le cas AlGaAs/GaAs. Le puits de potentiel étant plus large que dans le cas d'une structure HEMT classique, le courant dans ce transistor est donc plus élevé. De plus, la vitesse des électrons dans l'InGaAs (non

dopé) est également plus importante que dans le GaAs ce qui permet de très hautes fréquences de travail.

Figure 9 : Structure d'un transistor PHEMT GaAs associée à son diagramme de bande

Durant ces dernières années, les tensions d'avalanche ont été fortement augmentées, permettant ainsi de polariser les transistors à effet de champ avec une tension de drain supérieure à 20 V [9],[10],[11].

Ces fortes tensions de polarisation autorisent donc des densités de puissance plus importantes. Cependant, les transistors PHEMTs GaAs atteignent des densités de puissance de l'ordre de 2W/mm [12], [13], qui sont toujours très inférieures aux transistors grand gap (>10W/mm). Par conséquent, seuls des amplificateurs à plusieurs transistors connectés en parallèle peuvent convenir pour des applications de forte puissance micro-ondes, avec des tailles de transistor relativement importantes et des difficultés d'adaptation et de combinaison de puissance dues aux très faibles impédances de charge.

# I.3.4. Les transistors de puissance grand gap.

De récents développements ont permis l'élaboration de composants supportant des puissances bien supérieures aux transistors dits classiques. Aujourd'hui, les semi-conducteurs à large bande interdite sont les candidats idéaux pour réaliser des conceptions pour des applications de puissance. Leurs propriétés physiques (champ électrique de claquage, vitesse de saturation, conductivité thermique) en font des matériaux sans rivaux pour un grand nombre d'applications de forte puissance et à haute température. Les semi-conducteurs à grande bande interdite permettent d'étendre l'utilisation des dispositifs électroniques dans le domaine des hautes températures, du fait de la grande bande interdite, et des fortes puissances, du fait du fort champ électrique de claquage.

Il existe aujourd'hui deux principaux semi-conducteurs grand gap : les MESFETs en Carbure de Silicium (SiC) et les HEMTs en Nitrure de Gallium (GaN).

### I.3.4.1. Les transistors MESFETs SiC

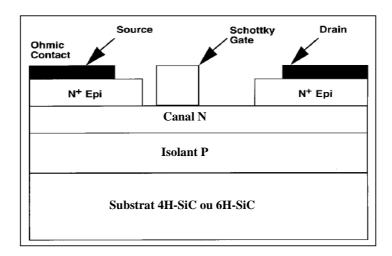

Le fonctionnement du MESFET (Figure 10) est basé sur la modulation de l'épaisseur du canal sous la grille. L'ensemble, constitué par la métallisation de grille et le semi-conducteur (SC) de type N au dessous de la grille, forme une jonction ou diode Schottky. La présence de ce contact justifie la dénomination MESFET (MEtal Semi-conductor Field Effect Transistor).

Une tension appliquée entre les contacts ohmiques de drain et de source fait circuler un courant d'électrons parallèlement à la surface du semi-conducteur. La saturation de ce courant est due à la saturation de la vitesse des électrons. L'intensité du courant dans les transistors MESFETs est contrôlé grâce à la modulation de la section du canal contrairement aux transistors MOSFETs et HEMTs où le contrôle du courant se fait par la modulation de la densité des porteurs. Plus précisément, l'intensité du courant est contrôlée par la profondeur de la zone déplétée, qui apparaît sous la jonction métal/semi-conducteur (contact Schottky) constituant la grille.

Figure 10 : Structure d'un MESFET sur 4H-SiC

Les performances en fréquence des transistors MESFETs sont conditionnées par la longueur de la grille. En effet, plus celle-ci est courte, plus les fréquences de transition et maximale d'oscillation sont importantes. Cependant, réduire la longueur de grille revient à augmenter sa résistance.

Les premiers transistors MESFETs sur Carbure de Silicium ont été réalisés à partir du polytype 6H-SiC parce que celui-ci présente de meilleures qualités cristallines. Ainsi, différentes équipes de recherche ont mis au point des transistors MESFETs 6H-SiC, en particulier l'équipe de J.W. Palmour à Cree Research [14]. Puis, rapidement, le polytype 4H-SiC est apparu plus intéressant : en effet, ce polytype possède une mobilité dont la valeur est deux fois la valeur de la mobilité du 6H-SiC. Grâce à ses propriétés physiques et électriques comparables à celles du polytype 6H-SiC, le polytype 4H-SiC s'est avéré être le candidat idéal pour réaliser des transistors MESFETs de puissance.

En 1994, Charles E. Weitzel [15] de Phoenix Corporate Research Laboratories / Motorola présente les résultats en puissance obtenus avec un transistor MESFET 4H-SiC dont la coupe transversale est donnée sur la Figure 11.

Il s'agit d'un transistor de deux doigts de grille, la largeur d'un doigt de grille étant de 166 μm et la longueur de grille de 0,7 μm. La structure de ce transistor est constituée par :

- un substrat 4H-SiC dopé N sur lequel on a déposé une couche épitaxiale semiisolante dopé  $p = 1,4 \times 10^{15} \text{cm}^{-3}$ , de 6 $\mu$ m d'épaisseur,

- le canal est dopé  $Nd = 1.7 \times 10^{17} \text{cm}^{-3}$  et a une profondeur de  $0.25 \, \mu \text{m}$ ,

- sous les contacts de drain et de source, les zones dopées N+ ( $N+ \ge 2x10^{19} cm^{-3}$ ) de  $0.15 \, \mu m$  de largeur sont obtenues par croissance épitaxiale et par gravure chimique.

Figure 11: Coupe transversale d'un transistor MESFET 4H-SiC

Charles Weitzel s'est intéressé aux performances hyperfréquences et en puissance de ce transistor MESFET 4H-SiC et a obtenu les résultats suivants :

- une fréquence maximale d'oscillation de 12,9 GHz et une fréquence de transition de 6,7 GHz. Ces fréquences ont été calculées à partir des paramètres [S] mesurés sur la bande de fréquence [45 MHz 26,5 GHz] et au point de polarisation Vds = 30 V, Ids = 78 mA, Vgs = 1 V (et Ig < 1 pA). Le gain petit signal, à ce même point, était de 9,3 dB à 4 GHz et 2,2 dB à 10 GHz,

- la densité de courant de drain est de 300~mA/mm à Vds = 25~V associée à une transconductance gm de 38 à 42~mS/mm,

- des mesures en puissance ont été effectuées à l'aide d'un banc de type load Pull. Le transistor était polarisé au point Vds = 54 V, Vgs = -2 V et Ids = 77,4 mA. La puissance de sortie maximale est de 29,72 dBm (0,937 W) associée à un gain de 6,7 dB et un rendement en puissance ajoutée de 12,7 % pour un niveau de puissance d'entrée de 23 dBm. La densité de puissance est de 2,8 W/mm.

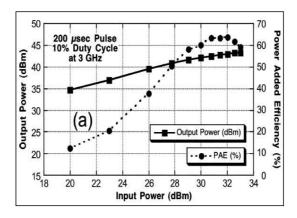

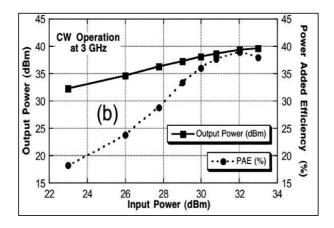

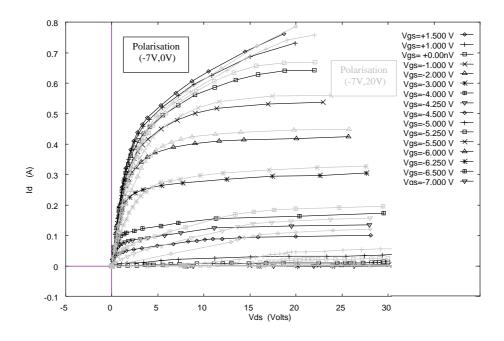

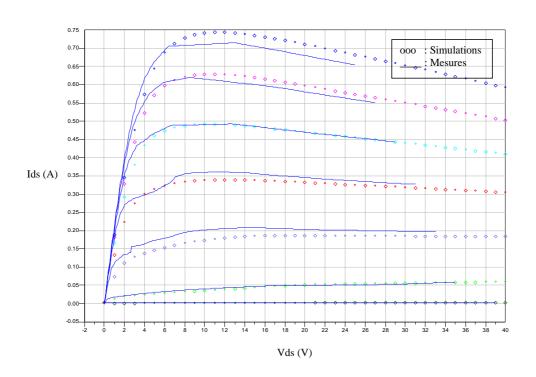

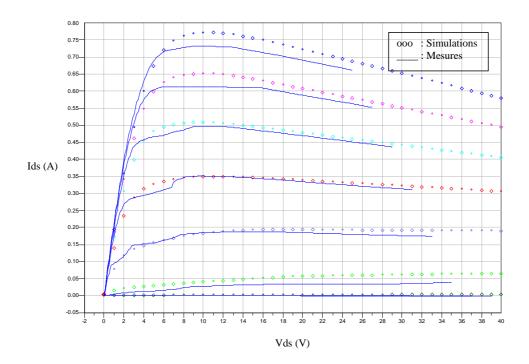

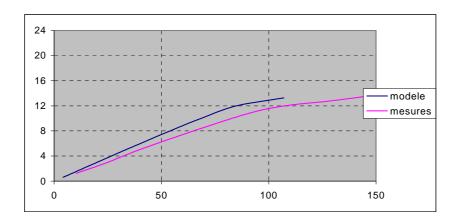

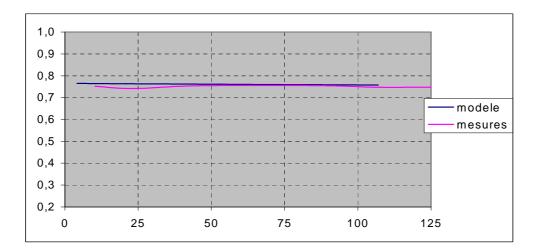

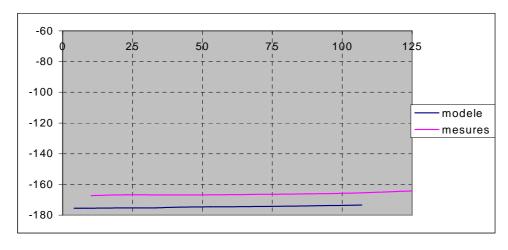

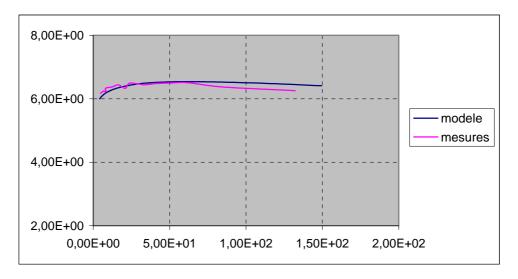

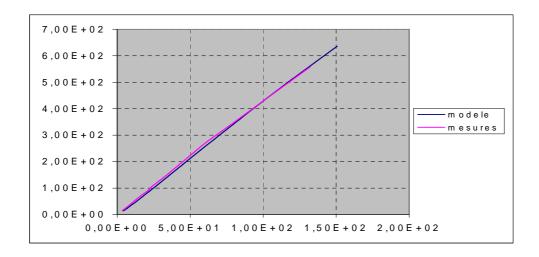

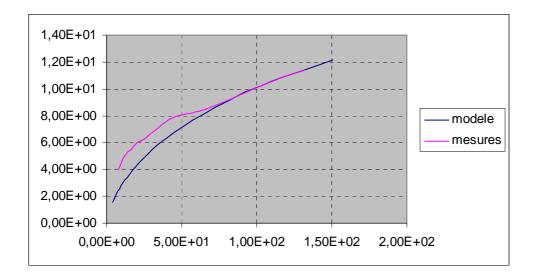

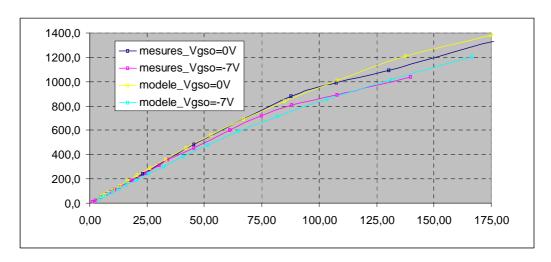

En juin 2004, H. George Henry [16] présente de très bons résultats à partir d'un MESFET SiC de 4.8 mm de développement fonctionnant à 3 GHz. Ce MESFET se différencie d'un MESFET classique par l'ajout d'un « spacer » de 200 Å en SiC non dopé entre le canal et la grille, minimisant ainsi les pièges de surface. Une première série de mesures grand signal pulsé (Figure 12) est effectuée avec une polarisation en classe AB avec *Vgs* pulsée et *Vds* continue (durée de pulse=200µs, rapport cyclique= 10 %). Ce transistor MESFET SiC délivre alors une puissance de sortie égale à 21 W (soit environ 4.4 W/mm), avec un *PAE* de 62 % et un gain en puissance de 10.6 dB. Une deuxième série de mesures grand signal CW (Figure 13) est effectuée avec les mêmes valeurs de tensions de polarisation mais en mode continu. Les performances de ce transistor MESFET SiC sont alors en retrait par rapport à celles obtenues en condition pulsée. Il délivre tout de même une puissance de sortie de 9.2 W (soit environ 2 W/mm), avec un *PAE* de 40 % et un gain en puissance de 7 dB pour une fréquence de travail toujours égale à 3GHz.

Figure 12 : Mesures grand signal d'un transistor MESFET SiC de 4.8mm de développement de grille en condition pulsée (durée de pulse=200µs, rapport cyclique= 10 %) @ 3GHz

Figure 13: Mesures grand signal CW du même transistor MESFET SiC de 4.8mm de développement de grille @ 3GHz

Cependant, le Carbure de Silicium est souvent très mal contrôlé du point de vue des défauts structuraux ou ponctuels. Ces défauts sont à l'origine d'un phénomène parasite appelé phénomène de pièges qui dégrade considérablement les performances RF des dispositifs SiC.

### I.3.4.2. Les transistors HEMTs GaN

Il existe trois types de semi-conducteurs en Nitrure de Gallium rencontrés dans la littérature : le HFET GaN, le MODFET GaN et le HEMT GaN.

Cependant, lors de cette thèse, nous allons juste nous intéresser au HEMT GaN parce qu'il est le composant le plus mature et le plus rencontré dans les différents laboratoires ainsi que chez les industriels.

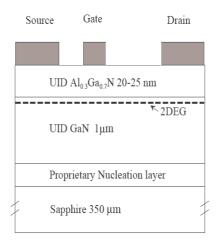

Pour mieux comprendre son fonctionnement, nous allons étudier brièvement les structures de bande des matériaux mis en jeu dans un HEMT AlGaN/GaN [17] qui est la technologie étudiée au cours de ces travaux de thèse (Figure 14).

Figure 14 : Structure physique de base d'un HEMT sur substrat Sapphire

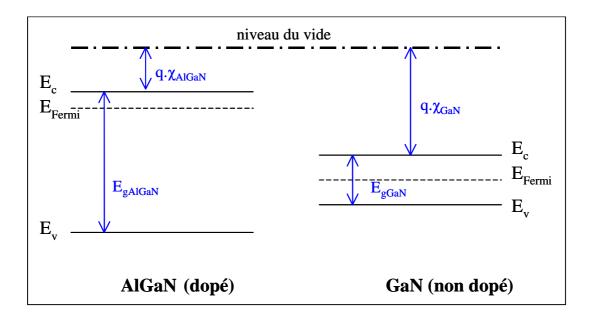

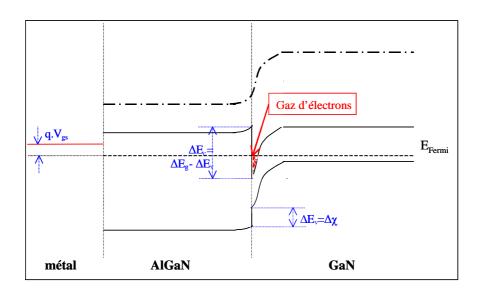

L'hétérojonction formée par la juxtaposition de deux matériaux dont les largeurs de bande interdite sont différentes, l'un présentant un large gap (AlGaN : 3,82eV) et l'autre un gap plus faible (GaN : 3,4eV), entraı̂ne la formation d'une discontinuité de la bande de conduction à l'interface ( $\Delta E_c$ ). La Figure 15 présente les niveaux d'énergie mis en jeu dans chacun des matériaux de l'hétérojonction considérés séparément, c'est-à-dire avant contact.

Figure 15 : niveaux d'énergie des matériaux mis en jeu dans l'hétérojonction

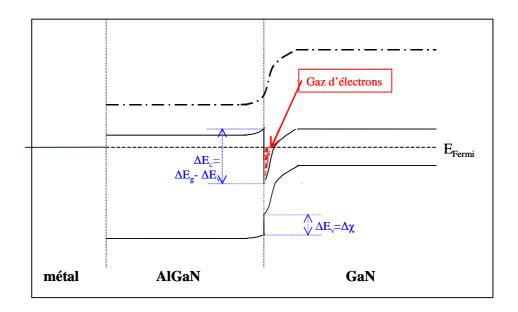

D'après les règles d'Anderson, lors de la jonction de deux matériaux, leur niveau de Fermi s'aligne. Le niveau du vide ne pouvant pas subir de discontinuités, il en résulte une discontinuité de la structure de bande d'énergie à l'interface. La Figure 16 montre les niveaux d'énergie à l'hétérojonction pour une tension appliquée nulle.

Figure 16 : niveaux d'énergie des matériaux à l'hétérojonction pour une tension appliquée nulle

Nous pouvons observer la formation d'un puit quantique à l'interface, dans le matériau de plus faible largeur de bande interdite. Ce puit reste cantonné dans la partie supérieure du matériau à plus faible gap non dopé car, au-dessus, le matériau de plus grande largeur de bande interdite joue le rôle de barrière. C'est dans ce puit que se regroupent les charges libres entraı̂nant le phénomène de conduction à l'origine de la formation d'un gaz d'électrons à deux dimensions : c'est le canal. La densité de porteurs dans ce canal dépendra du niveau de Fermi dans la bande interdite du matériau (niveau de dopage), de la différence de largeur de cette bande entre les deux matériaux ( $\Delta E_g$ ) et du dopage considéré. Par exemple, la Figure 17 montre les niveaux d'énergie mis en jeu à l'hétérojonction lorsqu'on applique une tension sur la grille du composant. On voit en effet une modulation de ce gaz d'électrons et donc de la concentration de porteurs dans le canal. C'est pourquoi une tension appliquée sur la grille d'un HEMT permet le contrôle du courant qui circule entre drain et source.

Une saturation du courant s'observe en raison de la vitesse de saturation des électrons pour des fortes valeurs de tension entre drain et source. Si l'on compare une fois encore le HEMT au MESFET, la mobilité des électrons étant plus élevée dans un gaz que dans un matériau dopé, il est plus rapide que ce dernier, permettant des applications à plus haute fréquence.

Figure 17 : niveaux d'énergie des matériaux à l'hétérojonction pour une tension appliquée non nulle

L'autre particularité du fonctionnement d'un HEMT, outre l'existence d'un gaz d'électrons, est la jonction Schottky créée par la jonction métal de grille et semi-conducteur du substrat.

Comparés aux résultats obtenus avec des MESFETs 4H SiC, avec des densités de puissance similaires à une fréquence de fonctionnement de 10 GHz, les transistors HEMTs AlGaN/GaN présentent de meilleures performances en fréquence. Par conséquent, pour des applications de très forte puissance à très hautes fréquences où les performances des FETs SiC sont relativement médiocres, les FETs GaN sont une solution indéniable.

Lors de ce paragraphe, nous avons recensé les différents transistors de puissance rencontrés dans la littérature. Une synthèse de leurs propriétés est effectuée dans le paragraphe suivant.

### I.4. Synthèse: comparaison des propriétés des transistors de puissance FETs.

I.4.1. Comparaison des paramètres physiques des semi-conducteurs

Le tableau suivant recense quelques caractéristiques physiques des principaux matériaux utilisés pour la réalisation de transistors hyper-fréquences [18].

|                                                                        | Silicium | Arséniure de<br>Gallium | Carbure de<br>Silicium | Nitrure de<br>Gallium |

|------------------------------------------------------------------------|----------|-------------------------|------------------------|-----------------------|

| Largeur de bande<br>interdite (eV)                                     | 1.1      | 1.43                    | 3.26                   | 3.39                  |

| Champ critique<br>(10 <sup>6</sup> V/cm)                               | 0.3      | 0.4                     | 3                      | 3.3                   |

| Mobilité des électrons à 300°K (cm².V <sup>-1</sup> .S <sup>-1</sup> ) | 1350     | 6000                    | 800                    | 1500                  |

| Conductivité thermique<br>(W.cm <sup>-1</sup> .K <sup>-1</sup> )       | 1.5      | 0.5                     | 4.9                    | 1.7                   |

| Constante diélectrique                                                 | 11.8     | 12.5                    | 10                     | 9                     |

| Température max (°C)                                                   | 300      | 300                     | 600                    | 700                   |

Ce tableau nous renseigne sur les différents points suivants:

La largeur de bande interdite représente l'intervalle situé entre le niveau inférieur de la bande de conduction et le niveau supérieur de la bande de valence d'un matériau. L'énergie de bande interdite est une mesure de la quantité d'énergie nécessaire à un électron pour passer de la bande de valence à la bande de conduction sous l'impulsion d'une excitation thermique ou autre. Cette quantité est un facteur de la capacité du matériau à supporter une forte température ; elle définit la température maximale de fonctionnement du transistor. Donc, plus la largeur de bande est importante, plus le transistor peut fonctionner à haute température. On peut donc voir que les matériaux SiC et GaN sont des candidats propices pour un fonctionnement à température élevée.

Le champ critique est la valeur du champ électrique que peut supporter le composant. Plus cette caractéristique est élevée, plus le composant sera capable de supporter des tensions de polarisation importantes. Le tableau montre que les semi-conducteurs grand gap (SiC et GaN) ont un champ critique près de 8 fois plus élevé que le Si et l'AsGa. On peut en conclure que les transistors grand gap sont excellents pour des applications de puissance.

\_ Une faible mobilité des électrons induit une augmentation de la résistance parasite, soit plus de pertes et moins de gain. De plus, ces effets s'intensifieront pour des fonctionnements aux hautes fréquences. On peut en conclure que le matériau AsGa est très propice aux applications très hautes fréquences. On peut cependant remarquer que le GaN a une mobilité des électrons deux fois plus importantes que le SiC. Le GaN permet alors de pouvoir travailler à plus haute fréquence que le SiC.

La conductivité thermique d'un matériau traduit sa capacité à évacuer la chaleur du composant. La chaleur non dissipée provoque une élévation de température du composant qui va entraîner une diminution du rendement. D'après le tableau, pour les applications de puissance, il est donc préférable de privilégier les transistors grand gap (essentiellement le SiC).

I.4.2. Comparaison des transistors sur les caractéristiques de fréquence et de puissance.

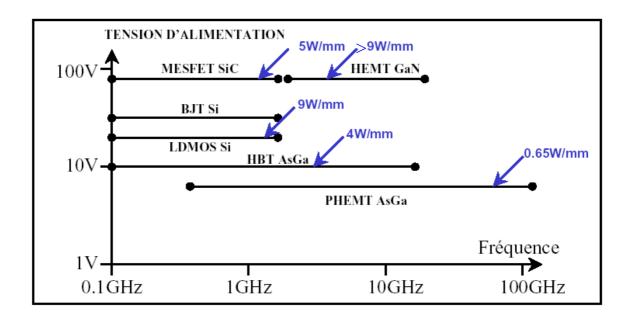

La Figure 18 montre les tensions d'alimentation possibles en fonction de la fréquence de travail du composant. On observe notamment que les transistors dits « petits gaps » ont des tensions d'alimentations peu importantes alors que pour les transistors MESFETs SiC et HEMTs GaN, les tensions maximales peuvent dépasser les 100 V. Cependant, l'avantage du Nitrure de Gallium est une utilisation possible pour des fréquences beaucoup plus élevées que le Carbure de Silicium. Ainsi, ce tableau démontre que HEMT GaN est un candidat idéal pour une application de forte puissance en bande X.

Figure 18 : comparaison de différentes technologies pour l'amplification de puissance

# II. Etat de l'art des transistors de puissance GaN.

### II.1. Historique

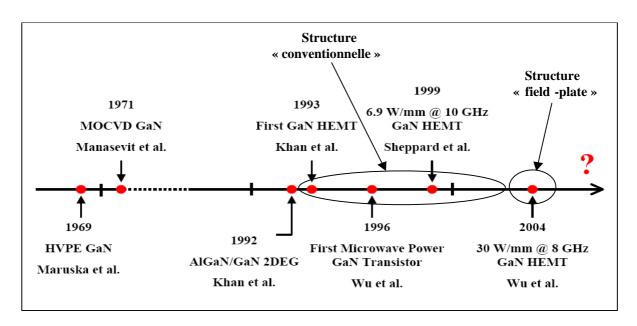

Les premiers transistors HEMTs GaN sur substrat saphir, silicium et carbure de silicium sont apparus au milieu des années 90. Mais il faut attendre la fin des années 90 et début 2000 pour trouver des résultats très intéressants en terme de puissance et/ou de fréquence.

En 1999, S.T. Sheppard (Cree) [19] présente des travaux sur un transistor HEMT GaN (substrat SiC) avec une densité de puissance de 6.9 W/mm à 10GHz.

Au sein du laboratoire IRCOM [20], un transistor HEMT GaN sur substrat SiC issu du laboratoire Tiger de 1.2mm de développement de grille a délivré une puissance de sortie de 6.7 W (5.6 W/mm) avec un *PAE* de 40 % et un gain en puissance associé de 6.5dB à une fréquence de 10 GHz lors de mesures grand signal en régime CW.

De très bon résultats ont aussi été obtenus à partir de transistors HEMTs GaN sur substrat silicium avec des densités de puissance de 1.9 W/mm (Tiger) [21] à 10 GHz allant jusqu'à 12 W/mm à 2.14GHz (Nitronex) [22].

Très récemment, des sociétés comme CREE et SOITEC ont commencé à proposer des wafers GaN, tout en continuant leur production de wafers SiC beaucoup plus matures. Les travaux de K. K. Chu font état d'un transistor HEMT AlGaN/GaN sur substrat GaN polarisé à 50 V sur le drain, ayant une densité de puissance de 9.4 W/mm avec un *PAE* associé de 40 % à 10 GHz [23].

Nous constatons donc que tous les résultats présentés jusqu'ici, et obtenus avec des transistors HEMTs à structure conventionnelle, ne dépassent pas les 10 W/mm pour des applications bande X [24] .

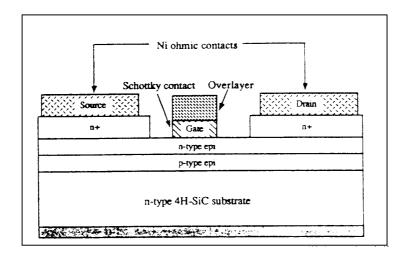

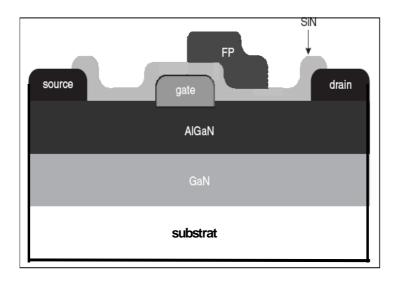

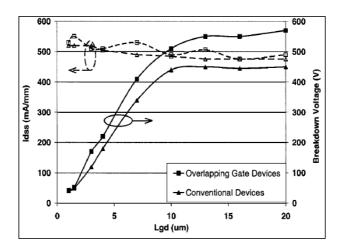

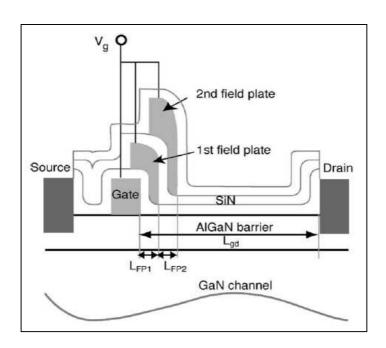

Or début 2004, un saut technologique a été franchi avec l'ajout d'une métallisation de grille, appelée « field plate » ou « overlapping gate » (Figure 19), située au-dessus de la couche de passivation du composant. Ces nouvelles structures field plate permettent d'atteindre des densités de puissance exceptionnelles jusqu'à 30 W/mm [25], [26].

Figure 19: structure d'un transistor HEMT GaN avec field-plate

Les premiers travaux relatant l'emploi de cette technologie field-plate datent du début des années 90. En effet, en 1992. C.L. Chen (Laboratoire Lincoln du Massachusset) présente un transistor MESFET GaAs avec field plate ayant une tension de claquage grille-drain de 42V [27]. Cette métallisation au-dessus de la couche de passivation permet de modifier le profil de la distribution du champ électrique du bord de la grille coté drain et de réduire le pic du champ électrique critique, augmentant ainsi la tension d'avalanche (Figure 20).

Figure 20 : courant maximum de sortie et tension d'avalanche drain source obtenus pour un transistor HEMT GaN conventionnel et pour un transistor avec field plate en fonction de la distance grille drain

Afin d'augmenter encore la tension d'avalanche, un transistor HEMT GaN à double field plate (Figure 21) possédant une tension d'avalanche de 900 V à été présenté par H. Xing (Université de Californie) [28].

Figure 21: structure d'un transistor HEMT GaN à double field plate

Y.-F. Wu (Cree) [26] obtient les meilleures densités de puissance actuelles, à savoir une densité de puissance supérieure à 30 W/mm à partir de transistors HEMTs GaN sur SiC avec un seul field plate. Les résultats exacts des mesures grand signal CW obtenus pour une tension de polarisation continue de drain égale à 120 V sur deux transistors (taille de 246µm) quasi identiques (longueur de field plate différente), sont les suivants :

=> une densité de puissance de 32.2 W/mm, un *PAE* de 54.8 %, un gain en puissance de 14 dB à 4 GHz pour une longueur de field plate égale à 1.1 μm

=> une densité de puissance de 30.8 W/mm, un *PAE* de 49.8 %, un gain en puissance de 10.7 dB à 8 GHz pour une longueur de field plate égale à 0.9 μm

Cependant, la présence du field plate augmente la capacité grille-drain et réduit ainsi quelque peu les performances en fréquence de ces transistors.

Chaque année, de nouveaux travaux sont publiés relatant des résultats obtenus toujours plus performants. Notamment en 2005 où le nombre de publications sur des résultats de puissance obtenus par des transistors HEMTs GaN a fortement progressé. La Figure 22 présente de façon chronologique les meilleures performances obtenues avec des transistors HEMTs GaN jusqu'à aujourd'hui.

Figure 22 : principaux résultats obtenus en terme de puissance et de fréquence à partir de transistors HEMTs GaN

# II.2. Tableau des performances relevées sur les transistors de puissance GaN.

Le tableau présenté ci-dessous est la synthèse de l'état de l'art des derniers composants HEMTs GaN portés à notre connaissance.

| laboratoires                               | Substrat | Fréquence | Densité de<br>puissance | Tension de<br>drain | PAE    | Publication        |

|--------------------------------------------|----------|-----------|-------------------------|---------------------|--------|--------------------|

| HRL<br>laboratorie<br>Malibu / ONR         | SiC      | 30 GHz    | 5.7 W/mm                | 20V                 | 45 %   | Juin 2005<br>[29]  |

| University of california                   | Si       | 4 GHz     | 3.3 W/mm                | 25V                 | 54 %   | Mai 2005<br>[30]   |

| TIGER                                      | Si       | 18 GHz    | 5.1 W/mm                | 35 V                | 20 %   | 2005<br>[31]       |

| ONR                                        |          | 40 GHz    | 10.5 W/mm               | 30 V                | 34 %   | Nov. 2005<br>[32]  |

| National<br>Central<br>Univesity<br>Taiwan | Sapphire | 2.4GHz    | 4 W/mm                  | 30V                 | 38 %   | Janv.2005<br>[33]  |

| Nitronex<br>Corporation                    | Si       | 2.14 GHz  | 2.1 W/mm                | 28 V                | 65%    | Juin 2005<br>[37]  |

| RF Micro<br>Devices                        | SiC      | 2.14 GHz  | 22.7 W/mm               | 80 V                | 55%    | Juin 2005<br>[34]  |

| Mitsubishi<br>Electric<br>Corporation      | SiC      | Bande C   | 2.79 W/mm               | 40 V                | 25%    | Juin 2005<br>[36]  |

| Cornell                                    | SiC      | 10 GHz    | 16.5 W/mm               | 60 V                | 47%    | Fév. 2004<br>[35]  |

| Cree                                       | SiC      | 4 GHz     | 32.2 W/mm               | 120 V               | 54.8 % | Mars 2004<br>[26]  |

| BAE systems                                | GaN      | 10 GHz    | 9.4 W/mm                | 50 V                | 40%    | Sept. 2004<br>[23] |

| Daimler<br>Chrysler                        | Si       | 2 GHz     | 6.6 W/mm                | 30 V                | 49%    | Avril 2003<br>[38] |

| Emcore<br>Corporation                      | SiC      | 18 GHz    | 9.1 W/mm                | 55V                 | 23.7 % | Sept 2005<br>[39]  |

| Hong-Kong<br>University                    | Sapphire | 4 GHz     | 3.26 W/mm               | 8 V                 | 55.6%  | Déc. 2005<br>[40]  |

Cette prolifération de publications traduit un début de maturité de fabrication de ces semi-conducteurs GaN et l'engouement des différents laboratoires internationales pour cette technologie.

Le tableau ci-dessous recense les caractéristiques électriques des principaux transistors GaN commercialisés:

| Industries | Puissance de sortie | Fréquence | Tension de<br>drain | PAE  | Gain    |

|------------|---------------------|-----------|---------------------|------|---------|

| Nitronex   | 50 W                | 3.5 GHz   | 28 V                | 50 % | 10.5 dB |

| Eudyna     | 45 W                | 2.2 GHz   | 50 V                | 60 % | 12 dB   |

| RFHIC      | 10 W                | 2.14 GHz  | 28 V                | 55 % | 10 dB   |

# III. Limitations actuelles : effets thermiques et phénomènes de pièges.

Les fortes densités de puissance admissibles sur les technologies grands gaps vont entraîner un échauffement important du transistor, la vitesse de saturation des porteurs va diminuer à son tour entraînant une diminution de la puissance de sortie et de la fréquence de transition jusqu'à atteindre un état établi. Ce sont ces phénomènes thermiques dus à l'auto-échauffement que nous allons étudier dans un premier temps.

De plus, la technologie récente de ces transistors HEMTs présente des défauts de structure. Cela se traduit par les effets de pièges qui affectent considérablement la puissance de sortie des transistors (gate-lag, drain-lag). Nous étudierons ces phénomènes dans un deuxième temps.

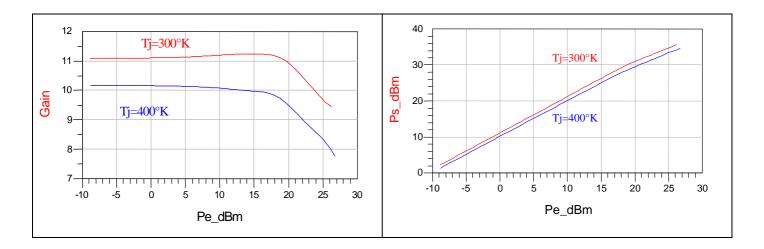

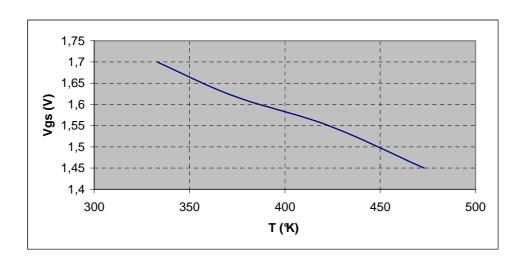

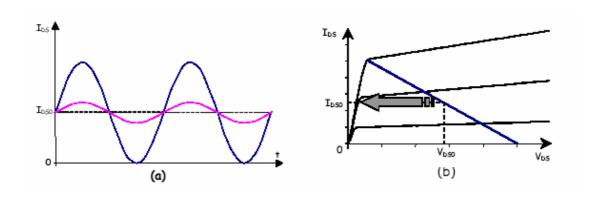

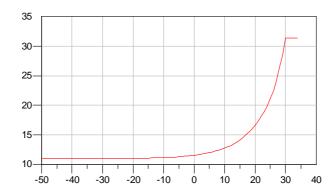

### III.1. Les effets thermiques dans les transistors HEMTs GaN

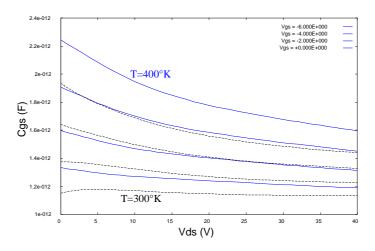

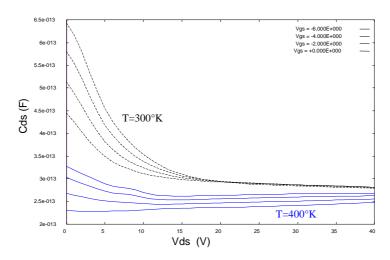

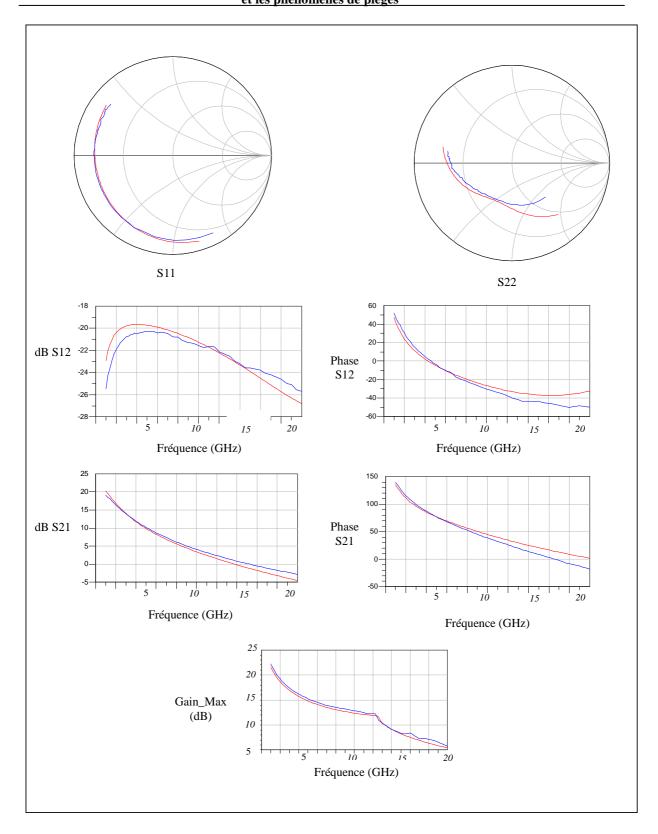

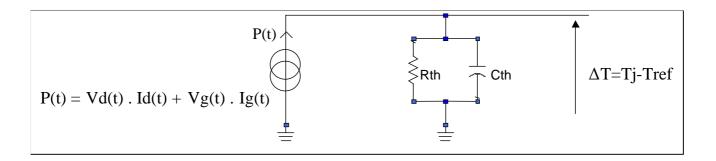

L'état thermique d'un composant résulte de la température ambiante et de l'autoéchauffement du transistor [41]. L'auto-échauffement du transistor se traduit par une puissance dissipée dépendant de la classe de fonctionnement du transistor et des performances RF de celui-ci vis-à-vis du signal injecté. Ainsi, lorsque la puissance dissipée augmente, la température de jonction notée Tj augmente, faisant diminuer la mobilité des porteurs. Cela se traduit par une chute de la puissance de sortie du dispositif ainsi que par une baisse des fréquences de transition et maximales d'oscillation. En clair, une forte élévation de température altère de façon importante les performances des transistors. Pour montrer cet effet, nous simulons en puissance un modèle de transistor GaN (Figure 23) qui prend en compte cet effet thermique (ce modèle est abordé dans le chapitre suivant), pour deux températures différentes : Tj=300°K et Tj=400°K.

Figure 23 : Comparaisons de simulations en puissance d'un transistor GaN pour deux températures de socles différentes (fo=8GHz)

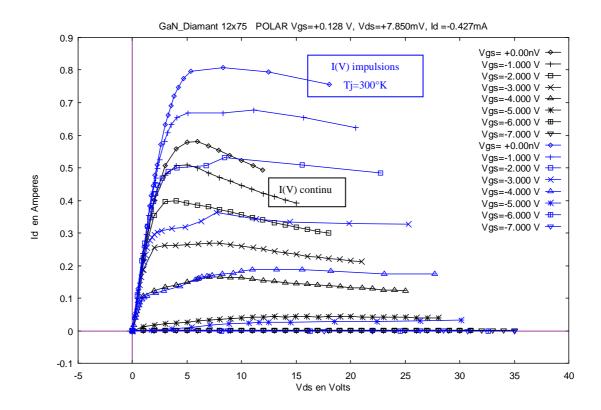

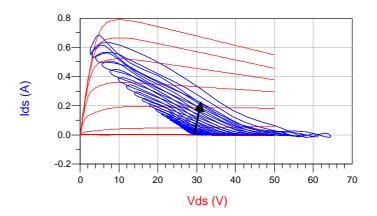

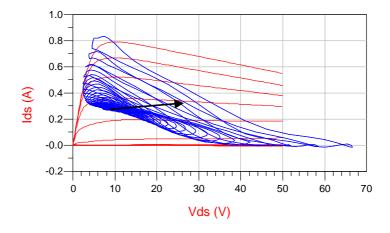

La Figure 24 illustre un exemple de l'effet d'auto-échauffement sur les caractéristiques I(V) d'un transistor HEMT GaN. Un réseau I(V) quasi-isotherme (Tj=300°K) mesuré en impulsions est comparé aux mesures en continu du même transistor (les méthodes de mesure seront abordées dans le chapitre II).

On peut observer une forte décroissance du courant de drain lorsque la tension Vds augmente. Ceci est lié à une décroissance de la mobilité des électrons lorsque la température augmente.

Figure 24 : Exemple d'auto-échauffement d'un transistor GaN

### III.2. Les phénomènes de pièges dans les transistors HEMTs GaN.

### III.2.1.Notion de piège

Le Nitrure de Gallium est un matériau semi-conducteur qui est mal contrôlé du point de vue des défauts qu'ils soient structuraux ou qu'ils soient ponctuels (impuretés, défauts intrinsèques). Ces impuretés génèrent des états énergétiques qui peuvent être occupés par des porteurs dans la bande interdite du matériau. Ces porteurs sont alors retenus pendant un temps T dans ces niveaux d'énergie et ne peuvent pas participer à la conduction, d'où le nom de pièges. Ces niveaux énergétiques constituent donc des pièges pour les matériaux semi-conducteurs.

Les phénomènes de pièges, résultant de l'existence d'impuretés ou de défauts dans le réseau cristallin altèrent considérablement le comportement électrique du transistor aux fréquences micro-ondes.

Plus le gap du semi-conducteur est grand et plus il offre la possibilité à des pièges de se former sur des niveaux d'énergie compris dans la bande interdite. Ces pièges ont la faculté de capturer ou d'émettre un électron ou un trou avec des constantes de temps diverses. Ces effets de pièges ont donc des conséquences sur le courant de drain, provoquant des effets transitoires de ce dernier [42].

La constante de temps de capture de pièges a une durée de l'ordre de la microseconde alors que celle d'émission des pièges a une durée d'environ 1000 fois supérieure à la capture, c'est à dire de l'ordre de la milliseconde. Ces constantes de temps correspondent à des phénomènes basses fréquences.

On distingue deux phénomènes de pièges prépondérants observés sur le courant de sortie du composant : le self-backgating et le gate-lag.

La méthode de mesure en régime I(V) pulsé permet de mettre en évidence ces phénomènes de piéges. En effet, c'est le point de polarisation de repos qui fixe, d'une part, l'état thermique et, d'autre part, l'état des pièges pour toute la mesure des caractéristiques I(V). En conséquence, si l'on mesure des caractéristiques I(V) à différents points de repos en conservant une puissance dissipée nulle (pour éviter l'échauffement du composant), la dispersion entre les mesures reflètera les effets de piège.

### III.2.2.Self-backgating

Ce phénomène est en relation avec la dispersion due aux pièges du substrat. Cet effet est en rapport avec le champ électrique généré par la tension drain-source [43], [44]. La présence de pièges dans le substrat semi-isolant, engendre des états transitoires du courant de sortie Ids vis à vis des variations de la tension Vds. En l'absence de variations des tensions de commande, le nombre de pièges ionisés reste constant. Le nombre d'atomes qui capturent un électron venant du canal est égal au nombre d'atomes libérant un électron.

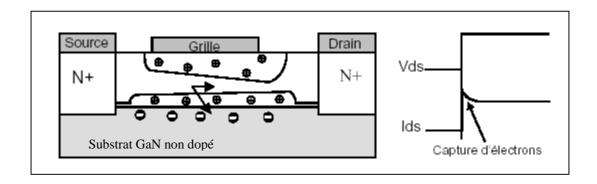

Lorsque la tension Vds augmente brusquement (Figure 25), un grand nombre d'électrons est injecté dans le substrat et est capturé par les pièges. La charge globale du substrat devient plus négative. Une charge d'espace positive se crée alors, dans le canal à l'interface canal - substrat. La section du canal diminue lentement ainsi que le courant Ids jusqu'à l'équilibre.

Figure 25 : Influence de la capture des électrons par des pièges de substrat

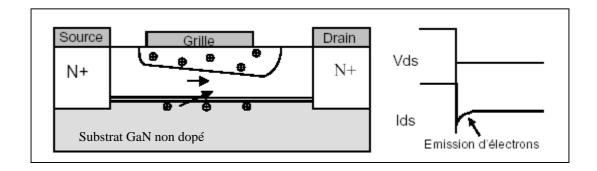

Lorsque la tension Vds diminue brusquement (Figure 26), les pièges émettent un grand nombre d'électrons dans le canal. En conséquence, la charge d'espace à l'interface canal – substrat, diminue lentement ; ce qui augmente l'épaisseur du canal. Le courant Ids augmente au rythme du processus d'émission des charges dans le canal jusqu'à atteindre son état permanent.

Figure 26 : Influence de l'émission d'électrons par des pièges de substrat

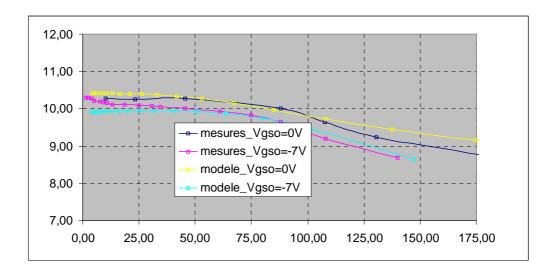

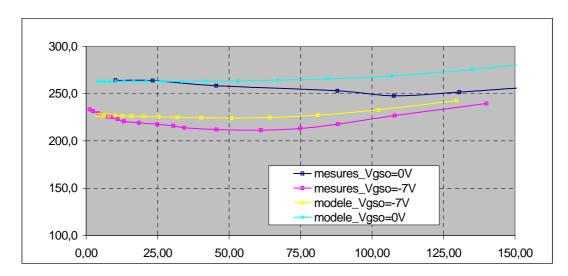

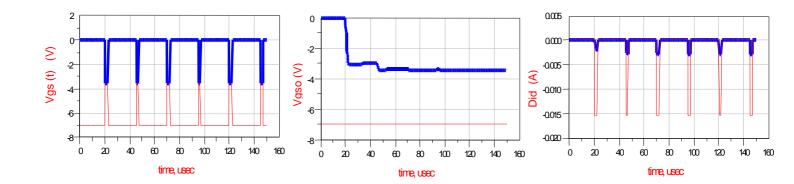

Afin de mettre en évidence ce phénomène, on compare les caractéristiques I(V) du composant mesurées en impulsion pour deux points de polarisation de repos différents qui ne présentent pas de puissance dissipée [45]. Cela consiste à appliquer des impulsions de polarisation de courte durée, dans notre cas 300ns avec une période de récurrence de 6µs.

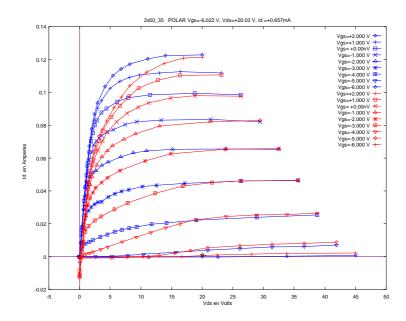

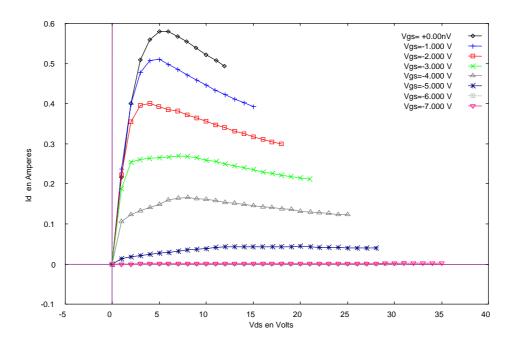

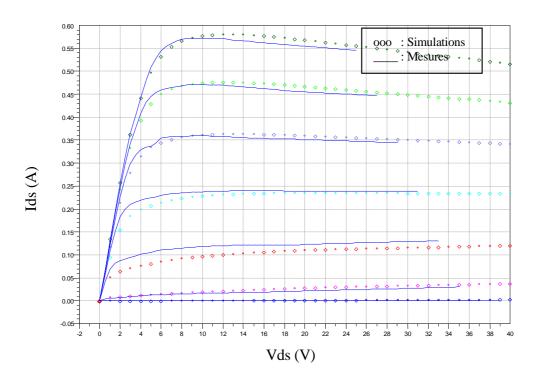

Tout d'abord, nous réalisons une première série de mesures pour lesquelles le transistor est polarisé de la manière suivante :  $V_{gs0} = V_p = -7V$  et  $V_{ds0}$ =0V. Ensuite, nous polarisons ce même transistor toujours avec la même tension de grille de repos, mais  $V_{ds0}$ =30V (Figure 27).

Figure 27 : Exemple de comparaison des caractéristiques I(V) obtenues sur un transistor GaN pour des polarisations (Vgs, Vds) de (-7V; 0V) et (-7V; 30V)

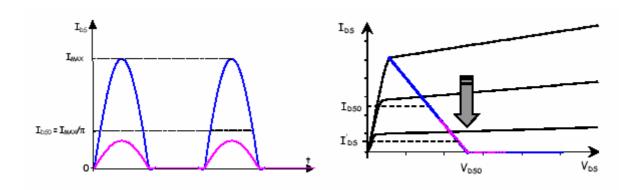

### III.2.3.Gate-lag

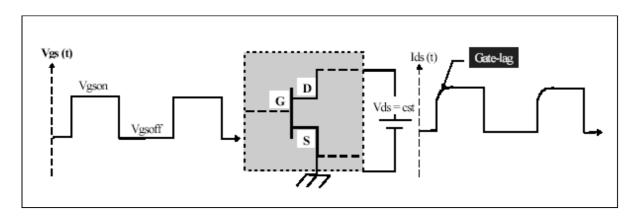

Ce phénomène [46], [47] (Figure 28) induit des effets transitoires lents du courant de sortie même lorsque la tension de commande varie brutalement, entraînant un retard du signal. Cet effet est principalement du à des piéges de surface et est en relation avec la tension grillesource de polarisation du composant. Un autre phénomène agit sur le gate-lag : l'ionisation par impact. Cependant les mécanismes physiques détaillés liés aux pièges de surface ne sont pas totalement identifiés.

Figure 28 : Mise en évidence du phénomène de « gate-lag »

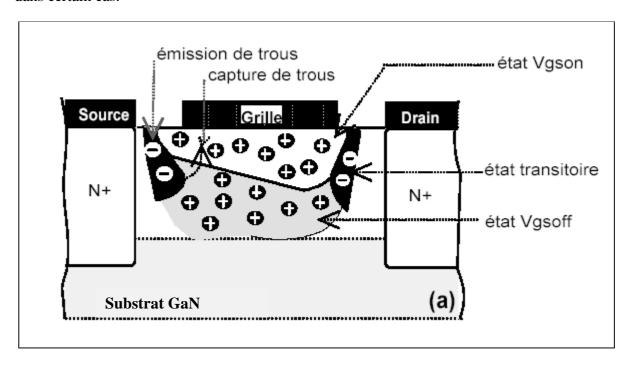

Lorsque Vgs=Vgsoff (pincement), le canal est entièrement déplété de la source vers le drain. Lorsque Vgs passe de Vgsoff à Vgson, le courant de drain reste faible jusqu'au commencement d'émission des électrons. L'augmentation du courant de sortie s'effectue d'une manière transitoire au rythme de vidage des pièges (Figure 29). Lorsque le processus de capture est terminé, le courant Ids atteint son état permanent après quelques millisecondes dans certain cas.

Figure 29 : Description physique du processus d'émission et de capture des charges à partir des pièges de surface

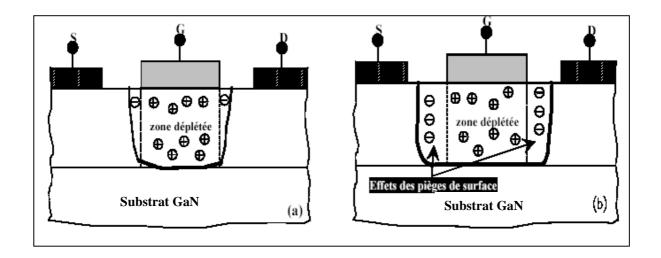

De plus, des travaux [48] ont montré que plus le transistor était pincé ( | Vgs | grand), plus les transitoires du courant de sortie dus au « gate lag » sont importants. Lorsque Vgsoff correspond au début du pincement du canal, celui-ci est essentiellement fermé sous toute la longueur de la grille (Figure 30-a), ainsi les effets de pièges de surface peuvent être négligeables. En revanche, lorsque Vgsoff atteint une valeur pour laquelle le pincement est profond, le canal est entièrement déplété de la source vers le drain (Figure 30-b). Dans ce cas, le courant Ids présente un comportement transitoire plus prononcé avant d'atteindre son état permanent.

Figure 30 : Effets d'un pincement léger (a) et profond (b) sur la zone désertée

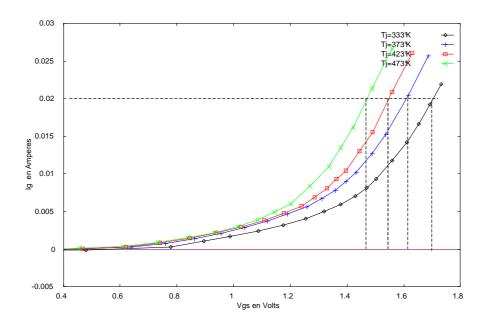

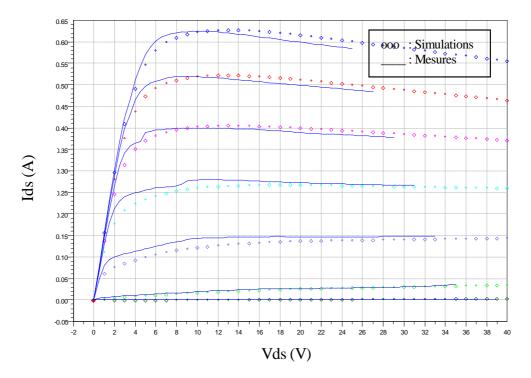

Afin de mettre en évidence ce phénomène, de la même manière que précédemment, on compare les caractéristiques I(V) du composant mesurées en impulsion pour deux points de polarisation de repos différents qui ne présentent pas de puissance dissipée [45].

Tout d'abord, nous réalisons une première série de mesures pour lesquelles le transistor est polarisé de la manière suivante :  $V_{gs0}=V_{ds0}=0V$ . Ensuite, nous polarisons ce même transistor avec  $V_{ds0}=0V$ , mais  $V_{gs0}=V_p=-7V$  (Figure 31).

Figure 31 : Exemple de comparaison des caractéristiques I(V) obtenues sur un transistor GaN pour des polarisations de (Vgs, Vds) de (0V ; 0V) et (-7V ; 0V)

Les réseaux I(V) précédents montrent les effets statiques des pièges. Cependant, pour des applications avec des signaux modulés en amplitude, il est important de prendre en compte les effets de pièges dynamiques. Typiquement, il existe deux constantes de temps :

- Les effets de capture des pièges qui sont de l'ordre de la micro-seconde.

- Les effets de libération de pièges qui sont de l'ordre de la milli-seconde.

Pour pouvoir réaliser une conception à partir de ces composants, il est donc nécessaire d'avoir un modèle électrique traduisant les effets thermiques et les effets de pièges du composant. Cette modélisation électrique est abordée dans le chapitre II.

# **CONCLUSION:**

Dans ce chapitre, les principaux critères technologiques (physiques et électriques) des différents transistors de puissance ont été présentés. Nous avons pu démontrer tout l'intérêt que présente le transistor HEMT en Nitrure de Gallium pour des applications d'amplification de puissance à haute fréquence.

Ce semi-conducteur apparaît dores et déjà comme un composant prometteur dans un avenir proche. L'état de l'art présentant de nombreuses publications sur la réalisation de transistor GaN atteste de l'intérêt des universitaires et des industriels pour ce composant.

Cependant, la réalisation du transistor qui est issu d'une technologie récente n'est pas encore totalement maîtrisée. Ils possèdent donc encore quelques défauts qui limitent leurs performances.

L'objectif final de la thèse est la conception d'un amplificateur de puissance de type Doherty. Etant donnée, l'importance des phénomènes thermiques et des effets de piège dans ce type de transistor en Nitrure de Gallium, nous avons développé un modèle électrique prenant en compte ces deux phénomènes. Ce modèle contribuera fortement à la méthodologie de conception de cet amplificateur. Cette modélisation particulière est donc le sujet du deuxième chapitre.

### **BIBLIOGRAPHIE**

### [1] S.I. LONG

"Microwave HBT. Principles and models",

IEEE Transactions on Microwave Theory and techniques Vol. 37, n°9, Sept 1989, pp. 1286-1301.

### F. ALI. A. GUPTA [2]

"HEMTs & HBTs".

Artech House, p. 191, 1991.

### [3] W. SHOCKLEY

"A unipolar field effect transistor",

Proc. of the IRE, vol. 40, pp. 1365, 1952.

### [4] J. M. COLLANTES, J. J. RAOUX ET AL.

« A new large-signal model based on pulse measurements techniques for RF power MOSFET » IEEE -MTT-s International Microwave Symposium, Orlando, 15-19 mai 1995

### S. WU, B. RAZAVI [5]

« A 900 MHz / 1.8 GHz CMOS receiver for dual-band applications »

IEEE journal of Solid State Circuits, vol. 33, n°15, pp 2178-2185, dec.1998

### [6] T.MANKU

« Microwave CMOS-Device physics and design »

IEEE journal of Solid State Circuits, vol. 34, n°3, pp 277-285, mars 1999

### [7] J. OLSSON, N. RORSMAN ET L. VESTLING ET AL

"1W/mm Power Density at 3.2GHz for a Dual-Layer RESURF LDMOS Transistor",

IEEE Electron Device Letters Vol 43, No 4, Avril 2002.

### BRECH, H.; BURGER, W.; DRAGON, C.; PRYOR, B [8]

"Voltage optimization for state of the art RF-LDMOS for 2.1 GHz W-CDMA cellular infrastructure applications",

Microwave Symposium Digest, 2003 IEEE MTT-S International, Volume: 1, 8-13 June 2003 Page(s): 209 -212 vol.1

### [9] K. MATSUNAGA, K. ISHIKURA, I. TAKENAKA AND AL.

A Low-Distortion 230W GaAs Power FPHFET Operated at 22V for Cellular Base Station", 2000 IEDM Technical Digest, pp. 393-396.

### N. SAKURA, K. MATSUNAGA, K. ISHIKURA AND AL.

"100W L-Band GaAs Power FP-HFET Operated at 30V", 2000 IEEE MTT-S Digest, pp. 1715-1718.

### [11] K.INOUE ET.AL

"A High Gain L-band GaAs FET Technology for 28V operation" IMS 2004

### [12] M. NAGAHARA, K. INOUE, S. SANO, H. TAKAHASHI, AND S. TAKASE

"A 28V 250W GaAs Power FET with High Gain of 15.5dB for W-CDMA Base Stations" IEEE MTT-S Digest, pp.1359-1362, 2004

### B. M. GREEN, E. LAN, P. LI AND AL

"A High Power Density 26 V GaAs pHEMT Technology"

IEEE MTT-S Digest, pp.817-820, 2004

### J. W. PALMOUR, J. A. EDMOND, H. S. KONG AND C. H. CARTER

"Silicon Carbide power devices for aerospace applications,"

in Proc. 28 th Intersociety Energy Conversion conf. Amer. Chem. Soc., pp 1249-1254, 1993.

### C. E. WEITZEL, J. W. PALMOUR, C. H. CARTER AND K. J. NORDQUIST

"4H-SiC MESFET with 2.8 w/mm power density at 1.8 GHz,"

IEEE Electron Device Letters, vol. 15, n°10, pp. 406-408, October 1994

### [16] H. GEORGE HENRY, GODFREY AUGUSTINE AND AL

"S-Band Operation of SiC Power MESFET With 20 W (4.4 W/mm) Output Power and 60% PAE" IEEE Trans. on Electron Devices, Vol. 51, No. 6, Juin 2004

### [17] S. DE MEYER

"Etude d'une nouvelle filière de composants HEMTs sur technologie nitrure de gallium. Conception d'une architecture flip-chip d'amplificateur distribué de puissance à très large bande" thèse de doctorat soutenue le 12 septembre 2005, Université de Limoges.

### [18] S.M. SZE

"Physics of Semiconductor Devices" 2<sup>nd</sup> Edition, 1981, ISBN O-471-O9837-X

### [19] S. T. SHEPPARD, K. DOVERSPIKE, W. L. PRIBBLE, AND AL.

« High-power microwave AlGaN/GaN HEMT.s on semi-insulating silicon carbide substrates » IEEE Electron Device Lett., vol. 20, pp. 161-163, Apr. 1999

### [20] C. CHARBONNIAUD, T. GASSELING, S. DE MEYER, AND AL.

"Power Performance Evaluation of AlGaN/GaN HEMTs through Load Pull and Pulsed I-V Measurements",

GAAS 2004, 11-12 Oct, 2004 Amsterdam

### [21] A. MINKO, V. HOËL, E. MORVAN, B. GRIMBERT, AND AL.

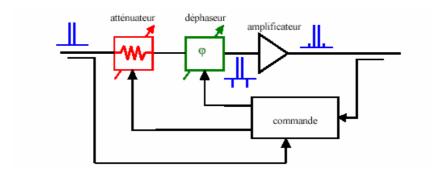

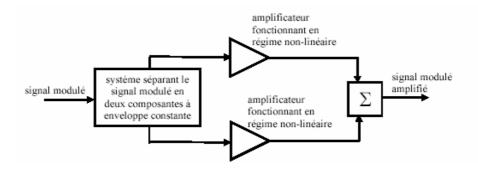

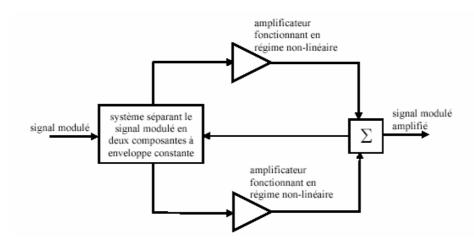

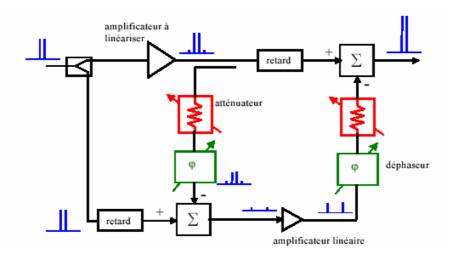

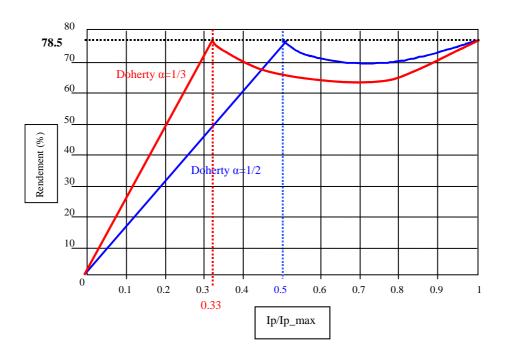

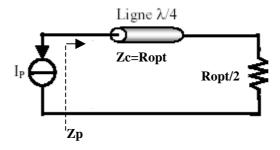

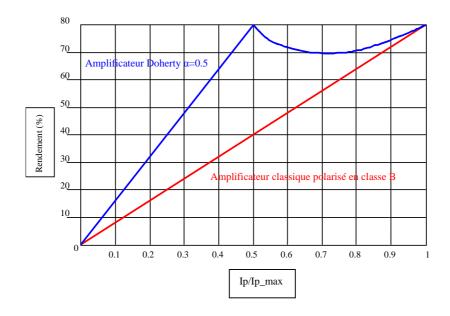

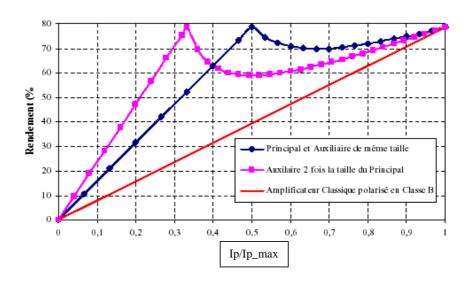

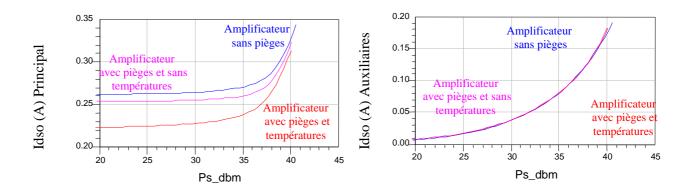

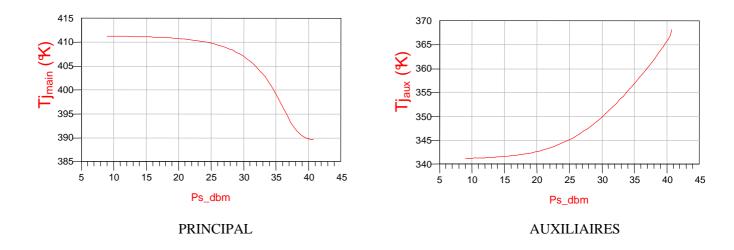

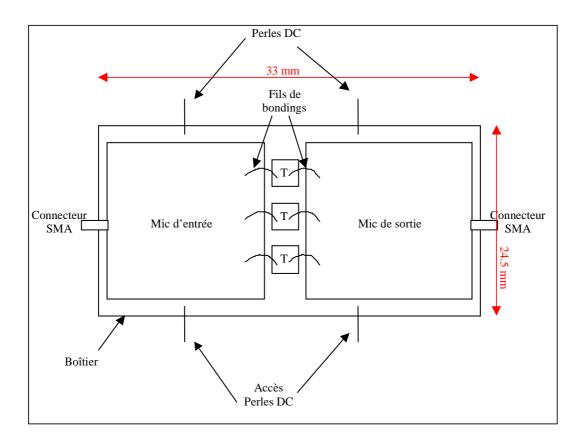

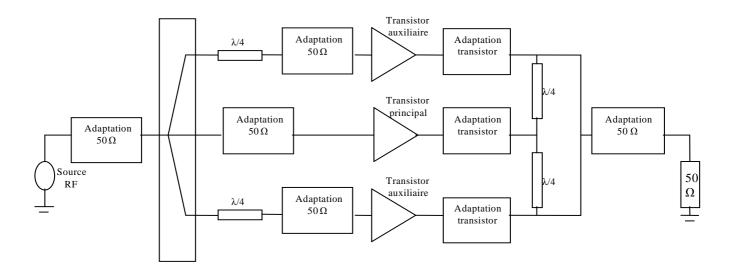

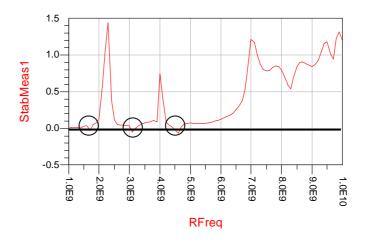

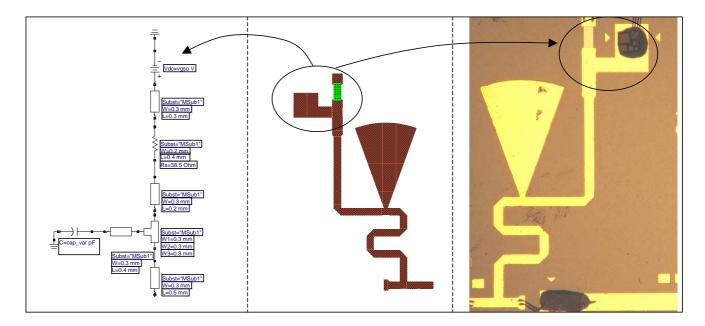

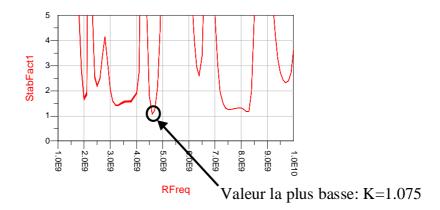

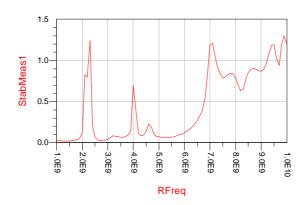

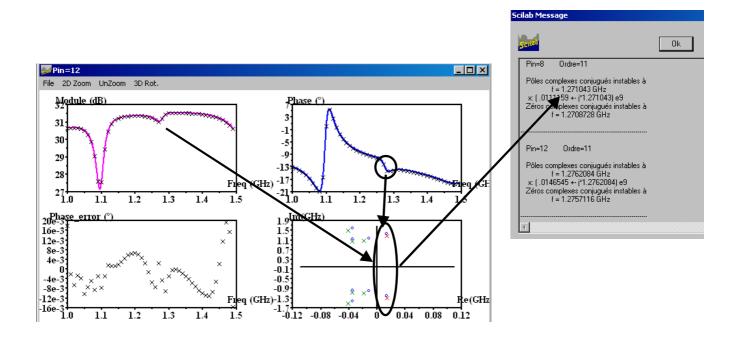

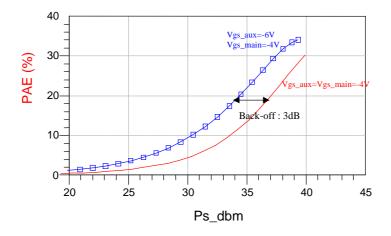

"AlGaN-GaN HEMTs on Si With Power Density Performance of 1.9 W/mm at 10 GHz", IEEE Electon Device Letters, Vol. 25, No. 7, pp. 453–455, Juillet 2004