#### UNIVERSITE DE LIMOGES

# ECOLE DOCTORALE SCIENCES - TECHNOLOGIE - SANTE FACULTE DES SCIENCES ET TECHNIQUES

XLIM – DÉPARTEMENT C<sup>2</sup>S<sup>2</sup>

Thèse n°14-2006

#### **Thèse**

pour obtenir le grade de

## DOCTEUR DE L'UNIVERSITE DE LIMOGES

## Discipline : Electronique des Hautes Fréquences et Optoélectronique

Spécialité : "Communications Optiques et Microondes"

Présentée et soutenue par

#### David EYLLIER

Le 5 mai 2006

## Outils de Synthèse Originaux pour la Conception de Dispositifs Actifs Microonde Intégrés

## Application au Filtrage et à l'Amplification Faible Bruit

Thèse dirigée par Laurent BILLONNET et Bernard JARRY

#### Jury:

| Michel CAMPOVECCHIO     | Professeur à l'Université de Limoges               | Président   |

|-------------------------|----------------------------------------------------|-------------|

| Gérard TANNE            | Maître de Conférences HDR à l'ENST Bretagne, Brest | Rapporteur  |

| Eric BERGEAULT          | Professeur à l'ENST Paris                          | Rapporteur  |

| Christophe LAPORTE      | Ingénieur au CNES, Toulouse                        | Examinateur |

| Jan Geralt BIJ DE VAATE | Scientific Project Manager, Astron R&D, Pays-Bas   | Examinateur |

| Laurent BILLONNET       | Professeur à l'Université de Limoges               | Examinateur |

| Bernard JARRY           | Professeur à l'Université de Limoges               | Invité      |

| Serge VERDEYME          | Professeur à l'Université de Limoges               | Invité      |

| Raymond QUERE           | Professeur à l'Université de Limoges               | Invité      |

|                         |                                                    |             |

#### REMERCIEMENTS

Ce travail a été effectué pour sa majeure partie à l'Institut de Recherche en Communications Optiques et Microondes, au sein de l'équipe « Circuits et Dispositifs Microondes » du Professeurs Serge VERDEYME que je remercie pour m'avoir accueilli.

La rédaction de ce manuscrit s'est achevée après l'avènement du laboratoire XLIM, époque à laquelle j'ai été rattaché au département C<sup>2</sup>S<sup>2</sup> dirigée par le Professeur Raymond QUERE que je tiens également à remercier.

Je tiens à remercier le Professeur Michel CAMPOVECCHIO qui a eu la gentillesse d'accepter de présider le jury de cette thèse.

J'exprime également toute ma gratitude à Monsieur Gérard TANNE, Maître de Conférences HDR à l'Ecole Nationale Supérieure de Télécommunication Bretagne de Brest, ainsi qu'à Monsieur le Professeur Eric BERGEAULT de l'Ecole Nationale Supérieure de Télécommunication de Paris qui ont bien voulu assurer la fonction de rapporteur.

Je témoigne ma reconnaissance à Messieurs Christophe LAPORTE et Jan Geralt BIJ DE VAATE, respectivement Ingénieur au Centre National d'Etudes Spatiales à Toulouse et Responsable de projet de Astron R&D aux Pays-Bas, pour avoir accepté d'examiner ce mémoire et de participer à ce jury.

J'adresse plus particulièrement mes remerciements à Messieurs Laurent BILLONNET et Bernard JARRY, Professeurs à l'Université de Limoges, qui par leur expérience, leur gentillesse et la disponibilité dont ils ont fait preuve, m'ont permis de mener à bien ces travaux.

Je tiens à exprimer ma gratitude à Monsieur Hubert JALLAGEAS, Ingénieur d'Etudes au Laboratoire XLIM, pour sa compétence et sa disponibilité lors des phases expérimentales.

J'adresse également mes sincères remerciements à Mesdames Marie-Laure GUILLAT et Marie-Claude LEROUGE pour leur convivialité et leur efficacité dans la gestion des tâches administratives.

Ces travaux ont été effectués en collaboration avec l'équipe de recherche du Professeur Leonid BABAK de l'Université de Tomsk, en Sibérie, que je remercie ici pour son aide et pour nous nous avoir permis d'utiliser ses outils logiciels.

Je tiens à remercier plus particulièrement Monsieur Mikhail CHERKASHIN, Docteur à l'Université de Tomsk, pour les nombreux échanges que nous avons eu, sa sympathie, sa gentillesse et pour nos discussions qui m'ont permis d'approfondir mes connaissances (en anglais surtout).

A Stéphanie, Laurent, Jean-Pierre et Nicole merci pour votre amour.

## **SOMMAIRE**

| INTRODUCTION GENER | ALE3 |

|--------------------|------|

|--------------------|------|

### **CHAPITRE I**

Nouvelle approche de conception pour la compensation des pertes de circuits passifs

| I.   | Int         | RODUCTION                                                            | 9      |

|------|-------------|----------------------------------------------------------------------|--------|

| II.  | ETA         | AT DE L'ART                                                          | 10     |

| III. | Pri         | NCIPE DU GYRATEUR ET DU CONVERTISSEUR D'IMPEDANCE NEGATIVE           | 15     |

| II   | I.1         | Introduction                                                         | 15     |

| II   | I.2         | Principe du gyrateur                                                 | 15     |

| II   | I.3         | Principe du convertisseur d'impédance négative (CIN)                 | 17     |

| II   | I.4         | Calcul de l'impédance de charge d'un quadripôle en fonction de l'imp | edance |

|      |             | d'entrée désireé                                                     | 19     |

| II   | I.5         | Bilan                                                                | 20     |

| IV.  | Pri         | ESENTATION DU LOGICIEL LOCUS                                         | 20     |

| IX   | V.1         | introduction                                                         | 20     |

| IV   | <i>J</i> .2 | Locus : principe de fonctionnement                                   | 20     |

| IV   | V.3         | Exemple de conception                                                | 23     |

| IV   | <i>J</i> .4 | Bilan                                                                | 27     |

| v.   | UTI         | LISATION DE LOCUS POUR LA COMPENSATION DE CIRCUITS PASSIFS           | 27     |

| V    | .1          | Conception d'une résistance négative large bande                     | 27     |

|      | V.1.        |                                                                      |        |

| V.     | 1.2  | Détermination du réseau passif de charge du CIN                     | 29      |

|--------|------|---------------------------------------------------------------------|---------|

| V.1.3  |      | Optimisation du circuit en éléments réels résultats de simulation   |         |

| V.     | 1.4  | Stabilité électrique                                                | 34      |

| V.2    | Co   | nception d'une inductance active large bande                        | 37      |

| V.2    | 2.1  | Topologie retenue - Détermination du réseau passif de charge        | 37      |

| V.2    | 2.2  | Dessin de masque et optimisation du circuit en éléments réels résul | tats de |

|        |      | simulation                                                          | 41      |

| V.2    | 2.3  | Etude de sensibilité                                                | 43      |

| V.2    | 2.4  | Stabilité électrique                                                | 45      |

| V.3    | Etu  | de d'une capacité négative pure large bande                         | 46      |

| V.4    | Bil  | an                                                                  | 47      |

|        |      |                                                                     |         |

| VI. co | NCLU | USION                                                               | 48      |

### **CHAPITRE II**

## Conception de filtres actifs utilisant la notion de profil d'impédance active

| I.   | INT         | RODUCTION                                                            | 51    |

|------|-------------|----------------------------------------------------------------------|-------|

| II.  | Pri         | NCIPE DU PROFIL D'IMPEDANCE                                          | 51    |

| I    | <b>I</b> .1 | Définition du profil d'impédance active                              | 51    |

| Ι    | I.2         | Contrôle de la fréquence centrale                                    | 53    |

| I    | I.3         | Contrôle de la bande passante                                        | 55    |

| I    | I.4         | Démarche de conception                                               | 56    |

| III. | APP         | LICATION A LA CONCEPTION D'UN FILTRE ACTIF SELECTIF                  | 57    |

| I    | II.1        | Conception de la partie passive du filtre                            | 57    |

| I    | II.2        | Extraction de la partie active                                       | 58    |

| I    | II.3        | Conception de la partie active                                       | 60    |

| I    | II.4        | Réalisation du filtre actif                                          | 61    |

| I    | II.5        | Mesure du circuit                                                    | 64    |

| IV.  | Con         | CEPTION D'UN FILTRE ACTIF PSEUDO-MULTIPOLE                           | 67    |

| Γ    | V.1         | Conception du filtre passif initial                                  | 67    |

| Γ    | V.2         | Extraction du profil d'impédance                                     | 68    |

| Γ    | V.3         | Conception de la partie active                                       | 73    |

| Γ    | V.4         | Réalisation du filtre actif                                          | 77    |

|      | IV.4        | .1 Etude de la stabilité électrique                                  | 79    |

|      | IV.4        | .2 Etude de sensibilité                                              | 82    |

| v.   | ETU         | DE D'UN PROFIL D'IMPEDANCE ACTIVE DESTINE A LA SYNTHESE D'UN FILTRE  | ••••• |

|      | MUL         | TINORME                                                              | 85    |

| V    | 7.1         | Définition d'un filtre multinorme                                    | 85    |

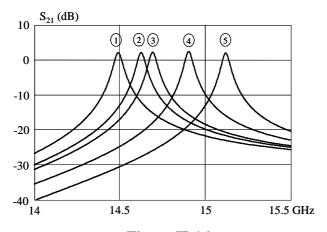

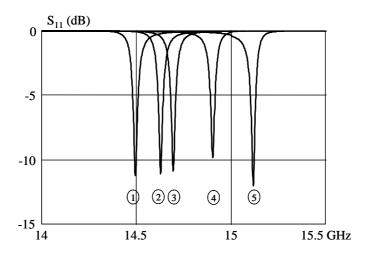

| V    | 7.2         | Comparaison des résultats de simulation du profil d'impédance active | 86    |

| VI.  | Con         | ICLUSION                                                             | 90    |

### **CHAPITRE III**

## Conception d'amplificateurs faible bruit Utilisation des logiciels Amp, Locus et Region

| I.   | INTE  | RODUCTION95                                                                    |

|------|-------|--------------------------------------------------------------------------------|

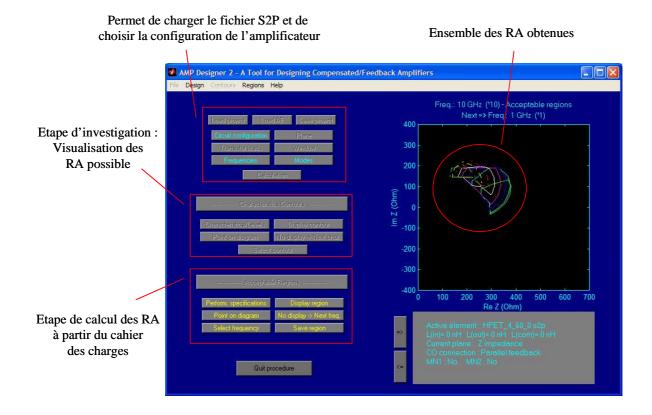

| II.  | Pres  | SENTATION D'UNE NOUVELLE METHODE DE CONCEPTION D'AMPLIFICATEUR 96              |

|      | .1    | Introduction96                                                                 |

|      |       | Amp: principe de fonctionnement                                                |

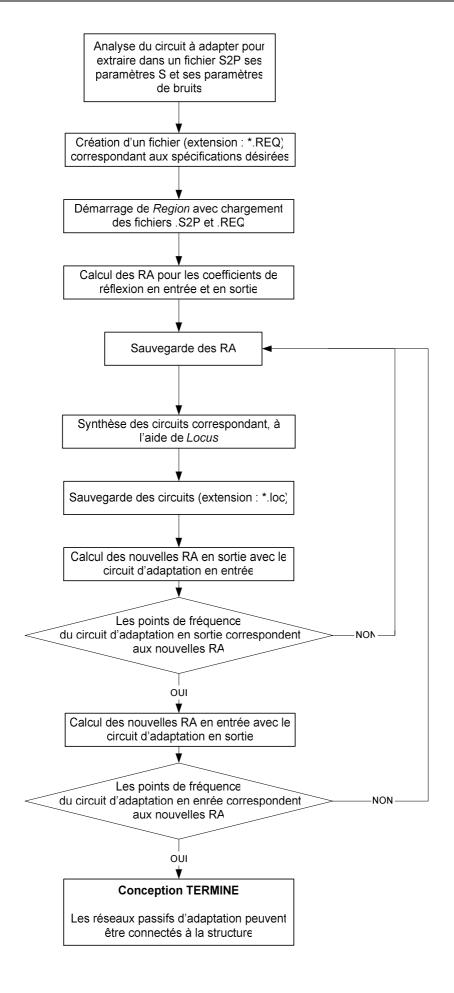

|      | .3    | Résumé de la méthode de synthèse                                               |

| III. | APP   | LICATION DE LA METHODE A LA CONCEPTION D'AMPLIFICATEURS FAIBLE                 |

|      | BRU   | rt104                                                                          |

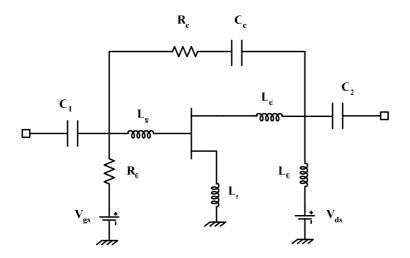

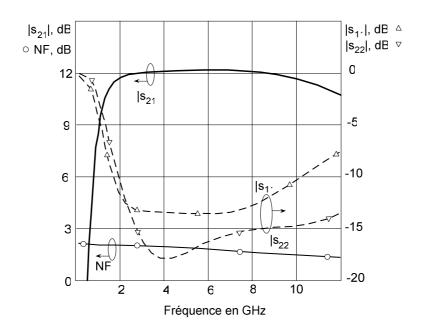

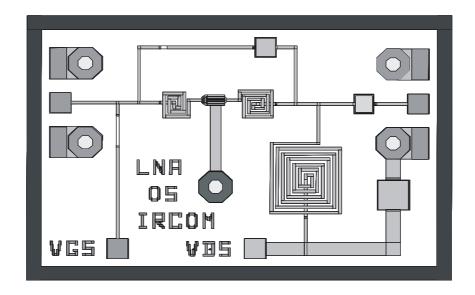

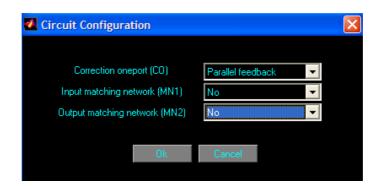

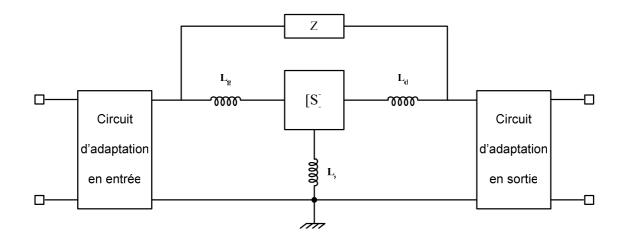

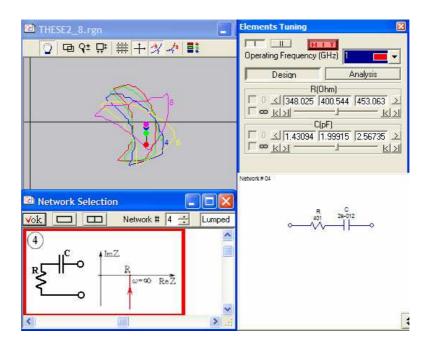

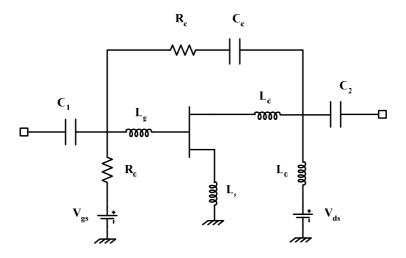

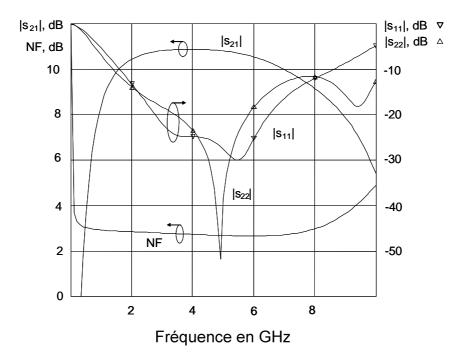

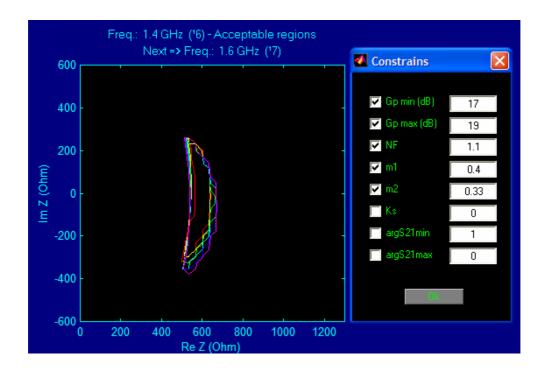

| II   | I.1   | Conception d'un LNA large bande entre 2 et 10 GHz                              |

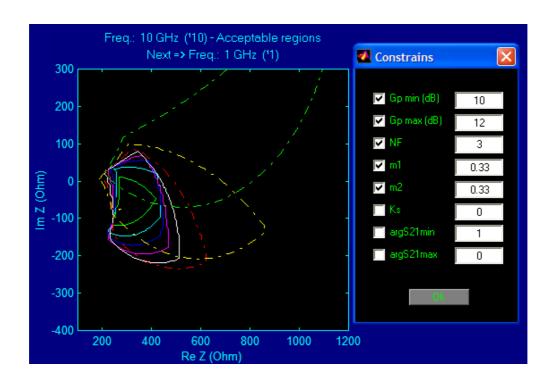

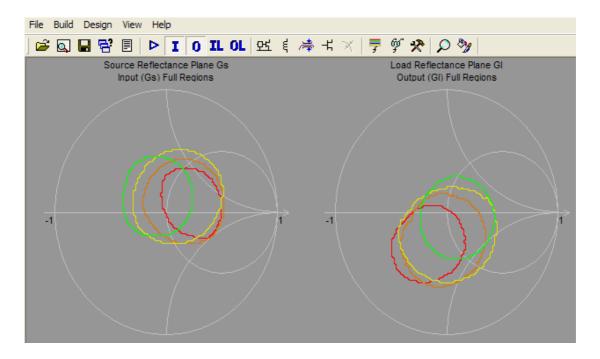

|      | III.1 | .1 Utilisation de Amp et Locus pour déterminer les régions acceptables et la   |

|      |       | topologie du LNA104                                                            |

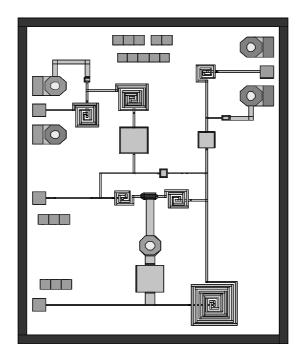

|      | III.1 | 2 Utilisation d'un logiciel circuit (Libra) pour finaliser la conception 107   |

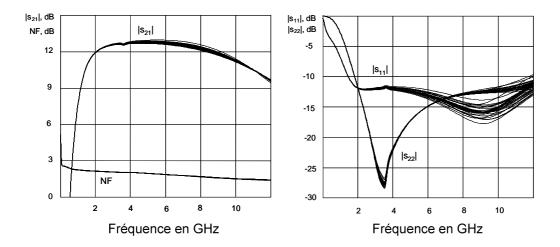

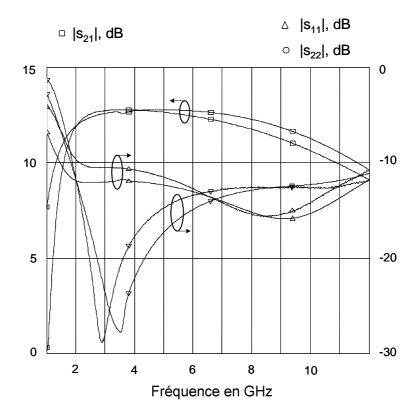

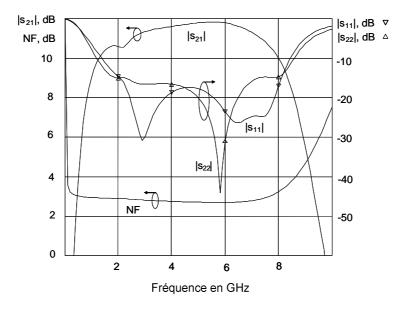

|      | III.1 | .3 Mesure du circuit                                                           |

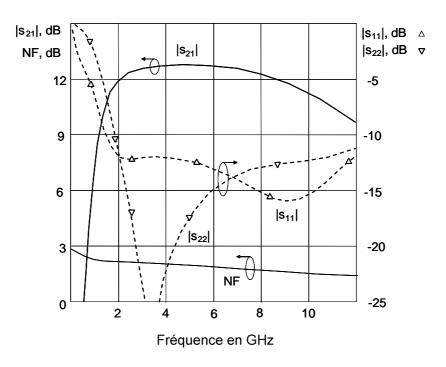

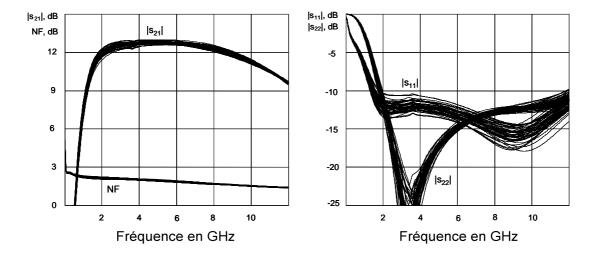

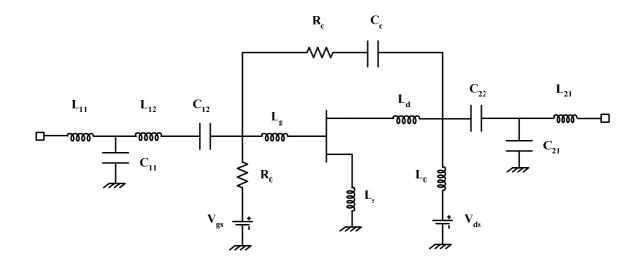

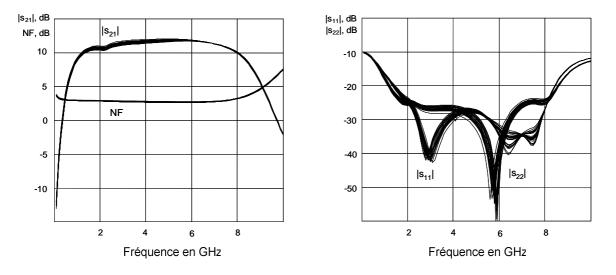

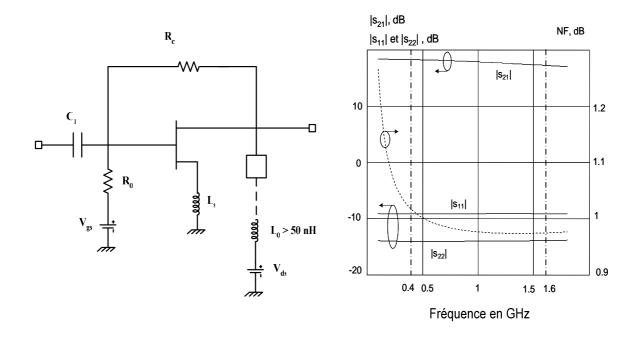

| II   | I.2   | Conception d'un LNA large bande entre 2 et 8 GHz adapté en entrée              |

|      |       | et en sortie                                                                   |

|      | III.2 | .1 Utilisation de Amp et Locus pour déterminer les régions acceptables et la   |

|      |       | topologie du LNA115                                                            |

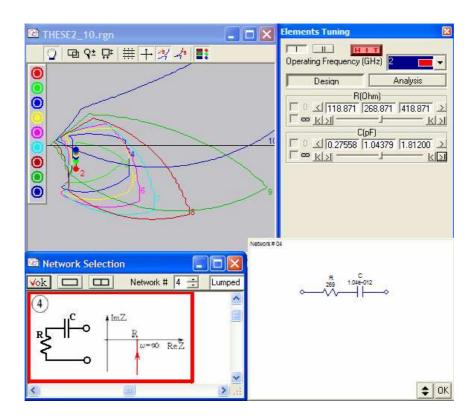

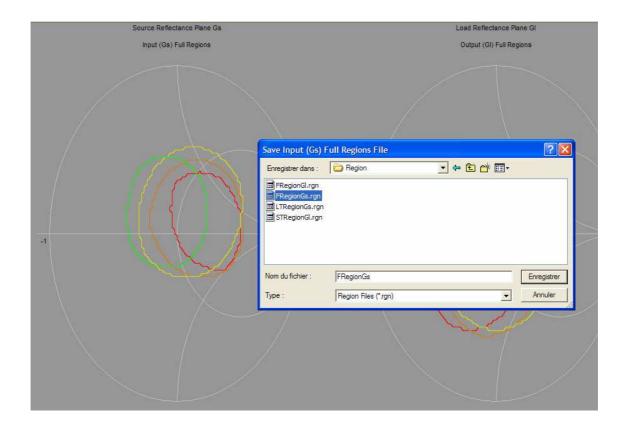

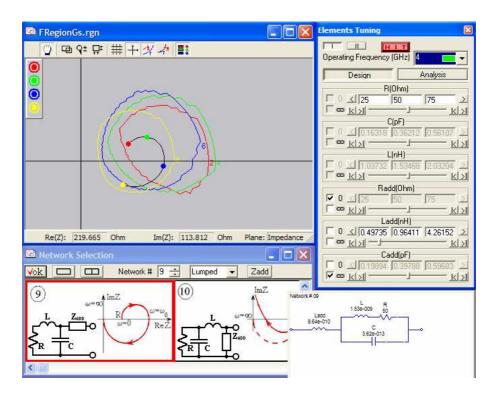

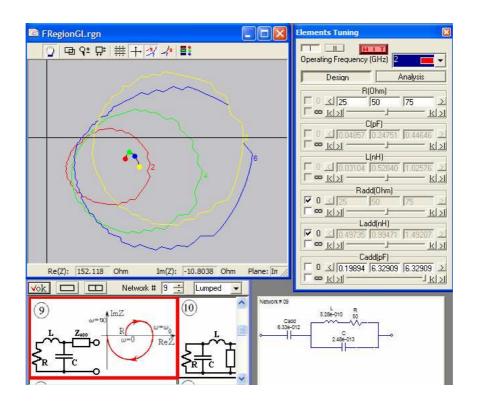

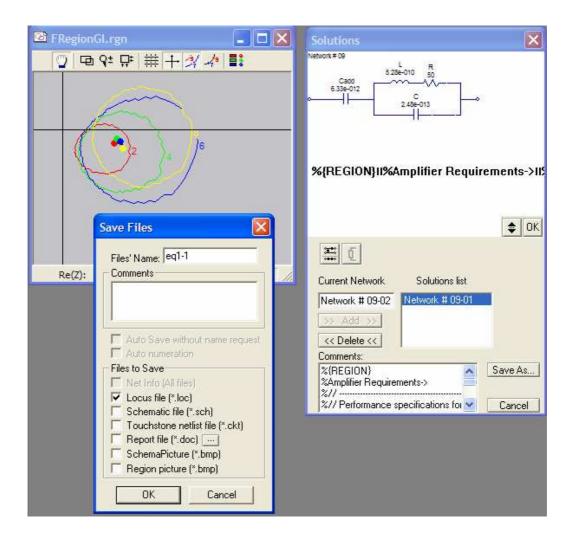

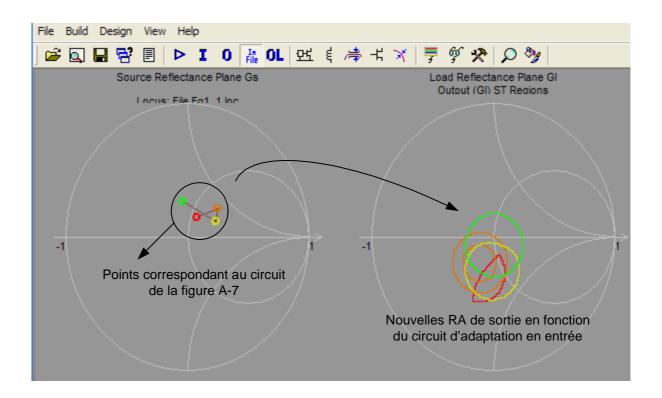

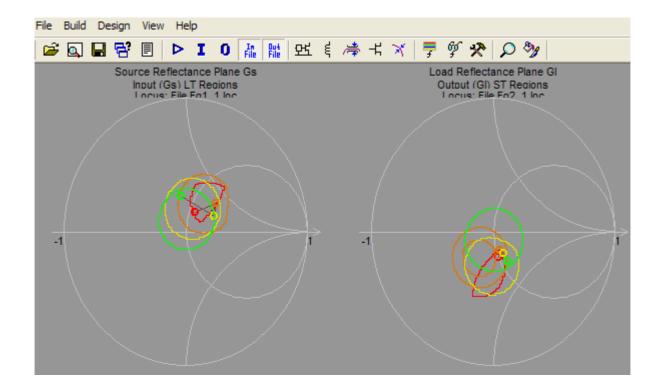

|      | III.2 | 2 Utilisation de Region et Locus pour construire les circuits d'adaptation 118 |

|      | III.2 | .3 Utilisation d'un logiciel circuit (Libra) pour finaliser la conception 119  |

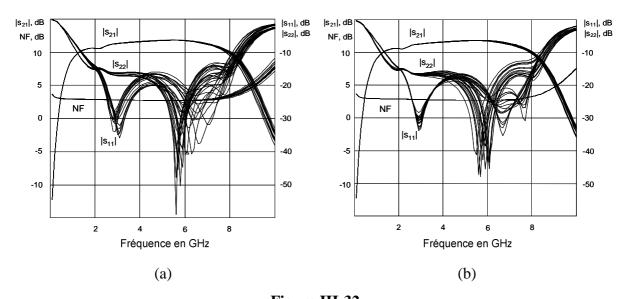

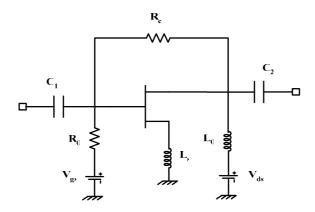

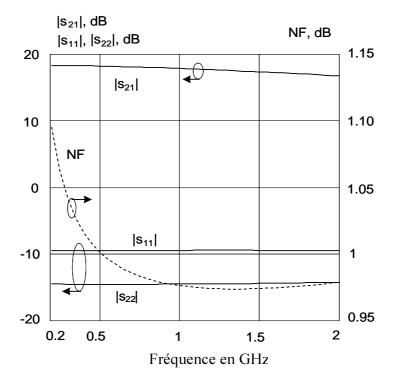

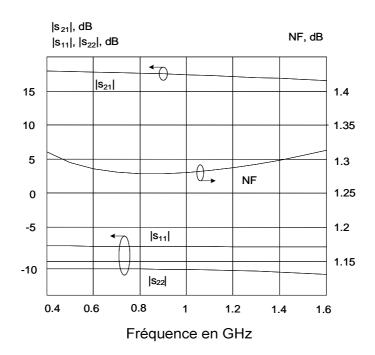

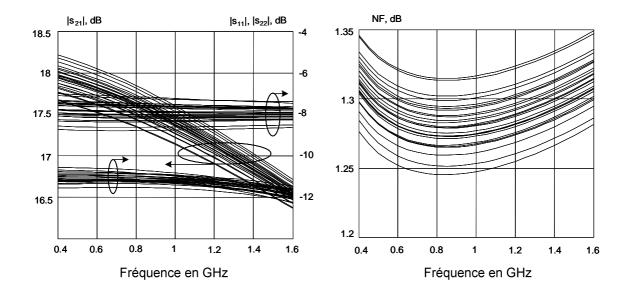

| II   | I.3   | Conception d'un LNA dans la bande [0,4 – 1,6] GHz                              |

|      | III.3 | .1 Utilisation de Amp et Locus pour déterminer les régions acceptables et la   |

|      |       | topologie du LNA126                                                            |

|      | III.3 | 2 Utilisation d'un logiciel circuit (Libra) pour finaliser la conception       |

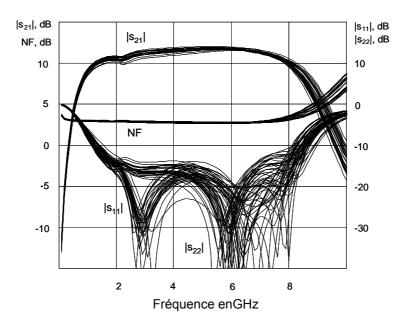

|      | III.3 | .3 Conception du LNA avec polarisation du drain au travers d'une charge        |

|      |       | active                                                                         |

| IV   | Con   | ICLUSION                                                                       |

| CONCLUSION GENERALE       | 141 |

|---------------------------|-----|

| ANNEXES                   | 145 |

| BIBLIOGRAPHIE             | 165 |

| BIBLIOGRAPHIE PERSONNELLE | 177 |

# INTRODUCTION GENERALE

#### INTRODUCTION GENERALE

Les progrès récents et considérables de la technologie micro-électronique ont largement fait évoluer les dispositifs hyperfréquence.

Depuis l'apparition des premiers radars et des liaisons hertziennes, les applications des systèmes microondes ne se restreignent plus maintenant au domaine militaire mais s'étendent de plus en plus aux secteurs civils.

En effet, les circuits intégrés monolithiques microondes (MMICs) ont acquis un rôle important dans les stratégies de développement depuis le début des années 80. Les MMICs sont désormais omniprésents dans les équipements actif hyperfréquences pour des applications grand public telles que les télécommunications par satellite, la téléphonie mobile [??], l'automobile avec le radar anticollision, l'Internet ou encore les systèmes de guidage par satellites de type GPS (Global Positionning System) ou prochainement de type GALILEO (système de localisation par satellites civil européen).

Ces nouvelles applications font appel à des dispositifs électroniques qui se doivent d'être de plus en plus performants sur bien des points :

- Sélection précise des bandes de fréquences allouées pour éviter d'éventuelles interférences entre les différentes applications,

- Réduction du poids et de l'encombrement des systèmes,

- Réduction des coûts de production,

- \$ Fonctionnement a des fréquences de plus en plus élevées.

L'amélioration des dispositifs électroniques passe par l'amélioration de chaque souscircuit assurant une fonction déterminée au sein du système. Deux d'entre elles, la fonction Introduction Générale 4

filtrage, et plus particulièrement le filtrage actif, ainsi que l'amplification faible bruit concernent directement les travaux présentés dans ce manuscrit.

Cependant, l'utilisation des dispositifs actifs dans la fonction de filtrage se sont accompagnés de nouveaux problèmes jusque là inconnus dans le cas de dispositifs microondes passifs. Parmi ceux-ci ont peut citer :

- ♦ la stabilité électrique,

- le comportement fort signal,

- \\$\\$\ les performances en bruit,

- 🖔 la consommation électrique des systèmes actifs.

Le concepteur doit donc faire appel à de nouvelle méthode afin d'améliorer en permanence ces dispositifs.

Les études présentées dans ce manuscrit s'inscrivent directement dans cette dernière approche. Notre objectif est d'utiliser de nouvelles méthodes de conception afin d'améliorer les performances des systèmes liés au filtrage actif tels que les résistances négatives, les inductances actives et les capacités négatives. Pour cela, nous utilisons une méthode appelée "méthode du profil d'impédance active".

Ce rapport est organisé en trois chapitres et s'articule de la manière suivante :

Dans le chapitre I, nous présentons un bref état de l'art sur l'évolution du filtrage actif microonde. Cette étude nous conduit vers l'analyse de dispositifs actifs tels que les gyrateurs et les convertisseurs d'impédances négatives.

La suite est consacrée à la synthèse d'une nouvelle méthode de conception faisant intervenir le calcul de l'impédance de charge d'un quadripôle en fonction de son impédance d'entrée et l'utilisation d'un logiciel (*Locus*) développé par Tomsk State University of Control System and Radioelectronics de l'Université de Tomsk en Sibérie. Cette première étude débouche alors par la conception de divers dispositifs et plus particulièrement une inductance active pure.

Introduction Générale 5

Dans le deuxième chapitre, nous présentons la conception de deux filtres actifs en technologie monolithique. Après une description de la "méthode de profil d'impédance active", nous appliquons ce principe à la conception d'un filtre actif passe bande sélectif ainsi qu'un filtre actif pseudo multipôle.

Les résultats de simulation de ces circuits s'accompagnent d'une série d'étude de sensibilité et de stabilité électrique. Nous comparons alors les résultats de mesures du filtre actif sélectif avec ceux obtenus en simulations afin de valider notre méthode de conception.

Enfin, nous comparons les résultats de simulation d'un circuit actif, obtenus avec le principe de profil d'impédance active, aux résultats présentés par F. Biron [40].

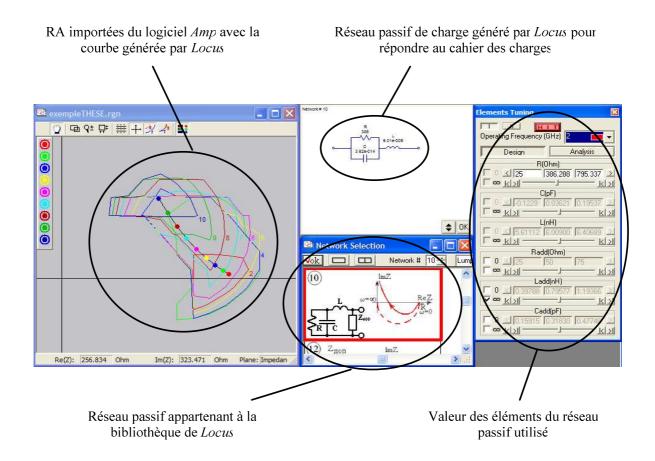

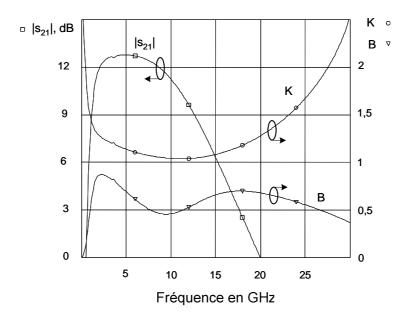

Le troisième chapitre porte sur l'étude d'une nouvelle méthode de conception d'amplificateur faible bruit. Cette conception, visuelle, est basée sur le tracé de courbes d'iso valeur correspondant aux différentes spécifications du circuit. Après avoir présenté le principe de cette méthode ainsi que le fonctionnement du logiciel *Amp*, nous appliquons cette étude à la conception de trois LNA.

Le premier est un LNA large bande entre 2 et 10 GHz dont la comparaison entre les résultats de simulation et les résultats de mesures nous permet de valider notre démarche. Le deuxième est un LNA large bande adapté en entrée et en sortie entre 2 et 8 GHz et fait intervenir un nouveau logiciel (*Region*) destiné à la conception de circuit d'adaptation. Enfin nous présentons les résultats de simulation d'un LNA dans la bande [0,4 – 1,6] GHz.

La conclusion générale présente les perspectives de ces nouvelles méthodes de conception.

## **CHAPITRE I**

Nouvelle approche de conception pour la compensation des pertes de circuits passifs

#### I. INTRODUCTION

L'utilisation d'éléments actifs dans des dispositifs microondes s'est révélée très prometteuse. Elle est particulièrement intéressante dans le cas des circuits monolithiques pour compenser les pertes d'une inductance spirale (résistance négative) ou pour réaliser directement une inductance idéale sans pertes (inductance active). On peut alors intégrer ces inductances actives au sein d'autres dispositifs monolithiques pour réaliser :

- des fonctions de filtrage très sélectives,

- des déphaseurs faibles pertes [1],

- des oscillateurs contrôlés en tension (OCT) [2]...[4]

L'objectif de ce chapitre est d'étudier et d'utiliser divers systèmes actifs tels que les gyrateurs et les convertisseurs d'impédances négatives pour concevoir des résistances négatives, capacités négatives et inductance actives.

Dans un premier temps, avant de réaliser cette étude, nous effectuons un état de l'art de manière à bien situer notre travail dans l'évolution actuelle des techniques de filtrage actif.

Nous nous attachons par la suite à donner un descriptif théorique des gyrateurs et des convertisseurs d'impédances négatives ainsi que d'une méthode développée par S.E. Sussman-Fort permettant de calculer l'impédance de charge d'un quadripôle pour réaliser ces fonctions.

Enfin, à partir de cette étude théorique, une prise en main détaillée du logiciel *Locus* nous permet de concevoir, avec l'aide de Libra, divers dispositifs, et plus particulièrement une inductance active pure.

Le but ici est de montrer, à l'aide de ces méthodes et nouveaux outils originaux, qu'il est possible de concevoir une multitude d'impédances destinées à des applications particulières de filtrage actif, et servant à compenser ou annuler les pertes d'insertions, à régler la largeur de la bande passante et/ou de la fréquence centrale des réponses correspondantes.

#### II. ETAT DE L'ART

La nécessité de passer des technologies "classiques" (du type guide d'onde) à des technologies planaires trouve son explication dans l'analyse des caractéristiques et des domaines d'applications des systèmes dits "volumiques" [5], [6] qui ne correspondent pas à l'évolution du marché vers les applications actuelles telles que la téléphonie mobile par exemple.

En effet, l'évolution des systèmes microondes vers des applications "grand public" a entraîné une augmentation conséquente de la complexité des systèmes et mis en évidence des contraintes incontournables telles que la réduction du poids et du volume des dispositifs ainsi que l'amélioration de leurs performances.

C'est pourquoi les concepteurs se sont tournés vers les technologies planaires puis vers des technologies monolithiques intégrées pour des applications analogiques microondes puis mixtes analogiques/numériques.

Cependant, comme tous les filtres passifs, les performances électriques des filtres correspondants sont limitées par leurs pertes d'insertion. Si on considère en plus la nécessité pour ces dispositifs d'être rendus accordables en fréquence, même les systèmes cryogéniques qui permettent une tenue en température des circuits [7], mais dont la mise en œuvre reste malgré tout encore encombrante et délicate, ne peuvent rentrer dans le cadre de ces différentes évolutions.

C'est donc vers le filtrage actif que le concepteur trouvera une grande partie des réponses à ces nouveaux problèmes.

En effet, l'introduction d'éléments actifs dans les filtres microondes, vise à atteindre les objectifs suivants :

- la compensation des pertes qui affectent les réponses des filtres,

- l'apport éventuel de gain dans les bandes de fréquence passantes,

- l'accordabilité et le réglage en fréquence des réponses par des moyens électriques,

- l'utilisation de nouvelles topologies de circuits pour le filtrage.

En contrepartie, l'utilisation de ces éléments introduit aussi de nouvelles contraintes que le concepteur devra donc prendre en compte, telles que la stabilité électrique, les performances de bruit, le comportement fort signal ainsi que la consommation électrique.

Même si, comme nous l'avons vu précédemment, l'amélioration des filtres passifs à l'aide de fonctions actives ne se limite pas uniquement à la compensation des pertes, cette dernière constitue un aspect important pour la réalisation de structures sélectives sans pertes et a été très développée par l'ensemble de la communauté scientifique.

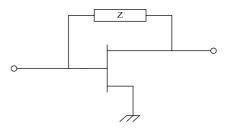

Sur ce thème, on peut voir, dans la littérature, que les circuits simulant une résistance négative sont répertoriées en deux grandes familles. La première utilise la rétroaction d'un transistor unique. La seconde repose sur le principe des convertisseurs d'impédances négatives que nous développerons plus en détail dans le paragraphe III.3.

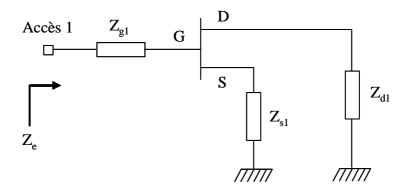

Ainsi, dans les études faites par Ph. Meunier [8], de même que dans [9] et [10], il apparaît que la rétroaction série d'un transistor monté en source commune est la structure la plus appropriée, par rapport à une rétroaction parallèle, pour la réalisation d'une résistance négative (figure I-1).

Figure I-1

#### Schéma général de la rétroaction série simulant une résistance négative

En effet, si on remplace le transistor de la figure I-1 par son schéma équivalent petit signal, on peut alors extraire l'expression de Ze l'impédance d'entrée du dispositif, montrant ainsi la possibilité de réaliser des résistances négatives.

Un solveur permet ensuite de déterminer les valeurs et la nature des impédances, devant être mise en série avec le transistor, afin d'obtenir une partie réelle de l'impédance d'entrée Ze négative.

Les publications [11] [12] [13] présentent aussi différentes conceptions de résistances négatives et tendent ainsi à montrer l'importance de tels systèmes.

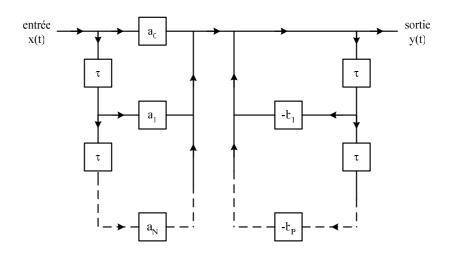

D'autres aspects du filtrage actif, tels que l'obtention de gain dans la bande passante et l'accordabilité en fréquence, ont été grandement développés ces dernières années. On peut citer parmi les différents dispositifs trouvés dans la littérature, la réalisation des filtres récursifs et transversaux [14], appartenant initialement à la catégorie des filtres numériques basses fréquences (figure I-2).

Figure I-2 Graphe de fluence général d'un filtre récursif et transversal

Ces filtres génèrent une fonction de transfert globale grâce à des recombinaisons constructives ou destructives des signaux, dues à un temps de retard unitaire  $\tau$ , dans les différentes branches du filtre où les signaux ne sont pas nécessairement filtrés mais plutôt pondérés par une fonction qui s'identifie aux fréquences microondes à un amplificateur.

Cette transposition des basses fréquences aux fréquences microondes permet ainsi des applications analogiques que ce soit pour la partie récursive [15] [16] [17], ou pour la partie transversale [18] [19] dans une approche parfois voisine des filtres "channélisés".

Les travaux développés dans [20] montrent l'obtention de gain dans la bande passante, obtenu grâce à une topologie de filtre récursif à deux pôles en anneaux (figure I-3)

Figure I-3

Structure et réponse d'une topologie récursive en anneaux

Dans cet exemple, le temps de parcours du signal dans un anneau correspond au temps de retard  $\tau$ . Les deux coupleurs en entrée et en sortie sont réalisés par deux paires de lignes couplées et le facteur de pondération est réalisé à l'aide de l'amplificateur unilatéral placé dans le premier anneau.

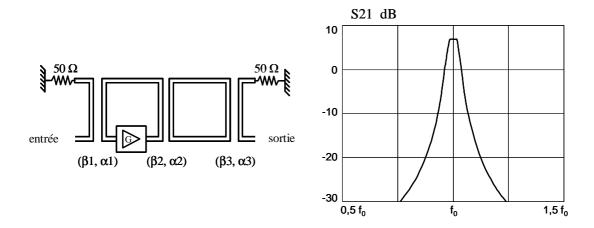

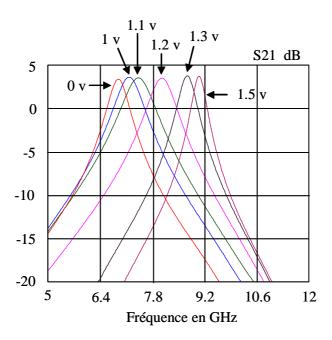

De plus, l'utilisation des filtres récursifs permet aussi, comme le montre l'exemple de la figure I-4, de régler la fréquence de résonance et ainsi d'obtenir des réponses de filtres accordables.

Figure I-4

Structure et réponse d'un filtre récursif avec un réglage de la fréquence centrale par diode varactor

Nous pouvons remarquer ici que, par plusieurs réglages, il est possible d'obtenir à la fois une accordabilité en fréquence et du gain à niveau constant dans les différentes bandes passantes.

En effet, ces résultats de simulation sont obtenus en modifiant la tension de polarisation de la diode varactor, mais aussi celles des différents transistors afin de maintenir un gain constant sur toute la plage d'accord. Il faut noter ici que la largeur de la bande passante n'est pas constante pour toutes les fréquences centrales obtenues.

Dans [21] et [22] des méthodes sont développées pour synthétiser des impédances quelconques à parties réelles négatives, mais dont les parties imaginaires peuvent être mises à profit pour une réduction de la taille du filtre passif initial.

De même, des études ont été menées sur des filtres accordables en fréquence ou commutables destinés à être utilisés pour des applications de télécommunications mobiles multinormes [23], [24] ; cependant le contrôle de la largeur de bande passante reste toujours un problème.

Ces réflexions vont nous amener à définir la notion de profil d'impédance.

#### III. PRINCIPE DU GYRATEUR ET DU CONVERTISSEUR D'IMPEDANCE NEGATIVE

#### III.1 INTRODUCTION

L'utilisation des gyrateurs (ou inverseurs d'impédance) et des "Convertisseurs d'Impédance Négative" (ou CIN), qui sont des fonctions électriques très utilisées initialement aux basses fréquences, répondent exactement aux attentes des concepteurs en matière de compensation de pertes ou de parties résistives en général. Leur rôle est initialement de "fabriquer" à partir d'une impédance dite "de charge", une autre impédance selon un objectif déterminé. Ainsi, le rôle d'un gyrateur est de présenter à son entrée, une impédance proportionnelle à l'inverse de son impédance de charge, alors que le CIN a pour rôle de présenter à son entrée une impédance proportionnelle à son impédance de charge mais de signe opposé.

Nous détaillons maintenant les principes des deux dernières méthodes citées.

#### III.2 PRINCIPE DU GYRATEUR

L'utilisation des gyrateurs débouche essentiellement, aux fréquences microondes, sur la conception d'inductances actives [25] [26]. En effet, l'utilisation des inductances spirales en technologie MMIC amène le concepteur à prendre en compte plusieurs problèmes comme leur grande taille ainsi que leur niveau de pertes.

Ces pertes sont fonction de la largeur et de la longueur du ruban constituant l'enroulement. Elles dépendent également de la fréquence de travail.

Dans le cas idéal, il est possible de synthétiser une inductance sans perte en chargeant le gyrateur par une capacité sans pertes.

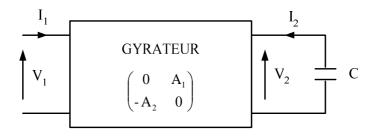

La matrice Y d'un gyrateur peut s'écrire de la manière suivante :

$$Y = \begin{bmatrix} 0 & A_1 \\ -A_2 & 0 \end{bmatrix}$$

où  $A_1$  et  $A_2$  sont réels de même signe.

Il est possible de concevoir une inductance active en chargeant un gyrateur par une capacité.

Soit le schéma suivant :

Figure I-5 Schéma de principe d'une inductance active obtenue à partir d'un gyrateur

On a alors:

$$\begin{split} I_1 &= A_1.V_2\\ I_2 &= -A_2.V_1\\ \text{et}: \qquad V_2 &= \frac{-1}{jC\omega} \cdot I_2\\ \text{d'où}: &-jC\omega V_2 = I_2 = -A_2 V_1\\ \text{soit}: &\quad V_2 &= \frac{A_2}{jC\omega} \cdot V_1 \end{split}$$

Finalement :

$$Z_e = \frac{V_1}{I_1} = \frac{jC\omega}{A_1.A_2}$$

(impédance d'entrée du dispositif)

L'impédance d'entrée du dispositif est alors homogène à une inductance de valeur  $C/A_1.A_2$ . Cette valeur peut être ajustable en chargeant le gyrateur sur une diode varactor, ou en faisant varier les coefficients  $A_1$  et  $A_2$ .

#### III.3 PRINCIPE DU CONVERTISSEUR D'IMPEDANCE NEGATIVE (CIN)

D'une manière générale, les filtres passifs ont souvent des performances limitées. Ces limitations sont principalement dues aux pertes introduites en transmission. Il est donc important de pouvoir diminuer ces pertes, voire de les annuler, par des circuits actifs tels que ceux du type résistances négatives par exemple [27], [28].

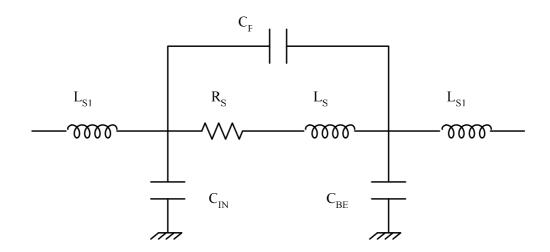

La figure I-6 présente le circuit électrique équivalent d'une inductance du procédé de fabrication monolithique ED02AH d'OMMIC [34] :

Figure I-6

Circuit électrique équivalent d'une inductance

du procédé de fabrication monolithique ED02AH d'OMMIC

où:

$$R_s = P \times (\alpha_{R_s} - \beta_{R_s} \times P)$$

avec:

$$\alpha_{R_s} = 0.268 + \frac{28.13}{W}$$

$$\beta_{R_s} = 0.00312 + \frac{0.583}{W}$$

et: P: longueur du ruban

W: largeur du ruban

Il apparaît que la résistance série  $R_s$  croît avec la longueur de ruban et qu'elle diminue lorsque la largeur du ruban augmente.

Pour réduire ces pertes, le concepteur a la possibilité de placer une résistance négative en série avec l'inductance afin d'obtenir des pertes nulles au moins dans la bande passante.

De tels dispositifs peuvent être réalisés à l'aide de convertisseurs d'impédance négative [29] dont l'impédance d'entrée est proportionnelle et de signe opposée à l'impédance de charge. Ces circuits sont maintenant très utilisés dans la conception de filtres actifs et peuvent aussi servir à la conception de capacités négatives [30].

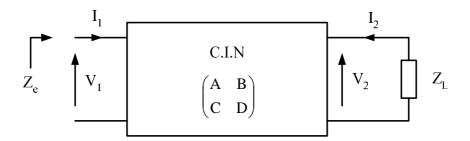

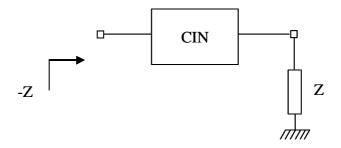

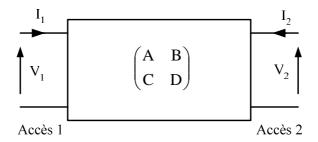

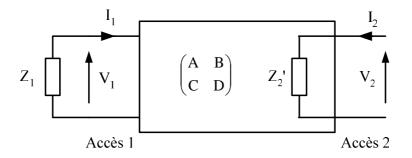

Un C.I.N est un quadripôle comme le montre la figure I-7

Figure I-7  $\begin{tabular}{ll} Schéma de principe d'un convertisseur d'impédance négative \\ chargé sur une impédance $Z_L$ \\ \end{tabular}$

où

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix}$$

est la matrice chaîne du C.I.N et où A, B, C, D sont de réels.

On peut écrire :

$$\left\{ \begin{array}{l} \mathbf{V}_1 = \mathbf{A}\mathbf{V}_2 - \mathbf{B}\,\mathbf{I}_2 \\ \mathbf{I}_1 = \mathbf{C}\,\mathbf{V}_2 - \mathbf{D}\,\mathbf{I}_2 \end{array} \right. \quad \text{et} \qquad \mathbf{V}_2 = -\mathbf{Z}_L \cdot \mathbf{I}_2$$

d'où:

$$\frac{V_1}{I_1} = \frac{A V_2 - B I_2}{C V_2 - D I_2}$$

L'impédance d'entrée  $Z_e$  du dispositif s'écrit alors :  $Z_e = \frac{A Z_L + B}{C Z_L + D}$

Dans le cas idéal, un convertisseur d'impédance négative est caractérisé par les relations B=C=0 et A/D=-1. L'impédance d'entrée  $Z_e$  est alors égale à l'opposé de l'impédance de charge  $Z_L$  et s'écrit alors :

$$Z_e = -k Z_L$$

où  $k = \frac{A}{D} < 0$

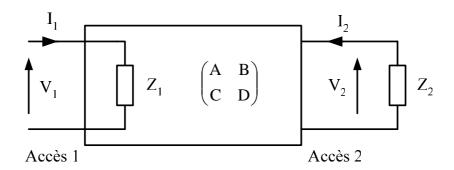

Cependant, l'utilisation d'éléments réels ne permet plus de vérifier ces deux principes. Le but est alors, compte tenu des parasites des éléments utilisés aux fréquences microondes, de connaître l'impédance complexe avec laquelle il va falloir charger le quadripôle à un de ses accès pour obtenir à un autre accès et à chaque fréquence l'impédance désirée.

## III.4 CALCUL DE L'IMPEDANCE DE CHARGE D'UN QUADRIPOLE EN FONCTION L'IMPEDANCE D'ENTREE DESIREE

Cette méthode de calcul qui permet de déterminer l'impédance de charge d'un quadripôle en fonction de l'impédance d'entrée désirée est développée dans l'annexe 1.

Nous montrons ainsi que dans la pratique, il suffira de charger l'accès 2 par l'opposé de  $Z_2^{"}$  pour obtenir Z1 à l'accès 1. Cette impédance de charge correspond au profil d'impédance passif à synthétiser.

#### III.5 BILAN

L'analyse des différents travaux réalisés jusque là sur les dispositifs actifs comportant des gyrateurs et des convertisseurs d'impédances négatives, constitue une excellente base aux études que nous avons menées.

Nous nous intéressons maintenant à l'étude d'un nouvel outil logiciel de conception (*Locus*), qui associé à des outils classiques, tels que ADS [31] ou Libra [32], permet de concevoir des circuits d'adaptations ou de compensations.

#### IV. Presentation du logiciel Locus

#### IV.1 INTRODUCTION

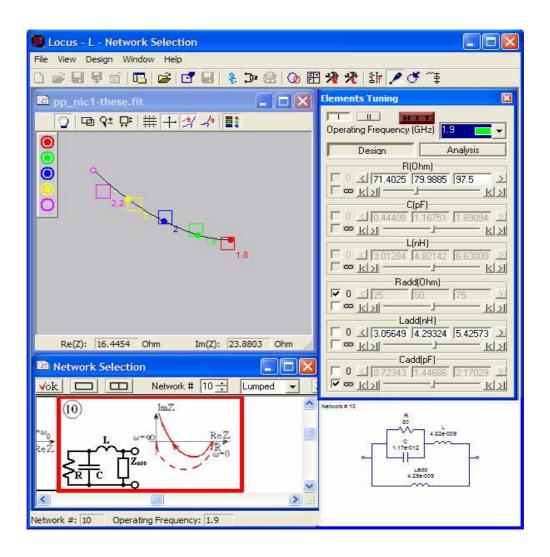

Nous avons conçus tous nos circuits simulant des résistances négatives, inductances actives et capacités négatives à l'aide du logiciel *Locus* [33].

L'utilisation de ce logiciel a fait l'objet d'une collaboration avec l'Université de Tomsk en Sibérie : Tomsk State University of Control System and Radioelectronics, dans le cadre d'un contrat INTAS.

Nous allons donc détailler ici le principe de fonctionnement de ce logiciel.

#### IV.2 Locus: Principe de fonctionnement

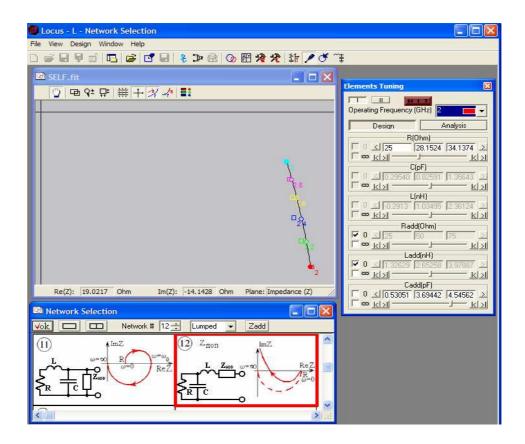

A l'opposé des logiciels classiques de type circuit, tels qu'ADS ou Libra, qui permettent de simuler une réponse à partir de la schématique d'un circuit donné, *Locus* détermine la topologie d'un circuit en fonction de la réponse souhaitée.

Cet outil logiciel est utilisé pour déterminer des réseaux passifs destinés à réaliser soit une adaptation soit une compensation de circuits passifs, ou actifs, RF et microondes. Il est fondé sur une représentation visuelle du processus de conception.

Pour expliquer son principe de fonctionnement, prenons le cas d'un dispositif quelconque.

Le but est d'obtenir à un des accès du dispositif, dans une bande de fréquence donnée, différentes performances de gain, d'adaptation ou/et de bruit imposées par un cahier des charges.

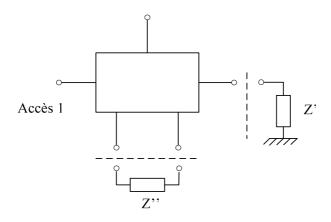

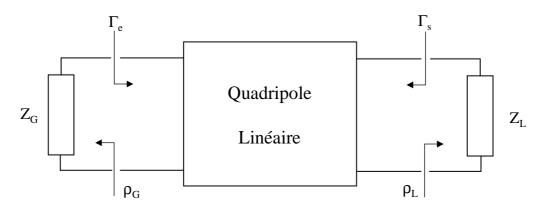

Le but est ainsi, pour chaque fréquence, de déterminer, quelle doit être l'impédance à présenter aux différents accès pour répondre aux performances requises (figure I-8).

Figure I-8

Exemple de dispositif avec ses impédances de fermetures.

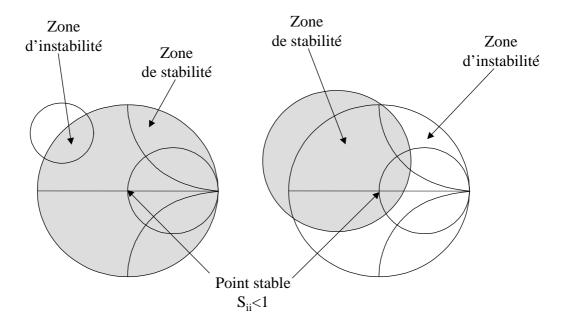

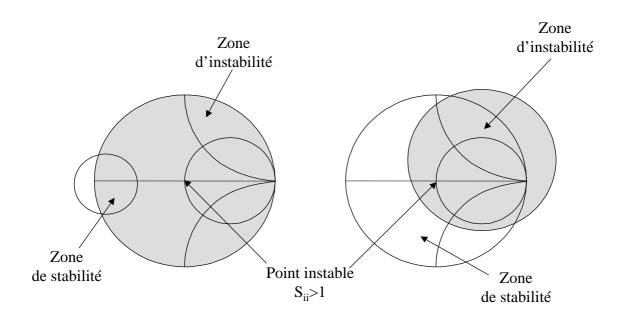

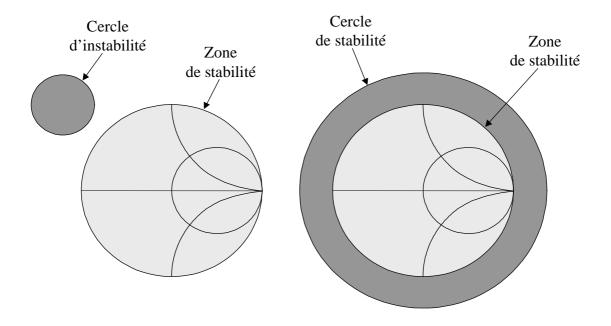

En spécifiant le cahier des charges sous forme de marges de performances, la technique permet d'aboutir, pour chaque paramètre (gain, adaptation, bruit, ...) à une zone d'impédance à l'intérieur de laquelle le paramètre est dans l'intervalle requis.

Ces zones d'impédance, appelées "Régions Acceptables" (RA), correspondent alors aux différentes valeurs d'impédance possibles du circuit passif de charge permettant d'obtenir à l'accès 1 les niveaux de performances compris dans les marges imposées par le cahier des charges.

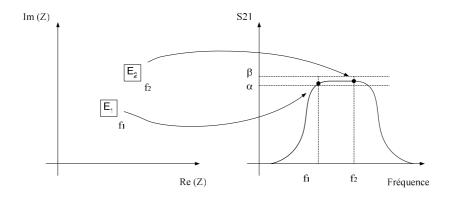

La figure I-9 montre, sur un exemple simple, des RA qui permettent d'obtenir le paramètre S21 aux fréquences  $f_1$  et  $f_2$  à l'intérieur de marges  $\alpha$  et  $\beta$  spécifiées. Ainsi, si l'on arrive à synthétiser une impédance dont la valeur est à l'intérieur de la région  $R_1$  on obtiendra une valeur, pour le paramètre S21, comprise entre  $\alpha$  et  $\beta$  et qui correspond à l'intervalle de performance requis par le cahier des charges.

Figure I-9  $Exemple \ de \ r\'egions \ acceptables \ permettant \ d'obtenir \ une \ valeur \ du \ paramètre \ S21$   $comprise \ entre \ \alpha \ et \ \beta \ aux \ fr\'equences \ f_1 \ et \ f_2$

Si plusieurs paramètres sont spécifiés à une même fréquence (gain, adaptation, bruit, ...), la région acceptable finale est l'intersection des régions acceptables de chacun des paramètres.

Une fois les régions acceptables déterminées fréquence par fréquence, *Locus* permet de déterminer un réseau passif dont l'impédance  $Z(j\omega_k)$  aux fréquences  $\omega_k$  passe par les régions acceptables respectives  $E_k$ :

$$Z(j\omega_k) \in E_k$$

,  $k = \overline{1, m}$

Ce procédé de conception nécessite deux étapes :

- 1) le choix de la configuration du réseau passif

- 2) la détermination des valeurs des éléments du réseau qui a été choisi

Un catalogue de réponses correspondant à différents types de réseaux passifs a été précompilé. On peut donc choisir, de manière visuelle, le circuit dont la réponse se rapproche le plus, en valeur et en comportement, du lieu des RA.

Dans la première étape, le réseau passif est donc choisit en fonction du tracé de l'impédance correspondante dans le plan complexe. Pour chaque fréquence, l'impédance doit se situer à l'intérieur de la RA correspondante.

Pour arriver à ce résultat, deux techniques sont possibles :

- Une première consiste à faire varier les valeurs des éléments du réseau considéré (capacités, inductances et/ou résistances) de manière à faire « rentrer » les points d'impédance à l'intérieur des différentes régions acceptables.

- Une autre méthode, interactive et très intuitive, consiste à sélectionner à l'aide de la souris un point d'impédance sur la courbe et à le faire glisser directement dans sa région acceptable. Les différentes valeurs des éléments s'adaptent automatiquement. On peut ainsi ajuster manuellement l'ensemble des points d'impédance dans l'ensemble des RA correspondantes.

#### IV.3 EXEMPLE DE CONCEPTION

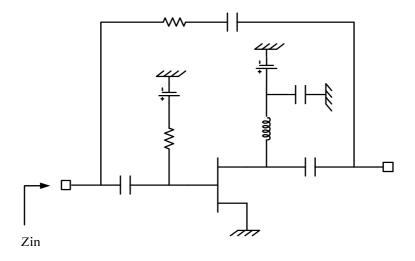

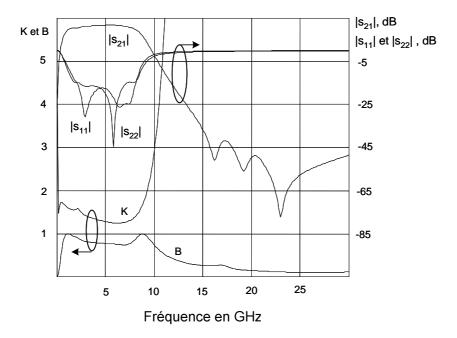

Nous prenons comme exemple, pour illustrer notre démarche, la réalisation d'un dispositif d'adaptation d'entrée d'un amplificateur faible bruit (LNA) dans la bande [8-10] GHz. La figure I-10 montre la topologie du LNA et ses caractéristiques initiales en transmission et en réflexion.

| Fréquence (GHz) | $\operatorname{Mod} S_{21}(dB)$ | $\operatorname{Mod} S_{11} (dB)$ | Re (Zin) Ω | Im (Zin) Ω |

|-----------------|---------------------------------|----------------------------------|------------|------------|

| 8               | 7.7                             | -5.7                             | 25.3       | -35.3      |

| 8.4             | 7.6                             | -5.5                             | 24         | -34.4      |

| 8.8             | 7.5                             | -5.3                             | 22.7       | -33.6      |

| 9.2             | 7.3                             | -5.2                             | 21.6       | -32.7      |

| 9.6             | 7.2                             | -5                               | 20.6       | -31.9      |

| 10              | 7                               | -4.9                             | 19.6       | -31.1      |

Figure I-10

Topologie et caractéristiques du LNA

Nous cherchons ici à rendre le module du paramètre S11 inférieur à -10 dB.

Pour adapter en entrée, de manière idéale, il faut Zin = 50 + 0j. L'idée est donc de placer à l'entrée un circuit permettant de ramener une impédance d'entrée proche de  $50 \Omega$ .

A partir de ces données (figure I-10), *Locus* permet de déterminer les différentes caractéristiques (profil d'impédance passive) que doit présenter en sortie le circuit d'adaptation lorsqu'il est chargé en entrée par  $50~\Omega$ , pour chacune des fréquences choisies dans la bande de travail.

Une tolérance de 1  $\Omega$  sur les parties réelle et imaginaire permet de construire les RA qui garantissent une valeur, pour le paramètre S11, inférieure à -10 dB.

Les données correspondantes sont sauvegardées dans un fichier (figure I-11) qui sera utilisé à l'étape suivante pour concevoir le réseau passif correspondant.

| Fichier | Edition Forn | nat Affichag | e ?      |          |     |

|---------|--------------|--------------|----------|----------|-----|

| %freq   | Re           | Im           | delta Re | delta IM | ^   |

| 1       |              |              |          |          |     |

| 8       | 24.7         | 31           | 1        | 1        |     |

| 8.4     | 26           | 32           | 1        | 1        |     |

| 8.8     | 27.3         | 33           | 1        | 1        |     |

| 9.2     | 28.4         | 34           | 1        | 1        |     |

| 9.6     | 29.4         | 34<br>35     | 1        | 1        |     |

| 10      | 30.4         | 36           | 1        | ti.      | 123 |

Figure I-11 Fichier correspondant aux différentes valeurs et tolérances (en  $\Omega$ ) des RA

Remarque : L'utilisation de *Locus* montre qu'il est plus facile de synthétiser un circuit dont les parties imaginaires des RA augmentent en fonction de la fréquence. Ainsi, si on se réfère au tableau de la figure I-10 la partie imaginaire de l'impédance à concevoir devrait diminuer avec la fréquence. Dans notre exemple, cela n'a que peut d'importance car nous cherchons ici à minimiser au maximum la partie imaginaire et à obtenir une partie réelle la plus proche de  $50\Omega$ .

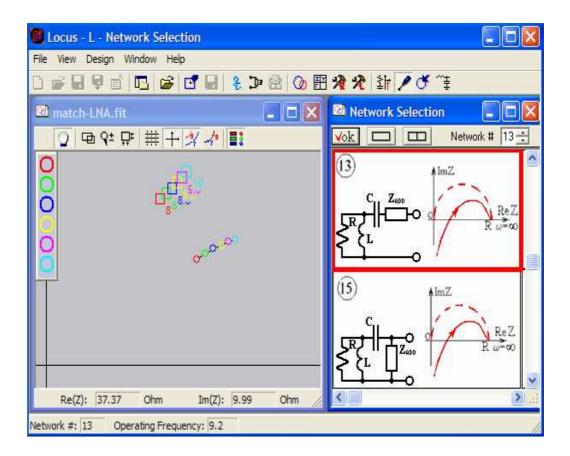

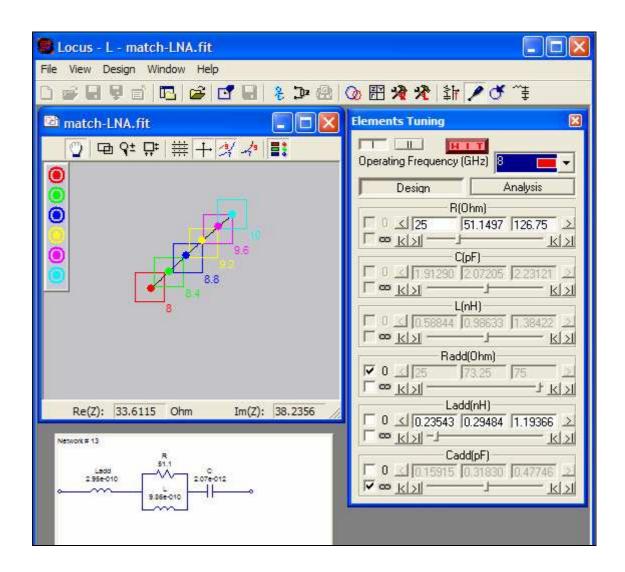

La figure I-12 présente l'interface de *Locus*. On reconnaît dans le plan Z les régions acceptables correspondant au fichier fourni à l'étape précédente. C'est la répartition de ces RA qui va dicter le choix de la topologie passive et le déroulement de la phase d'optimisation visuelle correspondante.

Dans notre exemple, le réseau choisi est constitué d'une capacité en série avec une résistance et une inductance placées en parallèle.

Figure I-12

Interface du logiciel *Locus*

La figure I-13 montre le résultat final de l'optimisation ayant permis de faire glisser les points d'impédance à l'intérieur des RA.

Figure I-13 Illustration du résultat de l'optimisation visuelle

Le circuit obtenu permet alors de ramener en entrée une impédance de 50  $\Omega$ . Cependant, une simulation sur Libra est nécessaire pour tester le circuit global (avec le réseau d'adaptation en entrée) et ainsi vérifier si les résultats sont conformes aux attentes. La figure I-14 montre la nouvelle topologie du LNA et ses caractéristiques en transmission et en réflexion.

Figure I-14

Topologie finale du LNA avec ses caractéristiques en transmission et en réflexion

#### IV.4 BILAN

Les outils présentés et les méthodes associées ont permis d'améliorer l'adaptation en entrée du circuit initial, et d'obtenir un paramètre S11 inférieur à -13 dB.

La partie suivante présente la conception d'une résistance négative et d'une inductance active en combinant *Locus* avec des logiciels classiques de type circuit tels que Libra et ADS.

# V. UTILISATION DE LOCUS POUR LA COMPENSATION DE CIRCUITS PASSIFS

### V.1 CONCEPTION D'UNE RESISTANCE NEGATIVE LARGE BANDE

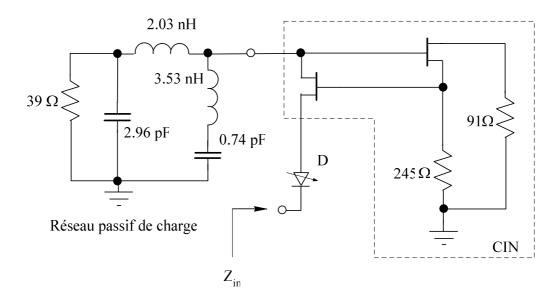

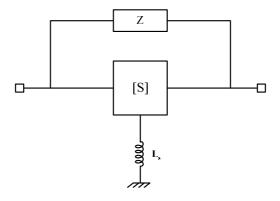

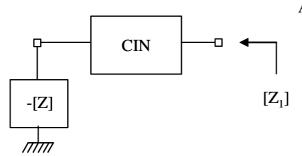

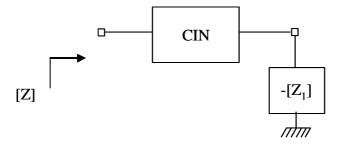

La topologie de base retenue pour concevoir notre résistance négative large bande est un convertisseur d'impédance négative (CIN).

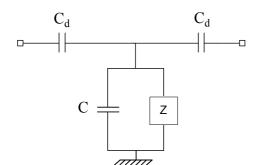

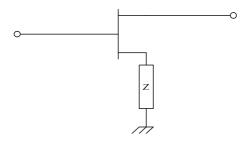

Le CIN (figure I-15) est un circuit actif à deux accès qui convertit une impédance de charge Z à un accès en une impédance d'entrée - kZ à l'autre accès.

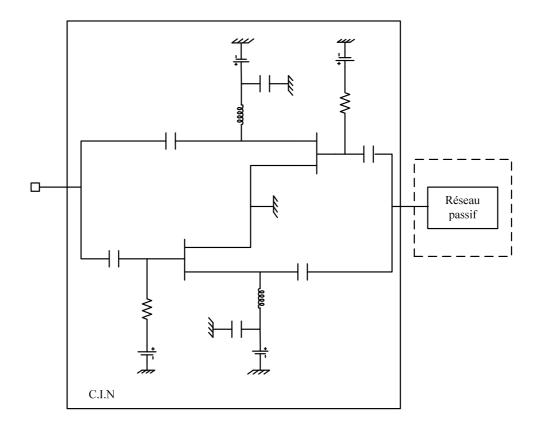

Figure I-15 Schéma de principe du CIN

# V.1.1 TOPOLOGIE RETENUE

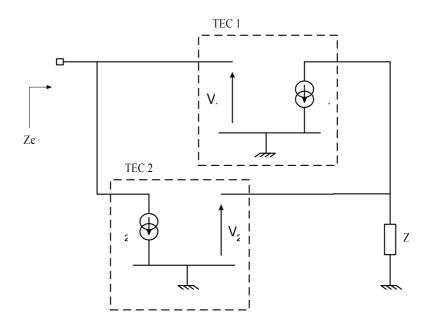

Une topologie de ce type de circuit, étudiée de manière détaillée par Ph. Meunier [8], se compose de deux transistors en rétroaction et d'une charge Z. Le circuit équivalent de la figure I-16 utilisant un modèle très simplifié pour les transistors permet d'exprimer simplement l'impédance d'entrée du dispositif :

Figure I-16 Schéma électrique simplifié d'un convertisseur d'impédance négative

$$Z_{e} = \frac{V_{1}}{I_{2}}$$

$V_{1} = \frac{I_{1}}{g_{m_{1}}}$   $I_{2} = g_{m2} V_{2}$

$$\Rightarrow \qquad Z_{e} = \frac{I_{1}}{g_{m1}} \ \frac{1}{-g_{m2} \ Z \, I_{1}} = \frac{-1}{g_{m1} \ g_{m2} \ Z}$$

L'impédance d'entrée se trouve alors de signe opposé à l'impédance de charge Z. Pour notre application, si cette charge est réalisée à l'aide d'une résistance, l'impédance d'entrée aura le comportement d'une résistance négative. Il faut noter que cette topologie est aussi de type « gyrateur ».

Cependant, d'un point de vue pratique, l'utilisation des composants du procédé monolithique utilisé (transistors et circuits de polarisation) ne permet plus de réaliser la fonction souhaitée. En effet, les composants s'écartent trop des modèles simplifiés choisis pour la démonstration.

C'est pourquoi nous utilisons ici une méthode présentée dans le paragraphe III.4 (calcul de l'impédance de charge d'un quadripôle), développée par S.E. Sussman-Fort, qui, combinée au logiciel *Locus*, va permettre de déterminer le circuit passif de charge du CIN permettant d'obtenir la résistance négative souhaitée en entrée.

#### V.1.2 DETERMINATION DU RESEAU PASSIF DE CHARGE DU CIN

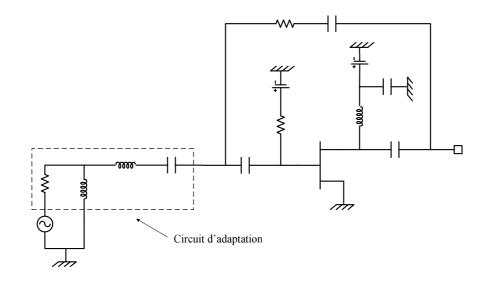

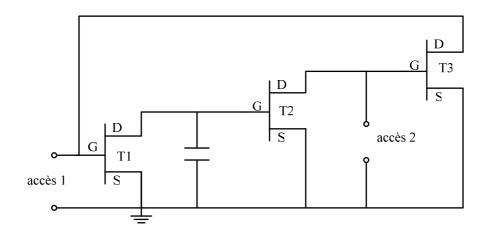

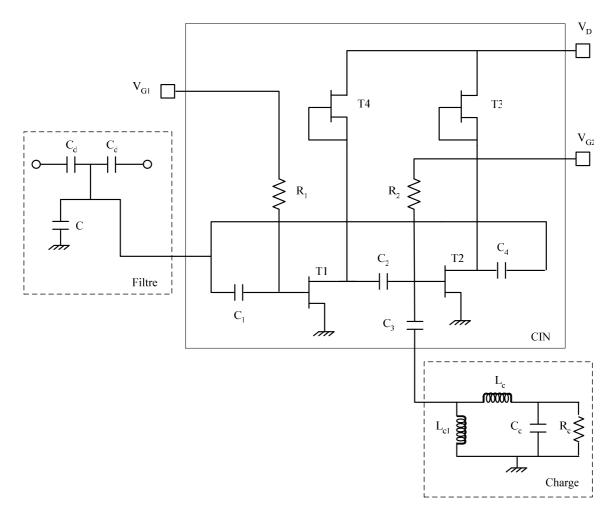

Pour cette application, notre objectif est d'obtenir une résistance négative pure sur une large bande autour de 3 GHz à l'aide du convertisseur d'impédance négative présenté sur la figure I-17.

Figure I-17

Schématique du convertisseur d'impédance négative

Une première étape consiste à déterminer, par la méthode Sussman-Fort, le réseau passif qui va charger le CIN (profil d'impédance passive). L'objectif est d'obtenir une impédance d'entrée de l'ordre de -10  $\Omega$  dans la bande [2-4 GHz] (annexe n°2). Le tableau I-1 donne les différentes valeurs d'impédance que doit présenter le réseau passif à chaque fréquence.

| Fréquence (GHz) | Partie réelle (Ω) | Partie imaginaire $(\Omega)$ |

|-----------------|-------------------|------------------------------|

| 2               | 13.8              | -6.4                         |

| 2.5             | 18.7              | -0.45                        |

| 3               | 19.8              | 3.4                          |

| 3.5             | 19.6              | 7.4                          |

| 4               | 19.1              | 11.5                         |

Tableau I-1 Valeur de l'impédance du réseau passif

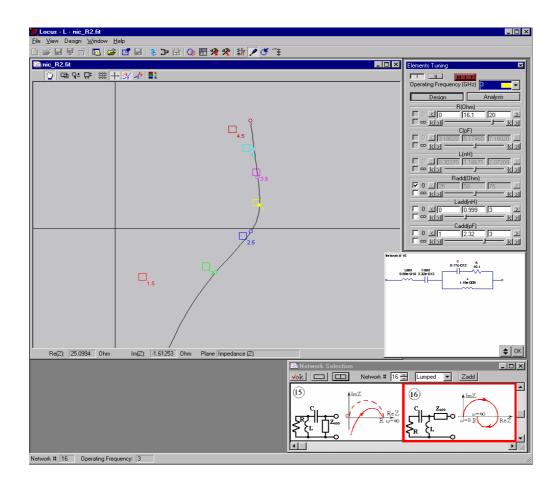

C'est à partir de ces résultats que *Locus* va permettre de déterminer le réseau passif s'approchant au mieux du profil ci-dessus. La figure I-18 montre le meilleur résultat obtenu après optimisation visuelle.

Figure I-18

Résultats d'optimisation obtenus avec le logiciel *Locus*

La schématique du circuit ainsi que les résultats de simulation obtenus (en éléments idéaux) pour l'impédance d'entrée  $Z_e$  sont présentés sur la figure I-19.

Figure I-19

Schématique du circuit final avec les résultats de simulation

# V.1.3 OPTIMISATION DU CIRCUIT EN ELEMENTS REELS RESULTATS DE SIMULATION

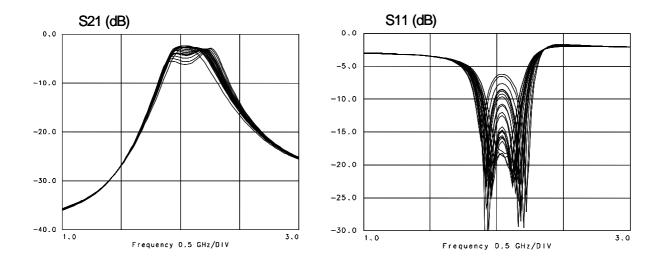

L'objectif est de concevoir, de façon simple, un circuit pouvant simuler une résistance négative, sur une large bande de fréquence, et capable de compenser les pertes d'une large gamme d'inductances spirales par simple réglage des tensions de polarisation des transistors.

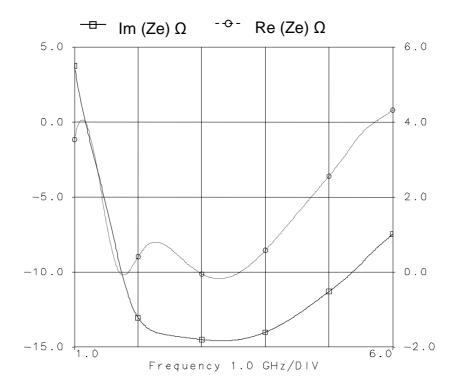

Ainsi, après avoir remplacé tous les éléments passifs idéaux par les éléments réels de la bibliothèque ED02AH de OMMIC [34], on obtient les résultats de simulation de l'impédance d'entrée  $Z_e$  de la figure I-20, pour des tensions de polarisation  $V_G$  = -0.22 V et  $V_D$  = 3.5 V du transistor.

$\label{eq:Figure I-20} Figure \ I-20$  Résultat de simulation pour  $V_G$  = -0.22 V et  $V_D$  = 3.5 V

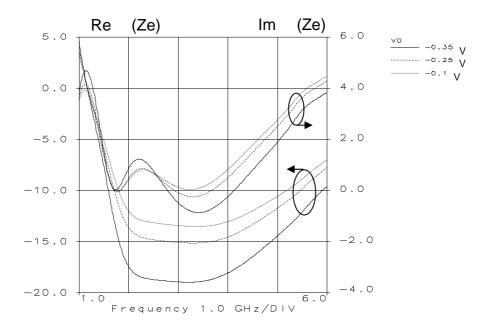

L'avantage d'un tel circuit est qu'il permet d'obtenir une large gamme de valeurs de résistances négatives par simple ajustement de la tension de polarisation  $V_G$ . Comme le montre la figure I-21, les parties réelles de l'impédance d'entrée  $Z_e$  sont relativement constantes dans la bande [2-4 GHz], comprises entre -13  $\Omega$  et -19  $\Omega$ . Les parties imaginaires sont comprises entre 1.2  $\Omega$  et -0.8  $\Omega$  pour une tension  $V_G$  variant de -0 .35 V à -0.1 V.

$\label{eq:Figure I-21}$  Impédance d'entrée pour  $V_G$  variant de -0.35 à -0.1 V

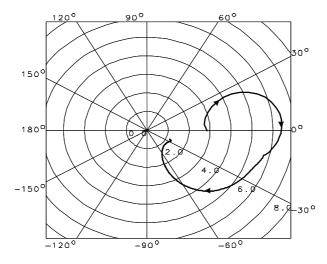

# V.1.4 STABILITE ELECTRIQUE

Comme tout circuit contenant des éléments actifs, le circuit que nous présentons nécessite une analyse de la stabilité électrique.

Cette analyse peut s'effectuer en calculant le déterminant de la matrice admittance nodale du circuit. La stabilité est vérifiée si le déterminant ne possède pas de zéro à partie réelle positive [35]. Une approche plus compatible avec les outils de simulation usuels, développée par Platzker, et adaptée aux simulations par S. Mons [36], consiste à employer la méthode de la NDF (Normalized Determinant Function) pour déterminer l'existence éventuelle de pôles à partie réelle positive intrinsèques au circuit à caractériser.

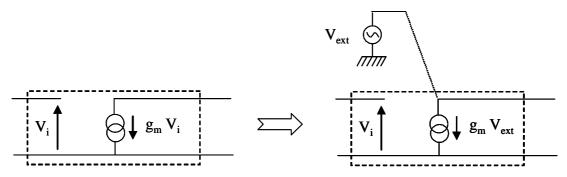

Le calcul de la NDF s'effectue en calculant les "return ratio" (taux de retour) des sources dépendantes du circuit (dans notre cas, il s'agit des sources liées aux transistors) :

$$NDF = (1+RR_1) (1+RR_2) ... (1+RR_N)$$

où RR<sub>i</sub> est le "return ratio" de la iéme source lorsque les i-1émes sources précédentes sont successivement éteintes (mises à zéro).

Dans le cas où les transistors sont modélisés par des sources de courant contrôlées en tension, les "return ratio", analogues à des rapports de tension dans ce cas, se calculent en déterminant, pour chaque source de courant contrôlée, la tension  $V_i$  ramenée à son accès d'entrée initial lorsque la source de courant est commandée par une source de tension externe  $V_{\text{ext}}$  comme indiqué sur la figure I-22.

Figure I-22 Source contrôlée nécessaire au calcul de la NDF

Le "return ratio" s'écrit alors :

$$RR = 1 - \frac{V_i}{V_{\rm ext}} \label{eq:return}$$

Le détail de la méthode est décrit dans [36]. L'application de la méthode de la NDF requiert donc de pouvoir agir sur le schéma électrique des éléments actifs. La bibliothèque mise à notre disposition ne permet pas cette modification. Pour effectuer le calcul de la NDF, nous avons donc dû établir un modèle des transistors présents dans notre circuit en nous appuyant sur un modèle petit signal équivalent et sur les mesures des éléments intrinsèques du modèle pour les points de polarisation utilisés. Ces renseignements sont disponibles dans le manuel de la bibliothèque.

Le fait de remplacer les modèles du fondeur utilisé lors de la conception par des modèles approchés introduit bien sûr certaines approximations et modifications de la réponse du circuit soumis à cette analyse.

Remarques : concernant les caractéristique de la fonction NDF

- La NDF est tracée sur une plage [0,f<sub>max</sub>]

- La fréquence maximale du tracé est limitée par la fréquence de simulation des modèles des composants d'une part, et d'autre part, par l'allure de la fonction NDF elle-même. Son tracé ne doit pas risquer d'entourer l'origine après f<sub>max</sub>.

- Pratiquement, la NDF tend vers (1,0) quand  $f \rightarrow \infty$ .

- Dans le cas d'un encerclement de l'origine dans le sens horaire, la fréquence d'oscillation se détermine par l'intersection du tracé avec le demi-axe réel négatif.

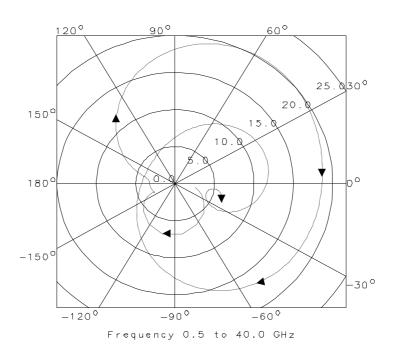

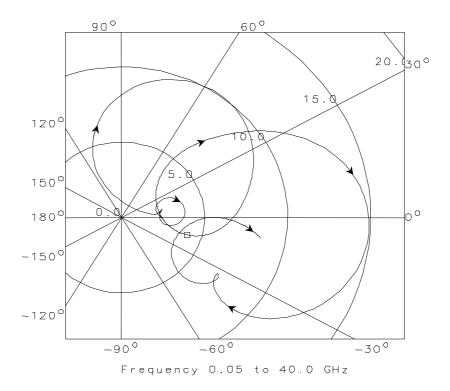

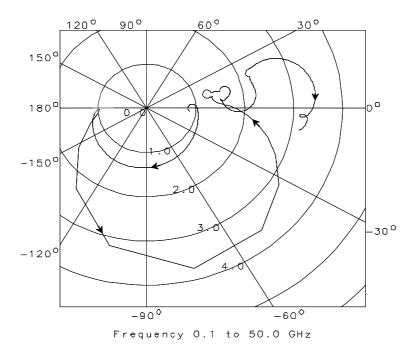

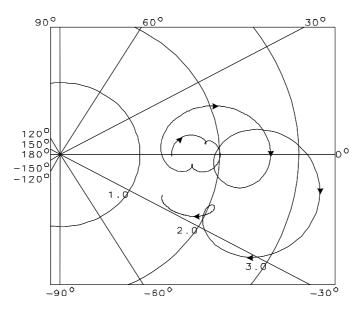

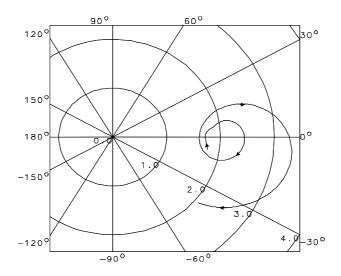

Le tracé de la NDF pour notre circuit dans le plan complexe est donné sur la figure I-23.

Figure I-23

Tracé de la fonction NDF

On remarque ici que la stabilité interne du circuit n'est pas assurée car le tracé de la fonction NDF entoure l'origine (0,0) du plan complexe dans le sens horaire quand la fréquence varie de  $0 \ alpha +\infty$ .

Il faut noter le fait que la structure choisie pour notre convertisseur d'impédance négative correspond à une structure classiquement utilisée pour la réalisation d'oscillateurs. En outre, le logiciel *Locus* ne permet que de déterminer l'impédance de fermeture du CIN qui donne l'impédance désirée en entrée, mais sans prendre en compte les problèmes de stabilité.

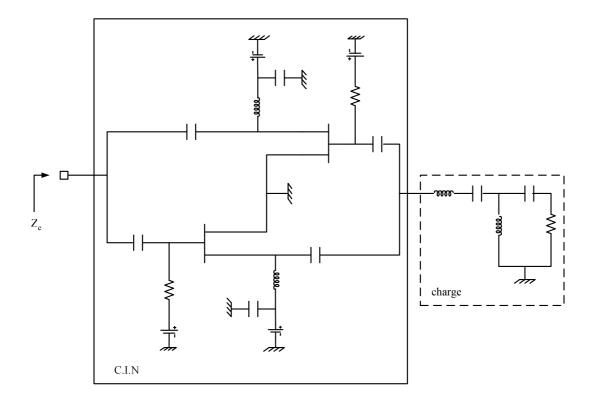

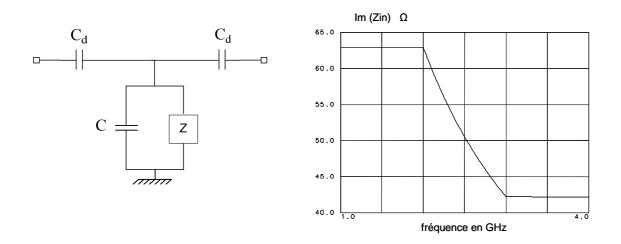

#### V.2 CONCEPTION D'UNE INDUCTANCE ACTIVE LARGE BANDE

De manière identique au paragraphe V.1, nous allons utiliser la même méthode pour concevoir une inductance active large bande à l'aide d'un gyrateur.

#### V.2.1 TOPOLOGIE RETENUE

#### DETERMINATION DU RESEAU PASSIF DE CHARGE

Afin de valider notre méthode de conception, nous souhaitons montrer que l'utilisation de *Locus* pour déterminer le réseau passif de charge à connecter à la topologie du gyrateur choisi, permet de synthétiser, à l'entrée du dispositif global, une multitude d'impédances purement imaginaires et linéaires dans une bande de fréquence donnée.

Ces impédances correspondent au profil d'impédance active que nous souhaitons réaliser.

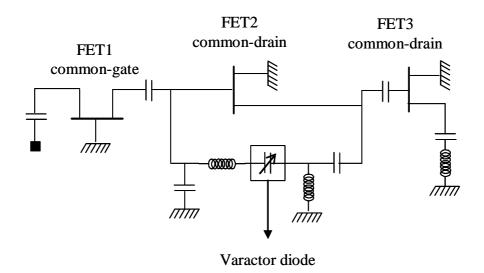

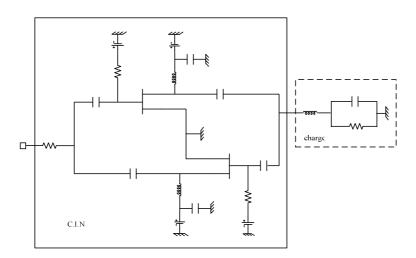

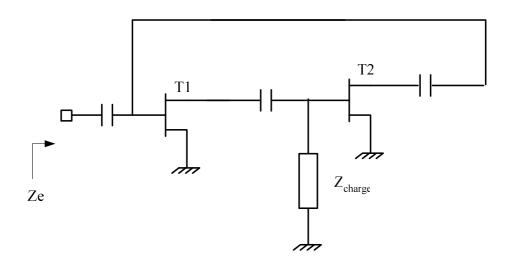

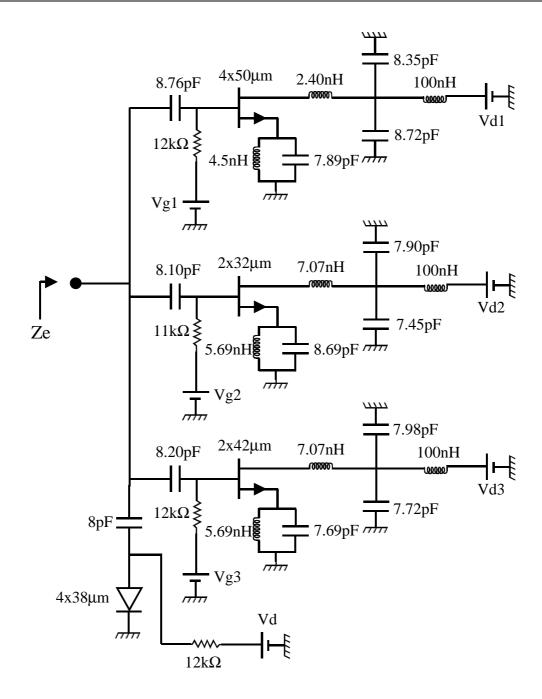

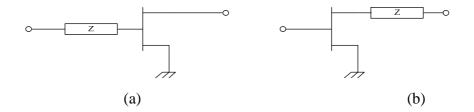

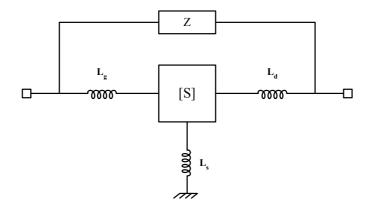

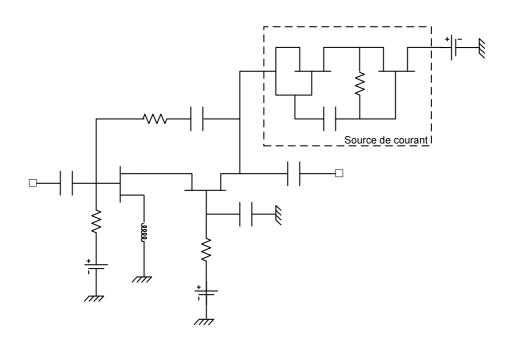

Nous désirons réaliser une inductance active pure dans la bande de fréquence [2-3 GHz] à l'aide du gyrateur présenté par S.E. Sussman-Fort et L. Billonnet dans [37] et présenté sur la figure I-24.

Figure I-24

Topologie du gyrateur retenue pour la conception d'une inductance active

La première étape consiste à synthétiser le réseau passif de charge (à l'accès 2) correspondant au profil d'impédance passive qui doit permettre d'obtenir en entrée (à l'accès 1) une impédance purement imaginaire équivalente à une inductance de l'ordre de 2.5 nH autour de 2.5 GHz.

Le tableau I-2 nous donne l'impédance du réseau passif à concevoir à l'aide de *Locus*.

| Fréquence (GHz) | Partie réelle (Ω) | Partie imaginaire (Ω) |  |  |

|-----------------|-------------------|-----------------------|--|--|

| 2               | 26                | -16.1                 |  |  |

| 2.2             | 25                | -13.4                 |  |  |

| 2.4             | 24.3              | -11                   |  |  |

| 2.6             | 24.2              | -8.9                  |  |  |

| 2.8             | 23.9              | -7                    |  |  |

| 3               | 23.6              | -5.2                  |  |  |

Tableau I-2 Valeur de l'impédance du réseau passif

A l'étape suivante (figure I-25), la technique consiste à trouver une topologie optimale de réseau passif avec lequel il est possible de faire passer tous les points d'impédances par les régions acceptables.

On note ici que cela n'a pas été possible, mais cette première approche permet déjà de synthétiser un circuit se rapprochant de façon satisfaisante de l'objectif, circuit qui devra de toute façon être optimisé avec le gyrateur à l'étape finale.

Figure I-25

Résultats obtenus avec *Locus*

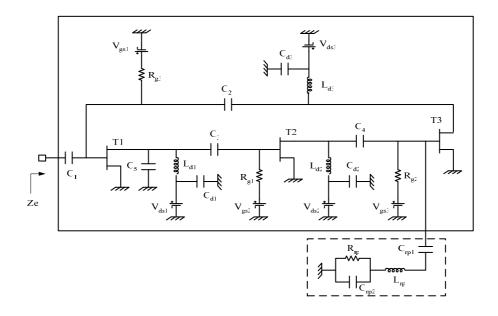

Le schéma électrique complet du circuit, avec le réseau passif de charge associé, est présenté sur la figure I.26

Figure I-26 Schéma électrique complet avec le réseau passif de charge associé

Les valeurs des composants sont répertoriées dans le tableau I-3

| I<br>N<br>D<br>U<br>C<br>T<br>A<br>N<br>C<br>E<br>S | $L_{d1}$ , $L_{d2}$ et $L_{d3}$ :  Eléments idéaux de fortes valeurs $\cong 1000 \text{ nH}$ $L_{rp} = 1.23 \text{ nH}$ | C<br>A<br>P<br>A<br>C<br>I<br>T<br>E<br>S | $C_{d1}$ , $C_{d2}$ et $C_{d3}$ :  Eléments idéaux de fortes valeurs $\cong 1000 \text{ pF}$ $C_1 = C_2 = C_3 = C_4 = 8 \text{pF}$ $C_5 = 6 \text{ pF}$ $C_{p1} = 0.8 \text{ pF}$ $C_{p2} = 3.7 \text{ F}$ | R E S I S T A N C E S | $R_{g1}, R_{g2}$ et $R_{g3}$ : Eléments idéaux de fortes valeurs $\cong 5000 \Omega$ $R_{rp} = 28 \Omega$ | T<br>R<br>A<br>N<br>S<br>I<br>S<br>T<br>O<br>R<br>S | T1 : 6×10 μm<br>T2 : 6×50 μm<br>T3 : 6×10 μm |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------|

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------|

Tableau I-3

Valeurs des composants du circuit

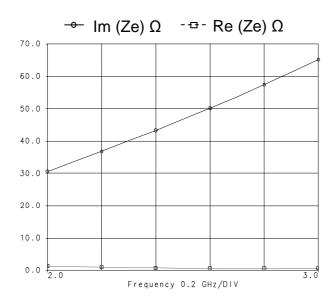

Ce circuit permet donc d'obtenir une impédance purement imaginaire et linéaire, dans la bande de fréquence [2-3 GHz], et équivalente à une inductance de l'ordre de 2.8 nH à 2.5 GHz.

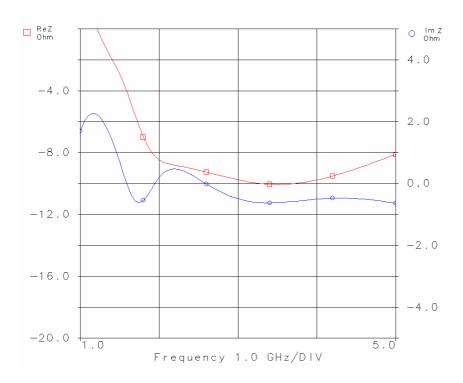

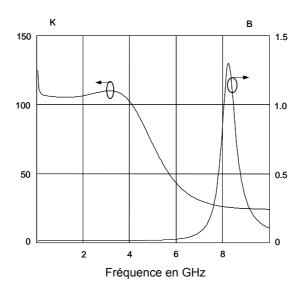

Les courbes de la figure I-27 présentent les parties réelle et imaginaire obtenues à partir du circuit présenté sur la figure I-26 et sans aucune phase d'optimisation.

Figure I-27

Partie réelle et imaginaire de l'inductance active

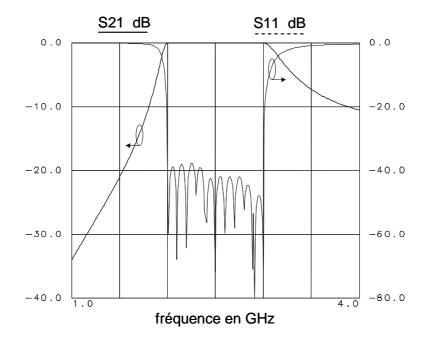

# V.2.2 DESSIN DE MASQUE ET OPTIMISATION DU CIRCUIT EN ELEMENTS REELS RESULTATS DE SIMULATION

Pour concevoir le circuit, nous utilisons le procédé de fabrication monolithique ED02AH de OMMIC. Le dessin de masque (layout) a été réalisé en utilisant les règles décrites dans le manuel de conception (Design Manual).

Au fur et à mesure de la phase de conception du layout, plusieurs cycles d'optimisation ont été nécessaires pour maintenir les objectifs de performances. Malgré cela, l'introduction des circuits de polarisation en éléments réels ainsi que les lignes et les différents plots de masse nous ont obligé à réduire de moitié la bande de fréquence dans laquelle nous souhaitions une inductance active pure.

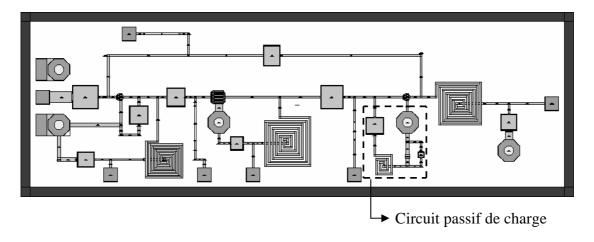

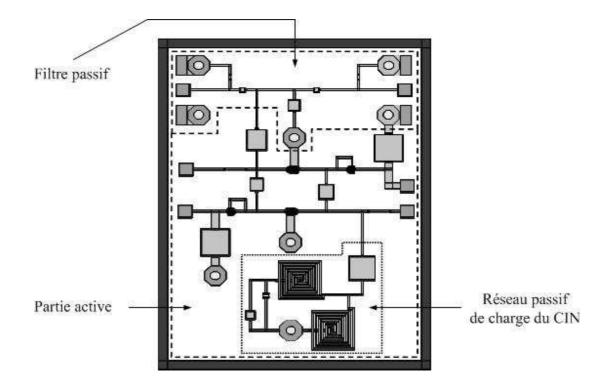

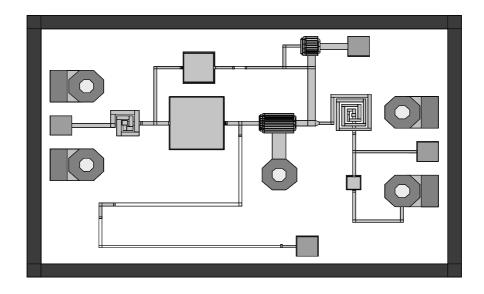

Sur la figure I-28, qui présente le masque final, on peut repérer le gyrateur avec son circuit passif de charge associé, ainsi que les tensions appliquées aux différents plots de polarisation.

Figure I-28

Masque de l'inductance active

Les dimensions de la puce sont de  $1 \times 3 \text{ mm}^2$ .

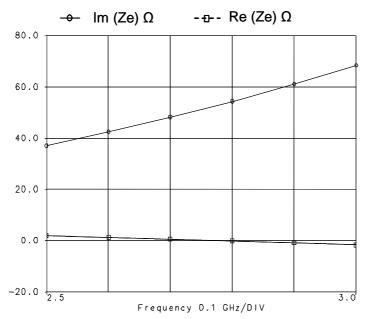

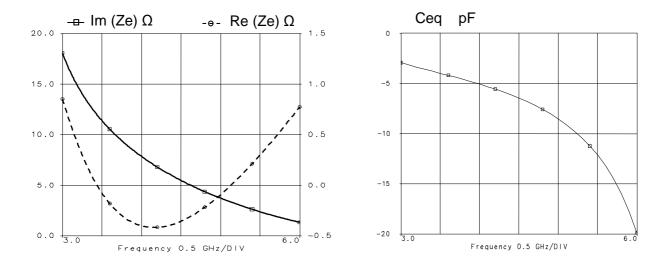

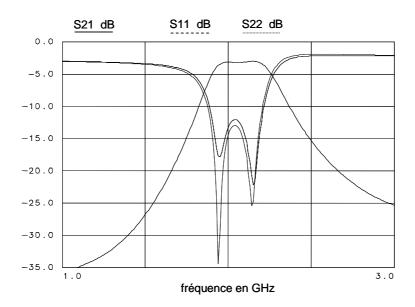

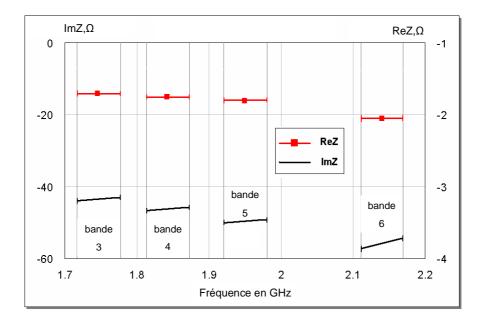

Les résultats de simulations de l'impédance d'entrée de ce circuit sont présentés sur la figure I-29.

Figure I-29

Résultats de simulation de l'inductance active

La partie imaginaire est purement linéaire et correspond à une inductance de l'ordre de 2.8 nH à 2.75 GHz. La partie réelle associée est proche de zéro (ici entre 2 et -2 ohms) sur toute la bande de fréquence considérée.

Les différentes valeurs des éléments du circuit, ainsi que des tensions de polarisation obtenues après l'ultime phase d'optimisation sont présentées dans le tableau I-4.

| I<br>D<br>U<br>C<br>T<br>A<br>N<br>C<br>E<br>S | $En nH  L_{d1} = 3.5  L_{d2} = 5  L_{d3} = 4.5  L_{rp} = 0.7$ | C<br>A<br>P<br>A<br>C<br>I<br>T<br>E<br>S | En pF<br>$C_{d1} = C_{d3} = 3$<br>$C_{d2} = 2$<br>$C_{1} = 7$<br>$C_{2} = C_{3} = 4$<br>$C_{4} = 6.2$<br>$C_{5} = 5$<br>$C_{rp1} = 0.3$<br>$C_{rp2} = 3.8$ | R<br>E<br>S<br>I<br>S<br>T<br>A<br>N<br>C<br>E<br>S | En $\Omega$ $R_{g1} = 4000$ $R_{g2} = 4000$ $R_{g3} = 2000$ $R_{rp} = 30$ | T<br>R<br>A<br>N<br>S<br>I<br>S<br>T<br>O<br>R | T1: 6×10<br>μm<br>T2: 6×50<br>μm<br>T3: 6×10<br>μm | T<br>E<br>N<br>S<br>I<br>O<br>N<br>S | $V_{gs1} = 0 \text{ V} \\ V_{gs2} = 0 \text{ V} \\ V_{gs3} = 0 \text{ V} \\ V_{ds1} = 1.86 \\ V \\ V_{ds1} = 3.3 \text{ V} \\ V_{ds1} = 1.83 \\ V$ |

|------------------------------------------------|---------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|------------------------------------------------|---------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

Tableau I-4

Valeurs des différents éléments du layout

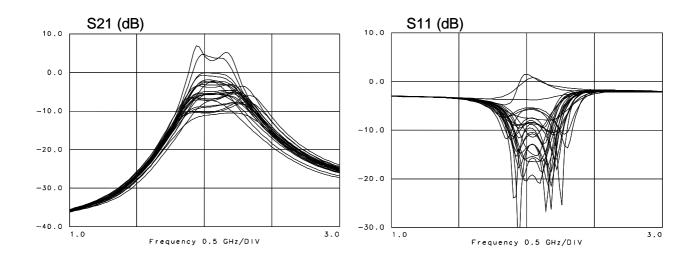

#### V.2.3 ETUDE DE SENSIBILITE

La conception d'un dispositif monolithique nécessite systématiquement une étude de sensibilité de la réponse du circuit aux variations des caractéristiques des éléments qui le constituent. En effet, les caractéristiques des composants peuvent varier dans des proportions non négligeables lors de l'étape finale de fabrication. Il est donc nécessaire, avant la phase de réalisation, d'évaluer l'effet de tous les éléments du circuit sur la réponse.

Le pourcentage de variation possible des valeurs des éléments est déterminé d'après le manuel de la bibliothèque ED02AH.

■ Self-inductances: ± 5 %

■ Capacités: ± 5 %

■ Résistances : ± 5 %

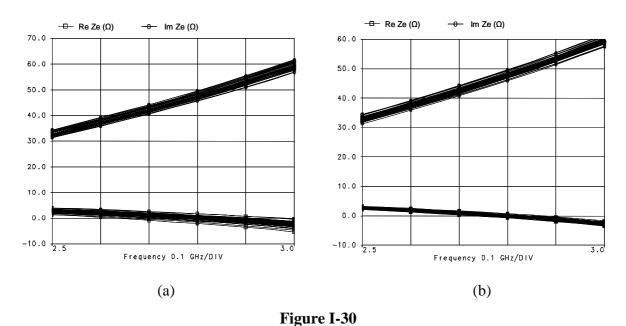

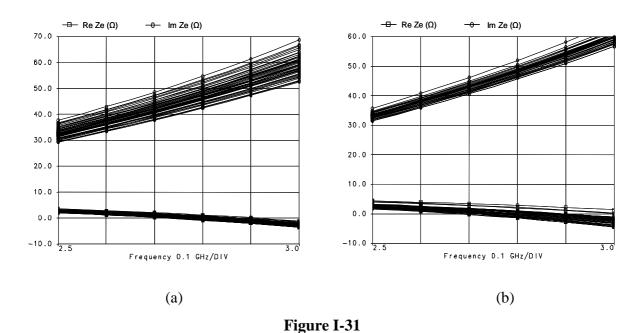

Les résultats de l'analyse de type Monté-Carlo sont présentés sur les figures I-30 et I-31.

Sensibilité de l'impédance d'entrée de l'inductance active aux variations des capacités de découplage (a) et des circuits de polarisation (b).

Sensibilité de l'impédance d'entrée de l'inductance active aux variations de la capacité  $C_5$  (a) et du réseaux passif de charge (b).

On remarque que seule une variation de la capacité  $C_5$  entraı̂ne une modification non négligeable de la partie imaginaire de l'impédance d'entrée de l'inductance active.

Cependant, il faut noter que, dans tous les cas, les tensions de polarisation des transistors permettent un réajustement des caractéristiques recherchées, notamment en cas de dérive de certains paramètres du procédé monolithique.

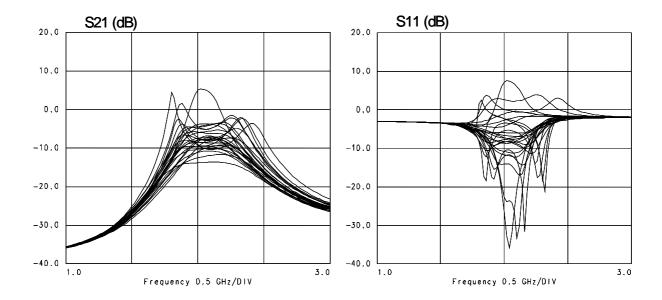

# V.2.4 STABILITE ELECTRIQUE

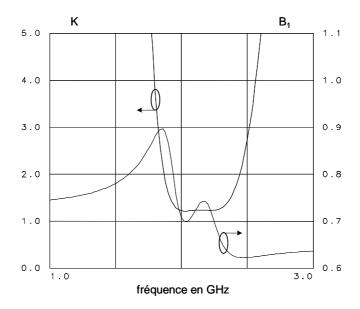

Nous étudions ici, comme dans le paragraphe V.1.4, le tracé de la NDF pour vérifier la présence d'instabilité intrinsèque du circuit. Le calcul de cette fonction se fait en déterminant les "return ratio" des sources dépendantes du circuit.

Dans ce cas :  $NDF = (1+RR_1) (1+RR_2)$ .

où  $RR_i$  est le "return ratio" de la  $i^{\grave{e}me}$  source lorsque les i- $1^{\grave{e}mes}$  sources précédentes sont successivement éteintes.

Le tracé de la NDF du circuit dans le plan complexe est donné sur la figure I-32.

Figure I-32

Tracé de la fonction NDF

La stabilité interne du circuit est ici assurée car le tracé de la fonction NDF n'entoure pas l'origine (0,0) du plan complexe dans le sens horaire, quand la fréquence varie de  $-\infty$  à  $+\infty$ .

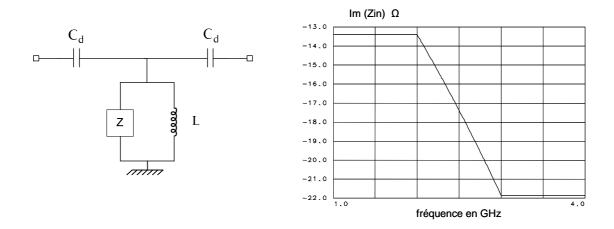

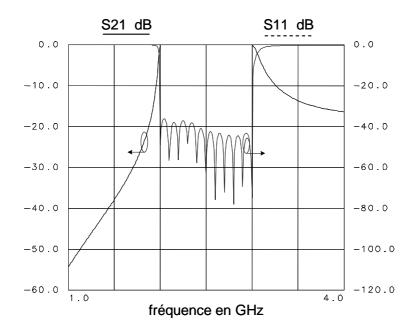

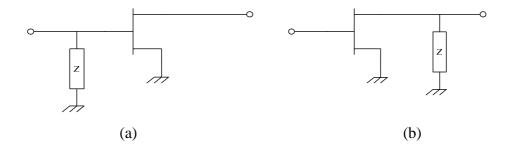

#### V.3 ETUDE D'UNE CAPACITE NEGATIVE PURE LARGE BANDE

Nous présentons dans cette partie les résultats de simulation obtenus pour une capacité négative large bande dans la bande [3-6 GHz].

Nous utilisons ici la même méthode de conception que celle utilisée dans les deux paragraphes précédents pour la résistance négative et l'inductance active.

La capacité négative que nous souhaitons concevoir doit posséder une partie imaginaire positive et décroissante en fonction de la fréquence ainsi qu'une partie réelle nulle sur toute la bande.

Seulement quelques exemples de réalisation de capacités négatives ont été publiés à ce jour dans la littérature. S.E. Sussman-Fort et L. Billonnet utilisent pour leur réalisation [31] un convertisseur d'impédance négative. Nous reprenons cette structure pour l'adapter à nos objectifs et à notre bande de fréquence.

La figure I-33 présente le schéma électrique complet de la topologie choisie.

Figure I-33 Schéma électrique de la topologie retenue

L'impédance d'entrée et la capacité équivalente synthétisées dans la bande [3-6 GHz] sont présentées sur la figure I-34.

Figure I-34

Impédance d'entrée et capacité équivalente du circuit simulant une capacité négative

Dans la bande [3-6 GHz], la partie réelle est comprise entre  $0.8~\Omega$  et -0.4  $\Omega$  pour une partie imaginaire positive et décroissante en fonction de la fréquence variant entre  $18.1~\Omega$  et  $1.3~\Omega$ . Cela correspond à une valeur de capacité de -3 pF à 3 GHz et de -20 pf à 6 GHz.

### V.4 BILAN

Après une description des fonctionnalités du logiciel *Locus* et quelques rappels sur les caractéristiques des gyrateurs et des convertisseurs d'impédance négative, nous avons simulé une inductance active en technologie monolithique sur la bande de fréquence [2,5-3 GHz].

Nous avons montré ici que l'association des logiciels tel que ADS (ou Libra) et *Locus* permet de mettre en place une nouvelle approche de conception de résistances négatives, d'inductances actives et de capacités négatives, plus efficace, plus systématique, et aussi plus intuitive.

# VI. CONCLUSION

Dans ce chapitre, nous nous sommes intéressés à une nouvelle méthode de conception de dispositifs actifs destinés à la compensation ou à l'amélioration des performances des systèmes passifs.

Grâce à la collaboration établie avec l'Université de Tomsk, nous avons pu bénéficier du logiciel *Locus*, logiciel qui a permis de mettre en place une nouvelle approche de conception de circuits d'adaptation ou de compensation.

Les recherches bibliographiques qui ont été menées, nous ont permis de bien situer l'évolution scientifique dans ce domaine, et nous ont amené à déterminer les différents avantages et inconvénients d'une telle méthode :

Avantages: - méthode plus souple et plus systématique

- amélioration du temps de conception

- possibilité de conception sur de large bande de fréquence

- méthode simple et visuelle

- circuits résultants plus simples et plus compacts

Inconvénients : - non prise en compte des phénomènes de stabilité

La prise en compte des phénomènes de stabilité lors de la conception de circuit à l'aide de *Locus* est une des perspectives de nos travaux. Ces phénomènes de stabilité font déjà l'objet de plusieurs études par les concepteurs du logiciel à l'Université de Tomsk.

Dans la suite, nous allons d'appliquer ces nouvelles méthodes pour concevoir un filtre actif original où la notion de profil d'impédance active sera mise à profit.

# **CHAPITRE II**

Conception de filtres actifs utilisant la notion de profil d'impédance active

# I. INTRODUCTION

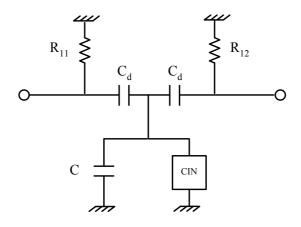

Dans ce chapitre, nous présentons la conception de deux filtres actifs en technologie monolithique utilisant la bibliothèque ED02AH de la fonderie OMMIC, ainsi qu'un circuit permettant de concevoir un filtre multinorme.

Ce chapitre est essentiellement basé sur une nouvelle méthode de synthèse des circuits actifs. Cette méthode consiste en la réalisation de profils d'impédances actives dont le rôle est de corriger les pertes de structures passives, d'adapter la taille de filtres passifs, de contrôler les fréquences de travail et les bandes passantes, ainsi que d'augmenter artificiellement le nombre de pôles de la réponse de ces mêmes filtres.

La première partie de ce chapitre est donc consacrée au principe du profil d'impédance.

Dans les deuxième et troisième parties, nous utilisons la méthode du profil d'impédance active pour réaliser un filtre passe-bande sélectif faible bande dans le premier cas, et un filtre pseudo multipôle dans le deuxième cas.

Enfin, dans une quatrième partie, nous détaillons les résultats d'un circuit actif destiné à concevoir un filtre multinorme, afin de valider notre méthode de conception.

# II. PRINCIPE DU PROFIL D'IMPEDANCE

#### II.1 DEFINITION DU PROFIL D'IMPEDANCE ACTIVE

Un profil d'impédance est un gabarit complexe en fréquence défini en parties réelle et imaginaire, et utilisé pour une amélioration significative des performances d'un filtre passif. Cette amélioration peut porter sur :

la réduction ou l'annulation des pertes de la structure filtrante passive,

- l'adaptation de la taille du circuit global (filtre passif + profil d'impédance),

- le contrôle continu ou discret de la fréquence de travail,

- le contrôle de la largeur de la ou des bandes passantes du filtre.

La compensation des pertes de la structure filtrante passive est assurée par la partie réelle du profil d'impédance actif. Cette partie réelle doit donc, dans la plupart des cas, et pour certaines gammes de fréquence, être négative. Aussi, on parlera dans la suite le Profil d'Impédance Active.

La modification de la taille du circuit global (augmentation ou réduction selon les besoins) provient directement de l'influence de la partie imaginaire du profil d'impédance active qui modifie électriquement les longueurs équivalentes des résonateurs à l'intérieur de la structure. L'ajustement des longueurs physiques des résonateurs qui peut ainsi être fait permet de jouer sur la taille des parties passives. Conjointement, la partie imaginaire du profil d'impédance active intervient donc également sur la fréquence centrale du filtre.

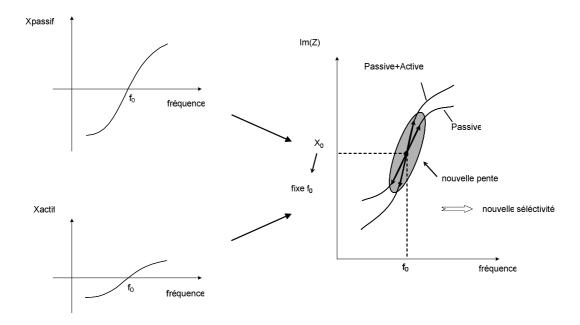

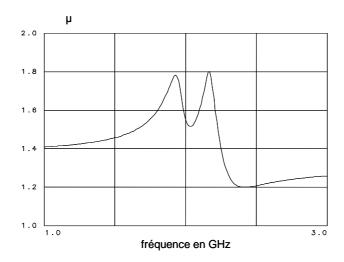

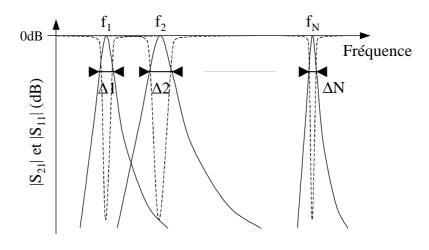

La bande passante de la structure filtrante peut être modifiée grâce au contrôle de la pente de la partie imaginaire de profil d'impédance active (figure II-1).

$\label{eq:Figure II-1}$  Exemple de modification de la pente de la réactance globale à la fréquence  $f_0$

# II.2 CONTROLE DE LA FREQUENCE CENTRALE

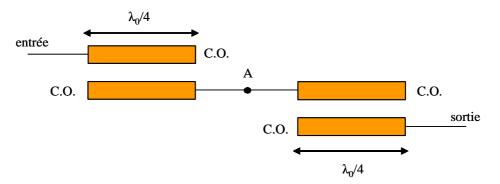

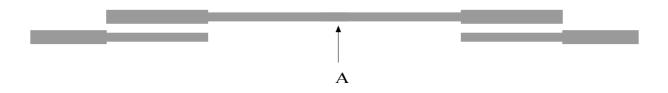

Considérons un filtre passe-bande distribué constitué d'un résonateur  $\lambda_0/2$  couplé à l'entrée et à la sortie sur des longueurs  $\lambda_0/4$  et terminé à ses accès par des circuits ouverts (figure II-2).

Figure II-2

Filtre passe-bande à résonateurs distribués

Ce filtre passif, dont la fréquence de résonance est  $f_0$ , possède des pertes d'insertions non nulles. Il est possible en insérant un circuit simulant une résistance négative au milieu du résonateur  $\lambda_0/2$  (au point A) de compenser les pertes du circuit. Cependant, pour ne pas modifier la fréquence centrale du filtre, il faut que la partie imaginaire du circuit de compensation soit nulle à cette fréquence centrale.

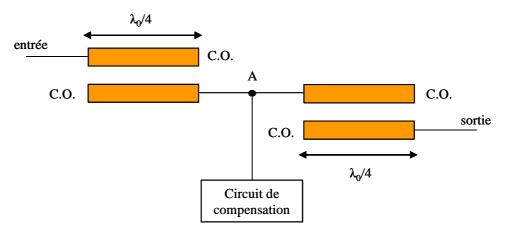

Le schéma du filtre aux pertes compensées est présenté sur la figure II-3. Il est constitué de deux résonateurs  $\lambda_0/4$  et d'un circuit de compensation.

Figure II-3 Schéma du filtre aux pertes compensées

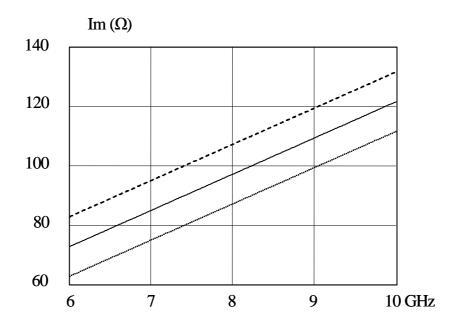

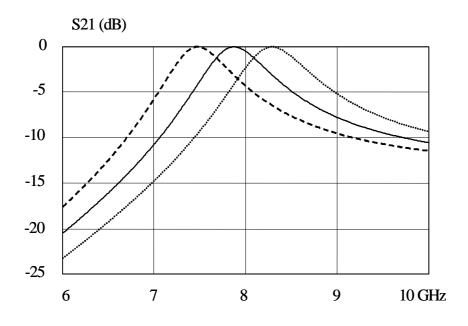

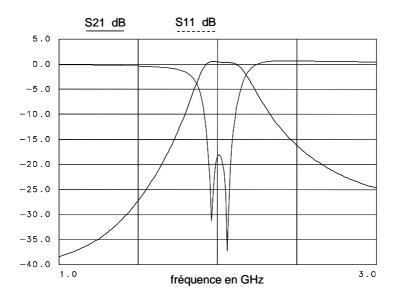

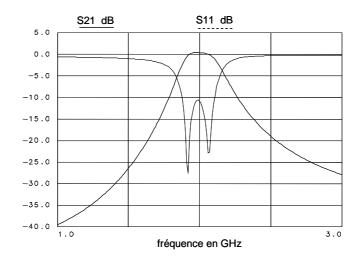

Les résultats de simulation de la partie imaginaire du circuit de compensation et de la réponse du filtre aux pertes compensées sont présentés sur les figures II-4 et II-5.

Figure II-4

Partie imaginaire du circuit de compensation

Figure II-5 Réponse du filtre aux pertes compensées

Ces résultats de simulation montrent qu'une augmentation de la valeur de la partie imaginaire entraı̂ne une évolution de la fréquence de résonance du filtre vers les fréquences

basses. Il est donc possible d'ajuster la fréquence centrale d'un tel filtre à une fréquence donnée tout en compensant ses pertes.

Les travaux développés par D. Denis [38] ont montré que la nature de l'impédance de charge des résonateurs qui, dans notre cas est un circuit ouvert, influe sur la fréquence de résonance du filtre. Une charge de type capacitive a pour effet de diminuer la fréquence centrale du filtre, alors qu'une charge de type inductive l'augmente.

# II.3 CONTROLE DE LA BANDE PASSANTE

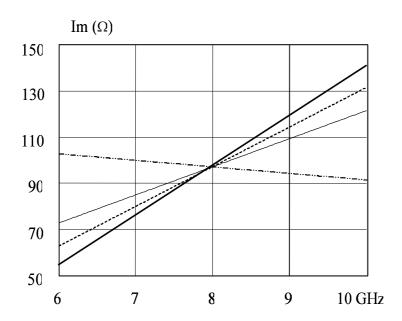

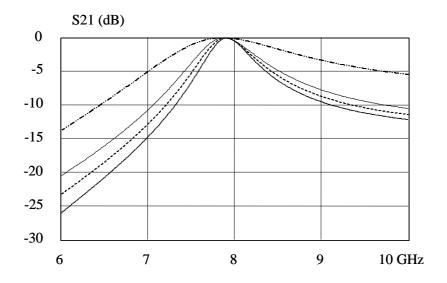

En gardant le même circuit que celui de la figure II-3, les résultats de simulation présentés sur les figures II-6 et II-7 montrent l'évolution de la largeur de la bande passante avec la pente de la partie imaginaire du circuit de compensation.

Figure II-6

Partie imaginaire du circuit de compensation

Figure II-7

Réponse du filtre aux pertes compensées

Pour une partie imaginaire de pente positive, la largeur de la bande passante du filtre croît quand la valeur de la pente diminue. Pour une partie imaginaire de pente négative, la bande passante décroît avec la valeur absolue de la pente.

Les principes présentés ici, qui sont liés à la structure même du dispositif, peuvent donc être utilisés pour améliorer les performances des filtres telles que la fréquence centrale et la sélectivité.

## II.4 DEMARCHE DE CONCEPTION

La démarche de conception d'un filtre utilisant la notion de profil d'impédance active comporte les étapes suivantes :

- conception de la partie passive initiale,

- calcul du profil d'impédance active : à partir du filtre passif initial réalisé, de la modification de taille prévue, et de la réponse du filtre global souhaitée, les valeurs des parties réelle et imaginaire sont extraites fréquence par fréquence.

• conception de la partie active : on détermine indépendamment la topologie qui permet de réaliser, au mieux, les parties réelle et imaginaire définies à l'étape précédente.

On comprend donc bien que ces deux dernières étapes permettent de réduire la taille d'un circuit et de modifier la fréquence centrale et la bande passante de la réponse d'un filtre ou donc, intuitivement, d'augmenter artificiellement son nombre de pôles. Nous allons donc maintenant développer cette méthode afin de concevoir un filtre actif sélectif ainsi qu'un filtre actif pseudo-multipôles.

#### III. APPLICATION A LA CONCEPTION D'UN FILTRE ACTIF SELECTIF

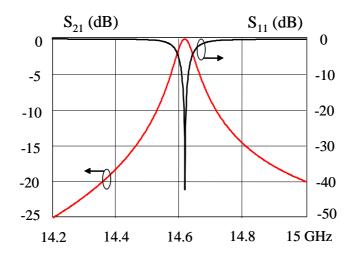

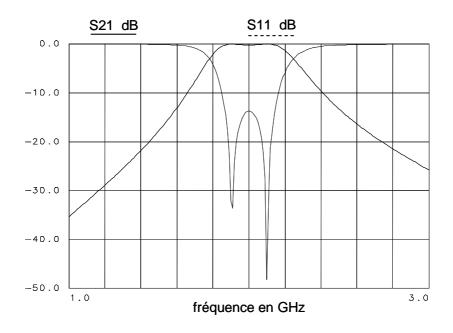

Dans cette partie, nous allons utiliser la notion de profil d'impédance, présenté dans ce chapitre, pour concevoir un filtre passe-bande sélectif qui a été développé avec Sébastien DARDILLAC [39]. Ce filtre a une bande passante d'environ 60 MHz autour de 15 GHz et utilise un circuit actif pour compenser des pertes et modifier sa sélectivité et sa fréquence centrale.

#### III.1 CONCEPTION DE LA PARTIE PASSIVE DU FILTRE

Dans cette partie, nous souhaitons obtenir une réponse de filtrage ayant une fréquence centrale proche de 15 GHz avec 60 MHz de bande passante.

La partie passive initiale en éléments distribués est présentée sur la figure II-8.

Figure II-8 Filtre passif en éléments distribués

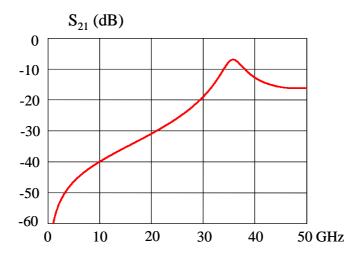

La longueur du résonateur est de 1,7 mm et sa fréquence de résonance ainsi obtenue est de 35 GHz (figure II-9).

Figure II-9 Réponse en transmission de la partie passive du filtre

La suite de l'étude consiste maintenant à associer un circuit actif à ce filtre pour ramener la fréquence de résonance à 15 GHz avec une bande passante de 60 MHz, tout en compensant les pertes d'insertion à la fréquence centrale.

La topologie et les dimensions du filtre passif ont été déterminées en fonction des différentes tailles de puce mises à notre disposition (cf. chapitre I. V.2.2) et de l'impédance que nous devions synthétiser au point A pour répondre à notre cahier des charges.

En effet, pour d'autres topologies de filtre que celle présentée ci-dessus, la partie active à concevoir pour obtenir la réponse souhaitée aurait été plus complexe.

### III.2 EXTRACTION DE LA PARTIE ACTIVE

La deuxième étape de la démarche vise à extraire les parties réelle et imaginaire du circuit actif à associer au point A de la partie passive.

Pour ce faire, nous calculons, fréquence par fréquence, l'impédance d'entrée de la partie active (le profil d'impédance active) qu'il faut synthétiser pour répondre au gabarit de réponse objectif.

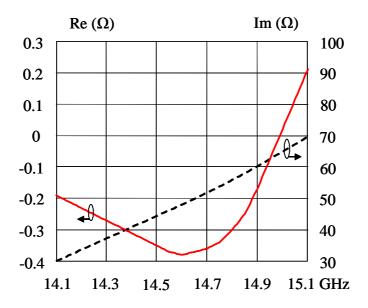

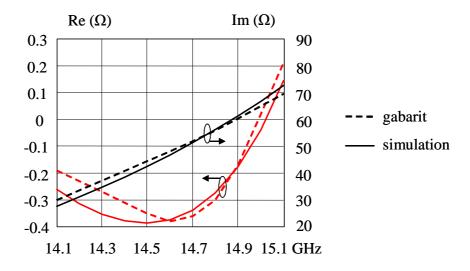

Cette impédance d'entrée, ainsi que la réponse globale du filtre, sont présentées respectivement sur les figures II-10 et II-11.

Figure II-10 Gabarit de l'impédance active

Figure II-11 Réponse du filtre global

Le profil d'impédance active à synthétiser (figure II-10) correspond à une résistance négative avec une partie imaginaire dont la réponse est globalement équivalente à une inductance.

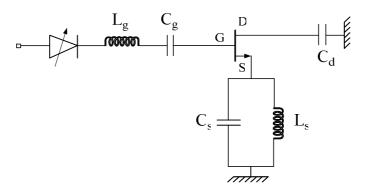

#### III.3 CONCEPTION DE LA PARTIE ACTIVE

Dans un premier temps, il faut déterminer une structure capable de réaliser l'impédance active requise. Le circuit retenu est construit selon une topologie de résistance négative qui a fait l'objet d'une étude dans [39] et [40] et dont l'impédance d'entrée est de même forme que le profil d'impédance présenté sur la figure II-10. Nous rajoutons une inductance en entrée du montage afin d'obtenir une partie imaginaire positive et une diode varactor de manière à pouvoir modifier la valeur de cette partie imaginaire pour ajustements ultérieurs (figure II-12).

Figure II-12

Topologie du circuit actif

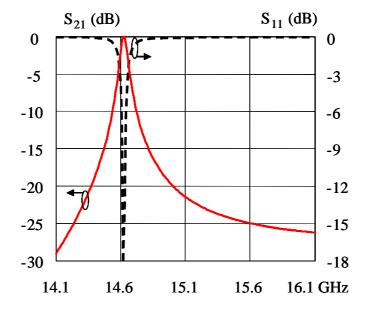

Les premières simulations de ce circuit, sans tenir compte des éléments parasites comme les lignes de connexion, sont présentées sur la figure II-13.

Figure II-13

Impédance présentée par le circuit actif sélectionné

Ces résultats montrent que ce circuit simple permet de satisfaire aux spécifications requises.

### III.4 REALISATION DU FILTRE ACTIF

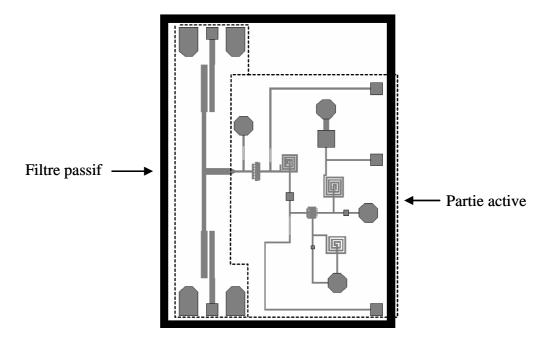

Les parties active et passive sont maintenant assemblées en tenant compte des éléments parasites de connexion. Le dessin du masque (layout) du filtre actif est présenté sur la figure II-14.

Figure II-14

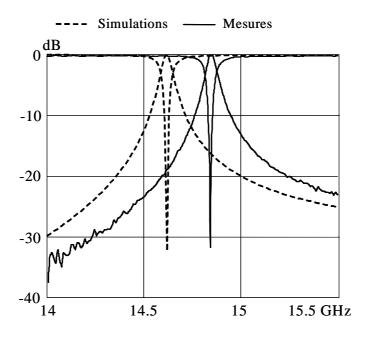

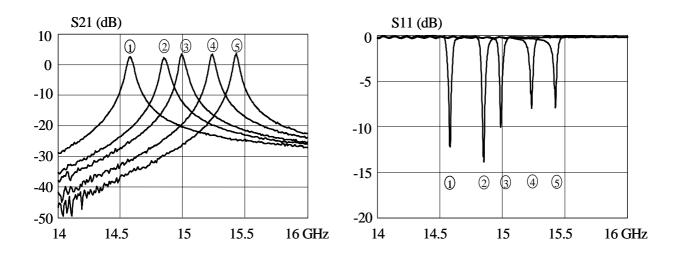

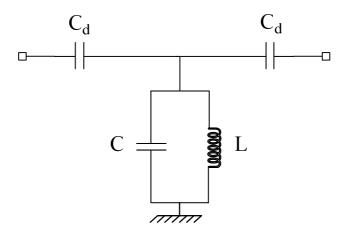

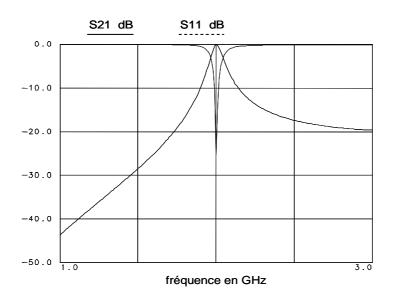

Masque du filtre actif